部分可重配置會涉及到將配置數據下載到正在運行的系統中。 盡管在芯片和比特流中內置了一些保護措施,比如器件ID,從而確保識別正確的部分,但是作為用戶設計的一部分,仍有一些技術需要理解和實現。 設計人員應遵循這些建議,以確保部分可重配置的安全和可預測性。

? 在進行重新配置操作之前需要對可重配置分區(RP)內的一些活動程序進行關閉,如果可重配置功能沒有進行完整的傳輸或者沒有對最近的請求作出回復,那么整個系統可能會掛起。

解決方案:在你的設計中務必確保在重新配置之前RP分區內所有活動都已經完成,在設計中對每個分區內都實現請求—通知握手操作,這樣系統就不會掛起,信息也不會丟失。

? 對RP分區進行隔離,這樣任何動態的變化都不會對靜態設計產生任何負面的影響,目前還無法預測RP分區在進行動態配置時會有哪些行為方式,如果一些浮動信號從RP分區“逃出去”,那么一些虛假事件就會對靜態設計產生負面影響。

解決方案:最佳的操作方案就是斷開該分區與靜態設計之間的連接直到可重配置操作完成,PR Controller IP通過選通任何接口端口可以用于隔離RP分區,或者自定義邏輯模塊(2選1多路復用器,具有復位或啟動門控的寄存器等)都可以實現這個功能。

? 如果部分比特流文件必須傳遞給遠程系統,那么在傳送過程中可能會造成損壞,如果將損壞的部分比特流發送到配置引擎中,那么靜態設計部分可能會受影響,在比特流末尾進行標準的CRC檢查并不夠完整,因為所有的配置數據在檢查操作之前已經發送完畢。

解決方案:部分比特流文件的每一幀數據都可以使用CRC進行檢測,因此壞幀在可以加載到配置存儲器之前都可以被檢測到,然后我們可以采取糾正或者回退操作。在每個路由設計檢查點都啟用CRC檢查,開啟命令如下:set_property bitstream.general.perFrameCRC yes [current_design]

然而最關鍵的細節就是絕對確保傳送給FPGA或者SoC的部分比特流能夠與靜態設計相互兼容,這樣才能夠配置到器件中,部分可重配置設計流程需要對靜態實現部分進行鎖定,并且所有可重配置模塊都要在此上下文中實現,如果靜態設計改變了,那么所有使用該靜態設計創建的部分比特流都將失效并且需要重新編譯,因為部分比特流內容的很多方面都已經發生了變化——時鐘、分區管腳、靜態路由等都可能是不同的了,這種保守的方法具有一定的靈活性,提升整體設計的性能,但是必須要個遵循主從的關系。

設計者必須實現某種版本檢查方案來確保只有匹配的比特流才能夠被加載到靜態設計系統中,實現方式有很多種,片上/片下、硬件/軟件等。不管哪種方式都將會在部分比特流文件發送至配置端口前根據靜態設計部分的版本來檢查比特流文件的版本。

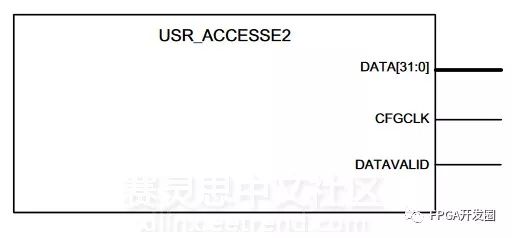

在FPGA結構中執行這種檢查的一個便利的方式就是使用USR_ACCESS模塊,該組件在專用配置空間中保存一個32位的寄存器,但是可以通過FPGA訪問,只需要將USR_ACCESSE2模塊在你的RTL設計中進行實例化就可以獲得訪問權限,通過連接32位數據總線即可使用此功能。

這個常量寄存器的值是通過下面命令來設置的:set_property BITSTREAM.CONFIG.USR_ACCESS 0x<8-digit-hex>|TIMESTAMP [current_design]

盡管我們可以使用TIMESTAMP選項,通過加載所有比特位文件信息可能更容易創建自定義的寄存器值,TIMESTAMP的值是即時計算的,所以在應用到部分比特文件時需要讀取Vivado工具為靜態設計部分計算的數值。

一旦設計連接了此元素,你可以使用32位的值來匹配部分比特流文件,這個值保存在上文給定屬性的完整比特流文件中,因為它是在器件初始化配置時編寫的,然而部分比特流文件并不包含此值,因為它不會去重新編程USR_ACCESS寄存器,你需要對每個部分比特流添加自定義數據頭信息,這個數據頭應該包含這個值用于靜態設計部分的版本檢查,最簡單的比較匹配就是設置錯誤標志,如果檢測到失敗這是必需的,一旦檢測到不匹配系統需要確定下一步該怎么操作。

當創建新版本的靜態設計時你需要更新USR_ACCESS的值,不僅包括靜態設計部分還包括根據此靜態設計版本相匹配的一系列部分比特流文件,USR_ACCESS模塊具有兩個特性使其成為該用法的理想選擇:

1. 由于它是配置應用方面專用的模塊,因此它不使用任何標準的CLB或者BRAM資源,為你的設計留出更多可用的資源。

2. 由于該值是通過屬性來設置的,因此可以在所有布局和布線完成后再插入該值,以后再重新插入新值時也不再需要進行重新綜合或者實現。

在寫入完整的比特流數據前只需要將新的 BITSTREAM.CONFIG.USR_ACCESS 應用于完整設計版本檢查,任何較舊版本的部分比特流文件都會在進行版本檢查時被拒絕,確保與硬件的匹配。

想了解更多關于USR_ACCESS的信息可以查看XAPP1231文檔。

總結在部分可重配置設計中應用版本識別檢查和其他安全機制從而可以確保安全可靠的工作環境。

我們希望聽到您的意見!參與部分可重配置問卷調查(請點擊“閱讀原文”在線參與)對這個解決方案提供反饋,幫助我們改進的更好。

作者簡介David Dye是分層設計流程的高級產品營銷經理,他的職責包括產品規劃、部分可重配置的市場營銷,串聯配置和相關設計流程等,比如模塊分析和團隊設計。他在Xilinx擁有超過20年的從業經驗,并在其任職期間支持各種ISE和Vivado設計工具的開發,從綜合、實現到調試。David擁有卡內基梅隆大學的電氣工程學位。

-

FPGA芯片

+關注

關注

3文章

248瀏覽量

40207

原文標題:部分可重配置設計流程 — 部分比特流版本檢查

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

鴻蒙原生應用元服務-訪問控制(權限)開發概念和使用基本原則

鴻蒙原生應用元服務-訪問控制(權限)開發校驗環節

鴻蒙原生應用元服務-訪問控制(權限)開發應用權限列表三

鴻蒙原生應用元服務開發-位置服務申請權限

P2P權限委托與訪問控制模型

基于規則引擎的實例級權限控制研究

Linux改變文件或目錄的訪問權限命令

微軟宣布開放其文本語音轉換 AI 的訪問權限

應用太多無從下手,企業如何破解訪問權限管理難題?

linux文件訪問權限怎么設置

如何解決C語言中的“訪問權限沖突”異常?C語言引發異常原因分析

鴻蒙開發Ability Kit程序訪問控制:申請使用受限權限

FPGA開發進行實例化,如何獲得訪問權限

FPGA開發進行實例化,如何獲得訪問權限

評論