摘要:本系統(tǒng)由FPGA、串口屏、DAC模塊和AD831組成。FPGA通過(guò)調(diào)用宏功能模塊NCO,按照輸入時(shí)鐘50MHz,產(chǎn)生相應(yīng)頻率正弦信號(hào)輸出,共產(chǎn)生兩路,一路為調(diào)制信號(hào),另一路為載波信號(hào)。根據(jù)AM調(diào)制的原理,調(diào)用宏功能模塊LPM_MULT將調(diào)制信號(hào)和載波信號(hào)的數(shù)值相乘,得到AM調(diào)制信號(hào),并能夠?qū)φ{(diào)制度進(jìn)行調(diào)節(jié)。并系統(tǒng)采用AD831完成對(duì)于AM調(diào)制信號(hào)的上變頻,本振信號(hào)由信號(hào)發(fā)生器產(chǎn)生。

1.設(shè)計(jì)方案工作原理

1.1系統(tǒng)方案描述

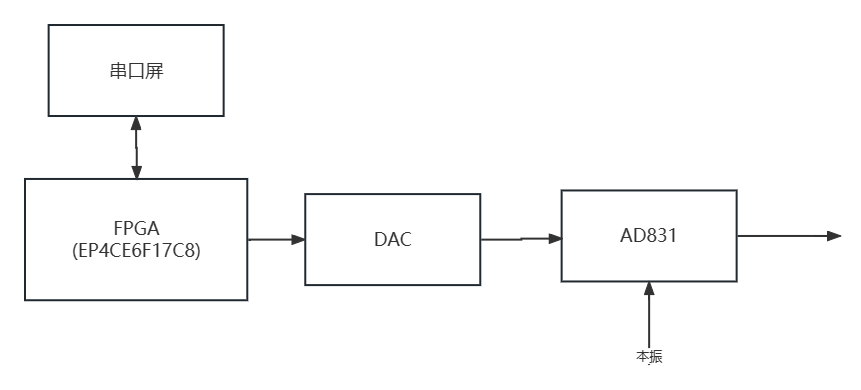

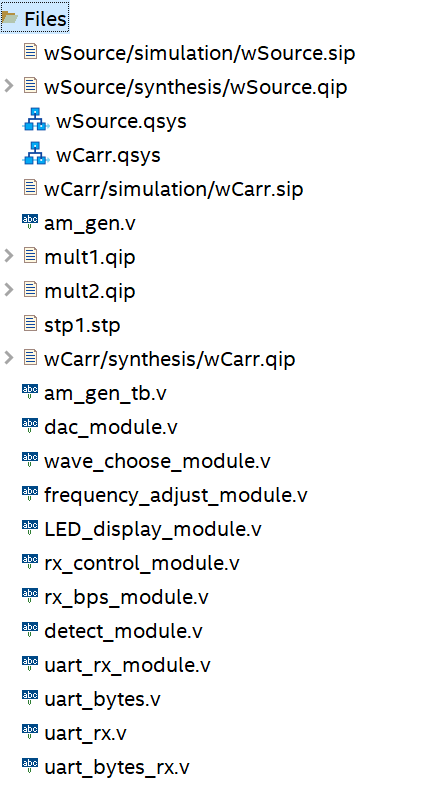

本系統(tǒng)框圖如圖1.1所示,FPGA通過(guò)調(diào)用宏功能模塊NCO,按照輸入時(shí)鐘50MHz,產(chǎn)生相應(yīng)頻率的調(diào)制信號(hào)、載波信號(hào)和AM調(diào)制信號(hào)數(shù)值,DAC模塊根據(jù)控制字產(chǎn)生相應(yīng)頻率和幅值的信號(hào)。輸出的AM調(diào)制信號(hào)接入AD831與高頻率信號(hào)進(jìn)行混頻最終輸出高頻信號(hào)。串口屏通過(guò)串口與FPGA進(jìn)行通信可以在一定范圍內(nèi)對(duì)調(diào)制信號(hào)的頻率、載波頻率和調(diào)制度進(jìn)行調(diào)節(jié)。

圖1.1 系統(tǒng)框圖

1.2方案比較與選擇

1.2.1 FPGA

方案1:使用高云的GW1NSR-LV4C型號(hào)的FPGA,其具有Cortex-M3的硬核處理器,共有4608個(gè)邏輯單元、3456個(gè)寄存器,乘法器的參數(shù)為16,Block SRAM有180K,用戶閃存為256K,并有2個(gè)鎖相環(huán)PLL,4個(gè)I/O Bank,用戶I/O數(shù)為44。

方案2:使用EP4CE6系列的Cyclone IV EP4CE6F17C8N型號(hào)FPGA,其含256個(gè)管腳,6272個(gè)邏輯單元,采用BGA封裝。采用低成本、低功耗的FPGA架構(gòu)、6K到150K的邏輯單元、高達(dá)6.3Mb的嵌入式存儲(chǔ)器、高達(dá)360個(gè)18×18乘法器,實(shí)現(xiàn)DSP處理密集型應(yīng)用、協(xié)議橋接應(yīng)用,實(shí)現(xiàn)小于1.5W的總功耗。

綜合以上考慮,考慮到AM調(diào)制系統(tǒng)的需求和各項(xiàng)頻率的需求,在盡、可能減少功耗的前提下,選擇方案2。

1.2.2 DAC電路方案

方案1:使用ACM9767高速DAC模塊,其為一款高性能高速雙通道DAC模塊,本模塊具有單電源5V供電輸入,雙通道數(shù)字轉(zhuǎn)模擬信號(hào)輸出,每個(gè)通道數(shù)據(jù)分辨率為14位,輸出電壓范圍為正負(fù)5V,且轉(zhuǎn)換速率高達(dá)125Msps。

方案2:使用與FPGA開(kāi)發(fā)板的AD和DA集成板,其采用THS5651A電路,能夠產(chǎn)生規(guī)定頻率的波形,并且穩(wěn)定輸出。具有精度高、電路簡(jiǎn)單、價(jià)格便宜的特點(diǎn)。

綜合上述考慮,考慮到電路的復(fù)雜程度、結(jié)果的精確程度以及方案的價(jià)格等方面,選擇方案2。

1.2.3 人機(jī)交互方案

方案1:使用數(shù)碼管和按鍵作為人機(jī)交互,數(shù)碼管顯示調(diào)節(jié)的模式(調(diào)制信號(hào)、載波信號(hào)和調(diào)制深度),按鍵調(diào)節(jié)頻率和調(diào)制度。

方案2:使用串口屏制作人機(jī)交換界面,制作一個(gè)主界面和三個(gè)子界面,三個(gè)子界面分別調(diào)節(jié)調(diào)制信號(hào)的頻率、載波信號(hào)的頻率和調(diào)制深度。

方案3:使用數(shù)碼管和矩陣按鍵,數(shù)碼管作為調(diào)節(jié)模式的顯示,矩陣按鍵作為輸入,輸入相應(yīng)的頻率和調(diào)制深度。

綜合以上考慮,為了方便快捷的調(diào)節(jié)頻率、調(diào)制度,我們最終選擇方案2。

2.核心部件電路設(shè)計(jì)

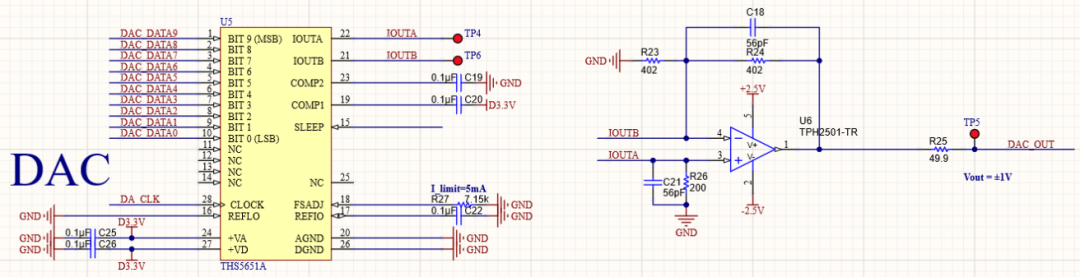

2.1 DAC電路

DAC電路,即數(shù)模轉(zhuǎn)換電路。其采用THS5651A電路,完成數(shù)模轉(zhuǎn)換。其通過(guò)R27和內(nèi)部VREF設(shè)定的DAC輸出差分電流是IOUTA = 0mA-5mA,IOUTB = 5mA-0mA(這里IOUTA和IOUTB是差分對(duì)),具體的輸出電流值由輸入DAC的碼值DA_Data[9:0]確定。IOUTA和IOUTB通過(guò)外部運(yùn)放電路轉(zhuǎn)化為單端電壓。

DAC電路如下圖2.1所示。

圖2.1 DAC電路圖

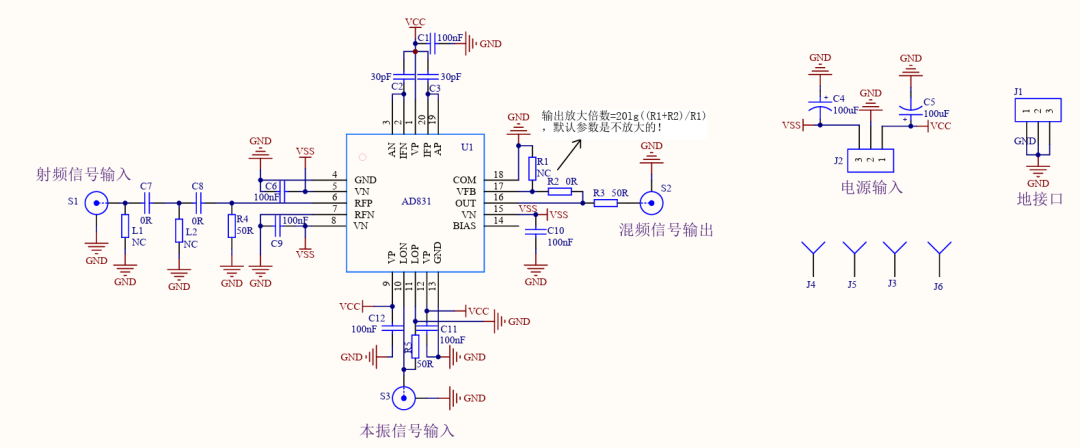

2.2 AD831混頻電路

AD831混頻電路起到的是混頻作用,將對(duì)FPGA產(chǎn)生的AM調(diào)制信號(hào)完成上變頻。其能夠完成將信號(hào)頻率由一個(gè)量值轉(zhuǎn)為另一個(gè)量值,常常用于產(chǎn)生中頻信號(hào)。AD831由混頻器、限幅放大器、低噪聲輸出放大器和偏置電路等組成,是一款集成的混頻器,其本人和射頻輸入均可達(dá)到500MHz,中頻輸出方式由兩種:差分電流輸出和單端電壓輸出,在采用差分電流輸出時(shí),輸出頻率可達(dá)250MHz;在采用單端電壓輸出時(shí),輸出頻率可達(dá)200MHz。

AD831電路如下圖2.2所示。

圖2.2 AD831電路圖

3.系統(tǒng)軟件設(shè)計(jì)分析

3.1主要模塊程序設(shè)計(jì)

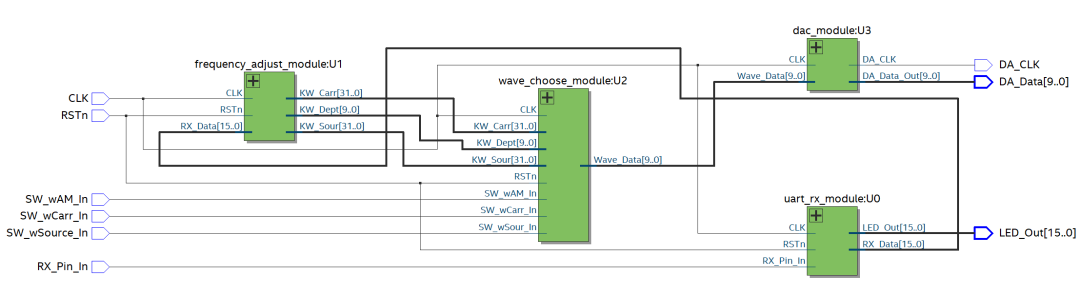

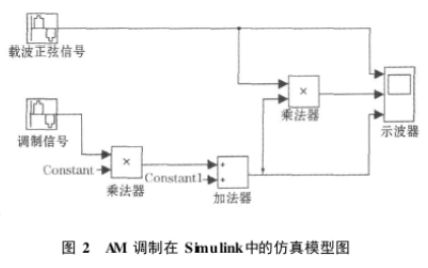

FPGA程序主要由四部分組成,分別為U0-串口接收模塊、U1-頻率調(diào)節(jié)模塊、U3-波形選擇模塊和U4-DAC轉(zhuǎn)換模塊。U0-串口接收模塊用于接收來(lái)自串口屏發(fā)出的頻率和調(diào)制深度信息,然后將接收的信息傳送到U1-頻率調(diào)節(jié)模塊,U1-頻率調(diào)節(jié)模塊進(jìn)行處理生成三個(gè)相對(duì)應(yīng)的控制字轉(zhuǎn)送給U3-波形選擇模塊,同時(shí)U3-波形選擇模塊根據(jù)撥動(dòng)按鍵來(lái)選擇輸出的波形,然后將波形產(chǎn)生數(shù)據(jù)傳送給U4-DAC轉(zhuǎn)換模塊。

AM調(diào)制系統(tǒng)RTL圖如圖3.1所示。

圖3.1 系統(tǒng)RTL圖

3.2關(guān)鍵模塊程序清單

關(guān)鍵模塊的程序原文件列表主要包含串口、波形選擇、頻率調(diào)節(jié)、DAC轉(zhuǎn)換和頂層文件。

模塊程序清單如圖3.2所示。

圖3.2 程序清單圖

4.競(jìng)賽工作環(huán)境條件

4.1設(shè)計(jì)分析軟件環(huán)境

Windows 10;Quartus Ⅱ;Modelsim。

4.2儀器設(shè)備硬件平臺(tái)

示波器(RIGOL:DS2022A-EDU);信號(hào)發(fā)生器(RIGOL:DG4102);直流電源(RIGOL:DP832)。

4.3測(cè)試條件

工作電源電壓:±12V;

溫度:室溫;

氣壓:標(biāo)壓。

5.作品成效總結(jié)分析

5.1系統(tǒng)測(cè)試性能指標(biāo)

調(diào)制信號(hào)測(cè)試方案:輸出信號(hào)為正弦波,頻率為1KHz,觀察示波器結(jié)果。

載波信號(hào)測(cè)試方案:輸出信號(hào)為正弦波,頻率為5MHz,觀察示波器結(jié)果。

AM調(diào)制測(cè)試方案:輸出信號(hào)為AM調(diào)制信號(hào),觀察示波器結(jié)果與波形。然后接入AD831模塊射頻輸入端,并使用信號(hào)發(fā)生器產(chǎn)生25 MHz,100mv Vpp的正弦信號(hào),接入AD831模塊本振輸入端,混頻后得到30 MHz,并使用示波器的MATH功能的FFT來(lái)觀察頻譜。

自由設(shè)置調(diào)制信號(hào)測(cè)試方案:使用串口屏調(diào)節(jié)調(diào)制信號(hào)頻率,觀察示波器結(jié)果。

自由設(shè)置載波信號(hào)測(cè)試方案:使用串口屏調(diào)節(jié)載波信號(hào)頻率,觀察示波器結(jié)果。

調(diào)制度測(cè)試方案:使用串口屏調(diào)節(jié)調(diào)制深度,觀察示波器結(jié)果,對(duì)其進(jìn)行分析。

5.2成效得失對(duì)比分析

5.2.1 調(diào)制信號(hào)測(cè)試結(jié)果

表5.1 調(diào)制信號(hào)測(cè)試結(jié)果表

| 波形 | 頻率 | 諧波失真度 |

| 正弦波 | 1KHz | 1.42% |

5.2.2 載波信號(hào)測(cè)試結(jié)果

表5.2 載波信號(hào)測(cè)試結(jié)果表

| 波形 | 頻率 | 諧波失真度 |

| 正弦波 | 5MHz | 1.31% |

5.2.3 AM調(diào)制測(cè)試結(jié)果

表5.3 AM調(diào)制測(cè)試結(jié)果表

| 是否調(diào)制 | 調(diào)制深度 | 是否上變頻 | 上變頻頻率 |

| 是 | 0.5 | 是 | 30.02MHz |

5.2.3 自由設(shè)置調(diào)制信號(hào)參數(shù)測(cè)試結(jié)果

使用串口屏進(jìn)入調(diào)制信號(hào)參數(shù)測(cè)試界面,調(diào)節(jié)調(diào)制信號(hào)頻率,觀察示波器結(jié)構(gòu)。其頻率范圍為1KHz-10KHz,分辨率為0.01KHz.以下為部分測(cè)試結(jié)果。

表5.4 調(diào)制信號(hào)頻率測(cè)試結(jié)果表

| 理論信號(hào) | 實(shí)際信號(hào) |

| 1.00KHz | 1.001KHz |

| 1.05KHz | 1.051KHz |

| 1.50KHz | 1.498KHz |

| 2.00KHz | 2.008KHz |

| 3.50KHz | 3.499KHz |

| 5.00KHz | 5.002KHz |

| 10.00KHz | 9.997KHz |

5.2.4 自由設(shè)置載波信號(hào)參數(shù)測(cè)試結(jié)果

使用串口屏進(jìn)入載波信號(hào)頻率設(shè)置界面,調(diào)節(jié)載波信號(hào)頻率,觀察示波器結(jié)果。其范圍為1M-10MHz,分辨率為0.01MHz。以下為部分測(cè)試結(jié)果。

表5.5 載波信號(hào)頻率測(cè)試結(jié)果表

| 理論信號(hào) | 實(shí)際信號(hào) |

| 1.00MHz | 1.002MHz |

| 2.00MHz | 2.006MHz |

| 3.00MHz | 2.988MHz |

| 4.00MHz | 3.989MHz |

| 5.00MHz | 5.008MHz |

| 6.50MHz | 6.503MHz |

| 7.70MHz | 7.705MHz |

| 8.80MHz | 8.796MHz |

| 10.00MHz | 10.004MHz |

5.2.4 自由設(shè)置調(diào)制深度測(cè)試結(jié)果

使用串口屏進(jìn)入調(diào)制深度設(shè)置界面,調(diào)節(jié)調(diào)制深度,觀察示波器結(jié)果。步進(jìn)為0.1。

以下為部分測(cè)試結(jié)果。

表5.6 調(diào)制深度測(cè)試結(jié)果表

| 理論值 | 實(shí)際值 |

| 0 | 0.001 |

| 0.1 | 0.107 |

| 0.2 | 0.180 |

| 0.3 | 0.280 |

| 0.4 | 0.390 |

| 0.5 | 0.450 |

| 0.6 | 0.580 |

| 0.7 | 0.670 |

| 0.8 | 0.790 |

| 0.9 | 0.875 |

| 1 | 0.998 |

5.3創(chuàng)新特色總結(jié)

系統(tǒng)電路系統(tǒng)簡(jiǎn)單,輸出波形美觀。結(jié)構(gòu)清晰分明,采用正負(fù)12V供電,對(duì)電源要求低;此外,系統(tǒng)還具有以下3點(diǎn)優(yōu)點(diǎn):

利用宏功能模塊NCO和LPM_MULT實(shí)現(xiàn)調(diào)制信號(hào)和載波信號(hào)以及AM調(diào)制信號(hào)的產(chǎn)生,精度高,速度快,遠(yuǎn)遠(yuǎn)超過(guò)題目所設(shè)定的要求。

具有混頻的功能,精度高,可以將FPGA產(chǎn)生的射頻信號(hào)進(jìn)行上變頻。

系統(tǒng)可以通過(guò)串口屏對(duì)系統(tǒng)進(jìn)行交互和控制。系統(tǒng)可以對(duì)頻率進(jìn)行粗略調(diào)節(jié)和精細(xì)調(diào)節(jié),可以實(shí)現(xiàn)超越題目要求的頻率輸出。

綜上,系統(tǒng)完全實(shí)現(xiàn)了題目的要求,精度較高,并且在功能上加以拓展。性能十分優(yōu)良。效果遠(yuǎn)超題目要求。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21946瀏覽量

613550 -

dac

+關(guān)注

關(guān)注

43文章

2369瀏覽量

192951 -

調(diào)制信號(hào)

+關(guān)注

關(guān)注

0文章

68瀏覽量

14995 -

串口屏

+關(guān)注

關(guān)注

8文章

578瀏覽量

38073

原文標(biāo)題:基于FPGA的AM調(diào)制系統(tǒng)

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

基于FPGA的幀同步系統(tǒng)設(shè)計(jì)方案

什么是調(diào)制?為什么進(jìn)行調(diào)制?AM調(diào)制是什么?#調(diào)制 #解調(diào) #信號(hào) #AM調(diào)制 #數(shù)字信號(hào)處理

從ASIC到FPGA的轉(zhuǎn)換系統(tǒng)時(shí)鐘設(shè)計(jì)方案

FPGA設(shè)計(jì)大賽設(shè)計(jì)方案提交規(guī)則和截止時(shí)間須知

分享一種不錯(cuò)的基于FPGA和USB的通用CCD采集系統(tǒng)設(shè)計(jì)方案

分享一種基于Actel Flash FPGA的高可靠設(shè)計(jì)方案

基于FPGA的QAM調(diào)制器系統(tǒng)實(shí)現(xiàn)

基于FPGA的視頻傳輸流發(fā)送系統(tǒng)設(shè)計(jì)方案

多種EDA工具的FPGA設(shè)計(jì)方案

QAM調(diào)制系統(tǒng)的FPGA設(shè)計(jì)與仿真

如何使用FPGA實(shí)現(xiàn)數(shù)字AM調(diào)制的設(shè)計(jì)

基于FPGA的AM調(diào)制系統(tǒng)設(shè)計(jì)方案

基于FPGA的AM調(diào)制系統(tǒng)設(shè)計(jì)方案

評(píng)論