在高速數字電路和射頻系統中,高頻晶振作為關鍵的頻率源,其信號完整性直接影響整個系統的性能。隨著電子技術的飛速發展,晶振的工作頻率不斷提高,電磁干擾(EMI)與串擾問題日益凸顯,成為制約系統可靠性和穩定性的重要因素。

**高頻晶振的信號完整性挑戰

(一)EMI產生機理

高頻晶振在工作時,會產生豐富的諧波成分,這些諧波通過電磁輻射和傳導耦合的方式傳播到周圍電路,形成EMI。晶振的封裝寄生參數,如引腳電感和電容,會加劇高頻信號的反射和輻射。此外,晶振內部的石英晶體在振蕩過程中會產生機械振動,與電路中的寄生參數相互作用,形成電磁輻射源。同時,電源噪聲和地平面噪聲也會通過晶振的供電引腳和接地引腳耦合到晶振電路,導致晶振輸出信號的相位噪聲增加,進一步惡化EMI性能。

**(二)串擾產生機理

串擾是指相鄰信號走線之間由于電磁耦合而產生的干擾現象。在高頻晶振電路中,晶振的輸出信號走線、時鐘分配網絡以及周圍的高速數字信號走線容易產生串擾。當兩條走線平行敷設且距離較近時,它們之間的互感和互容會導致信號能量的相互耦合,從而在受害走線上產生串擾噪聲。串擾不僅會影響晶振輸出信號的質量,還可能導致系統時鐘同步錯誤,引發數據傳輸錯誤等問題。

抑制EMI的方法

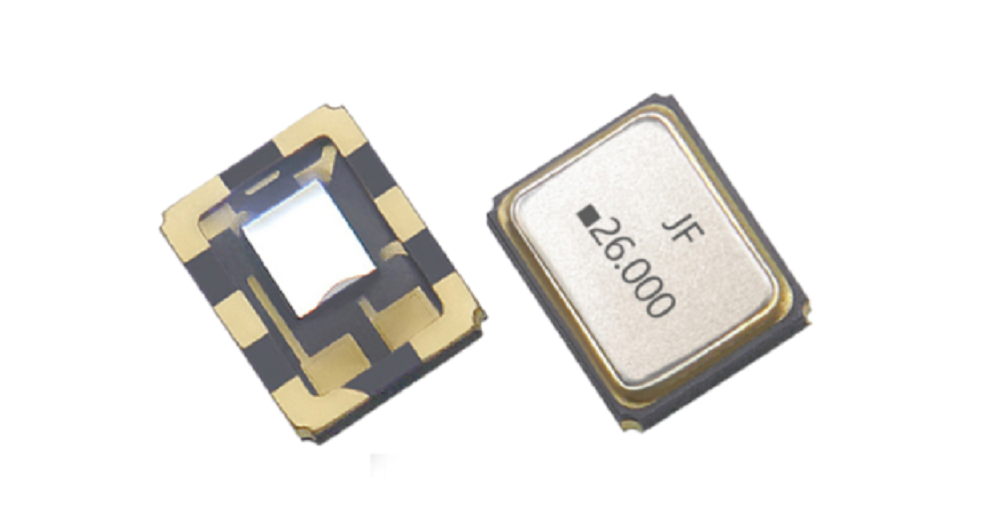

**(一)晶振選型與布局

選擇低EMI的高頻晶振是抑制EMI的首要步驟。優先選用表面貼裝(SMD)封裝的晶振,其引腳電感和寄生電容較小,有利于減少電磁輻射。同時,關注晶振的頻率穩定性和相位噪聲指標,低相位噪聲的晶振能夠減少諧波成分的產生。在PCB布局時,將晶振放置在靠近需要時鐘信號的芯片附近,盡量縮短晶振輸出信號的走線長度,減少走線的輻射面積。晶振應遠離高速數字信號走線、射頻電路和電源模塊,避免受到這些區域的電磁干擾。

(二)PCB設計優化

- 電源與地平面設計 :為晶振提供穩定的電源是抑制EMI的關鍵。使用獨立的電源層和地平面為晶振供電,避免與其他電路共享電源和地平面,減少電源噪聲和地平面噪聲的耦合。在晶振的電源引腳上并聯一個高頻去耦電容,通常為0.1μF的陶瓷電容,以濾除電源中的高頻噪聲。去耦電容應盡量靠近晶振的電源引腳,縮短連接走線的長度,提高去耦效果。

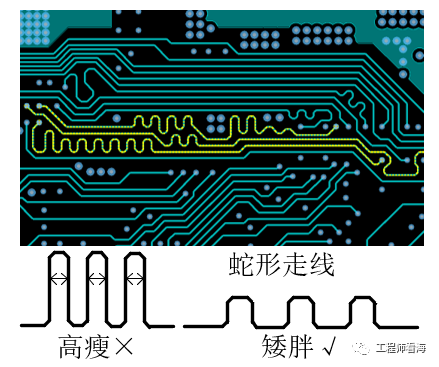

- 走線設計 :晶振的輸出信號走線應采用特性阻抗控制的傳輸線,如微帶線或帶狀線,確保信號的傳輸質量。走線寬度應根據傳輸速率和特性阻抗要求進行設計,避免走線過細或過寬導致的信號反射和輻射增加。同時,走線應盡量避免直角轉彎和分支,減少信號的反射和電磁輻射。對于差分晶振輸出信號,應采用差分走線設計,保持兩條走線的長度相等、間距一致,提高共模抑制比,減少EMI輻射。

**(三)接地處理

良好的接地是抑制EMI的重要措施。晶振的接地引腳應直接連接到PCB的主地平面,確保接地路徑的低阻抗。在晶振下方的地平面上鋪設連續的銅箔,形成一個良好的接地平面,減少晶振的電磁輻射。對于多層PCB,可將晶振放置在接地平面上方的信號層,利用接地平面作為屏蔽層,抑制晶振的電磁輻射。同時,注意其他電路的接地設計,避免不同接地系統之間的噪聲耦合。

**(四)屏蔽與濾波

對于EMI輻射較強的高頻晶振,可采用金屬屏蔽罩對晶振進行屏蔽,將晶振的電磁輻射限制在屏蔽罩內部,減少對周圍電路的干擾。屏蔽罩應良好接地,確保屏蔽效果。此外,在晶振的輸出信號線上添加EMI濾波器,如共模電感、LC濾波器等,濾除高頻噪聲成分,改善信號的頻譜特性。濾波器應根據晶振的工作頻率和噪聲特性進行選擇和設計,確保在有效抑制噪聲的同時,不影響晶振信號的正常傳輸。

**抑制串擾的方法

**(一)布局優化

在PCB布局時,合理規劃晶振電路與周圍信號走線的位置,避免晶振輸出信號走線與高速數字信號走線、射頻信號走線平行敷設。增加晶振走線與其他走線之間的間距,通常要求間距大于3倍的走線寬度,以減少互感和互容耦合。對于無法避免平行敷設的走線,可在兩條走線之間設置接地隔離帶,降低串擾噪聲。同時,將晶振的時鐘分配網絡盡量集中布置,減少時鐘信號的扇出數量和走線長度,降低串擾的可能性。

**(二)走線設計

采用差分走線設計晶振的輸出信號,利用差分信號的共模抑制特性,減少串擾對信號的影響。差分走線應保持嚴格的等長和等間距,避免出現長度偏差和間距變化,確保差分信號的相位一致性。對于單端晶振信號走線,可采用加粗走線、增加走線與地平面的耦合等方式,提高走線的抗串擾能力。此外,在走線周圍鋪設接地保護線,形成一個屏蔽層,減少外界干擾對晶振信號的影響。

**(三)端接與匹配

在晶振信號的接收端和發送端進行端接匹配,減少信號的反射和駐波,降低串擾噪聲。對于源端匹配,可采用串聯電阻的方式,將電阻值設置為傳輸線特性阻抗與晶振輸出阻抗的差值,使信號源的輸出阻抗與傳輸線的特性阻抗相匹配。對于終端匹配,可采用并聯電阻或RC匹配網絡的方式,使接收端的輸入阻抗與傳輸線的特性阻抗相匹配。端接匹配不僅能夠改善信號的完整性,還能減少串擾對相鄰走線的影響。

**(四)分層與隔離

在多層PCB設計中,合理分配信號層、電源層和地平面,將晶振電路與其他高頻電路和高速數字電路分布在不同的信號層,利用電源層和地平面作為隔離層,減少層間串擾。晶振信號層應與其他信號層之間保持足夠的層間距,避免層間電磁耦合。同時,對于關鍵的晶振走線,可將其布置在內層信號層,利用外層的電源層和地平面進行屏蔽,提高抗串擾能力。

**實驗驗證與案例分析

**(一)實驗平臺搭建

為了驗證上述抑制方法的有效性,搭建了一個高頻晶振實驗平臺,包括高頻晶振模塊、PCB測試板、頻譜分析儀、示波器等設備。晶振選用一款工作頻率為100MHz的SMD封裝晶振,PCB測試板采用四層板設計,包含晶振電路、時鐘分配網絡和高速數字信號電路。

**(二)實驗結果分析

在未采取任何抑制措施的情況下,通過頻譜分析儀測量晶振的EMI輻射,發現其在300MHz~1GHz頻段存在較強的諧波輻射,超過了電磁兼容標準的限值。同時,通過示波器觀察晶振輸出信號和相鄰走線的串擾噪聲,發現串擾噪聲峰值達到了信號幅值的20%,嚴重影響了信號的質量。

在采取了晶振選型優化、PCB布局布線調整、接地處理、屏蔽與濾波等抑制措施后,再次測量EMI輻射,發現諧波輻射強度顯著降低,在300MHz~1GHz頻段的輻射值低于電磁兼容標準限值。同時,串擾噪聲峰值降低到信號幅值的5%以下,晶振輸出信號的質量得到明顯改善。

**(三)案例分析

以某高速數字系統為例,該系統采用了一款200MHz的高頻晶振作為時鐘源。在系統調試過程中,發現晶振的EMI輻射導致周圍的射頻電路出現接收靈敏度下降的問題,同時串擾噪聲導致數字信號傳輸出現誤碼。通過分析,確定是晶振的布局不合理、走線過長以及接地不良導致的EMI和串擾問題。針對這些問題,重新設計了PCB布局,將晶振靠近主芯片放置,縮短了輸出信號走線長度,優化了電源和地平面設計,并為晶振添加了屏蔽罩和去耦電容。經過整改后,系統的EMI性能和信號完整性得到了顯著提升,射頻電路的接收靈敏度和數字信號的傳輸可靠性恢復正常。

高頻晶振的EMI與串擾問題是影響信號完整性的重要因素,需要從晶振選型、PCB設計、接地處理、屏蔽濾波等多個方面采取綜合抑制措施。通過合理的布局布線、優化的電源地平面設計、有效的接地和屏蔽濾波手段,能夠顯著降低EMI輻射和串擾噪聲,提高高頻晶振的信號完整性。

隨著電子技術的不斷發展,高頻晶振的工作頻率將越來越高,對信號完整性的要求也將更加嚴格。未來,需要進一步研究新型的晶振封裝技術、低EMI材料和先進的PCB設計方法,以應對更高頻率下的信號完整性挑戰。同時,結合仿真工具和自動化設計軟件,實現對高頻晶振電路的電磁兼容性預測和優化設計,提高系統的可靠性和穩定性。

審核編輯 黃宇

-

emi

+關注

關注

53文章

3698瀏覽量

130228 -

晶振

+關注

關注

34文章

3194瀏覽量

69509 -

信號完整性

+關注

關注

68文章

1432瀏覽量

96415

發布評論請先 登錄

常見信號完整性的問題之PCB設計串擾的原因與Altium Designer中的串擾消除技術

高頻晶振的信號完整性挑戰:如何抑制EMI與串擾

高頻晶振的信號完整性挑戰:如何抑制EMI與串擾

評論