隨著高速數(shù)字信號(hào)處理器(DSP)及外圍設(shè)備的普及,電子系統(tǒng)設(shè)計(jì)者面臨日益嚴(yán)峻的電磁干擾(EMI)問(wèn)題。早期研究中,此類(lèi)問(wèn)題常被稱(chēng)作電磁干擾(EMI)或射頻干擾(RFI),而現(xiàn)代工程領(lǐng)域則更精確地采用"電磁兼容性(EMC)"這一概念。EMC包含兩個(gè)核心維度:系統(tǒng)對(duì)外界電磁環(huán)境的干擾強(qiáng)度(發(fā)射)以及自身抗干擾能力(敏感度)。根據(jù)波洛斯準(zhǔn)則,符合以下三要件的DSP系統(tǒng)可視為具備電磁兼容性:

不對(duì)外部系統(tǒng)產(chǎn)生干擾

對(duì)外部電磁發(fā)射具備足夠抗擾度

系統(tǒng)內(nèi)部組件間無(wú)相互干擾

電磁干擾的成因與傳播機(jī)制

當(dāng)干擾能量導(dǎo)致接收設(shè)備進(jìn)入非正常工作狀態(tài)時(shí),即構(gòu)成有效干擾。干擾傳播可分為直接傳導(dǎo)(通過(guò)導(dǎo)體或公共阻抗耦合)與間接輻射(通過(guò)空間電磁場(chǎng)或串?dāng)_耦合)。典型干擾源涵蓋繼電器、直流電機(jī)、熒光燈等電磁輻射器件,以及電源線、互連電纜等傳導(dǎo)介質(zhì)。值得注意的是,高速數(shù)字電路中的時(shí)鐘電路常成為寬帶噪聲的主要來(lái)源,其產(chǎn)生的諧波失真可達(dá)300MHz,需在設(shè)計(jì)階段予以抑制。復(fù)位線、中斷線等控制信號(hào)線在數(shù)字系統(tǒng)中尤為敏感。

傳導(dǎo)干擾的三重路徑

直接傳導(dǎo)耦合

導(dǎo)線在電磁噪聲環(huán)境中可能成為"天線",吸收并傳導(dǎo)干擾至其他電路。典型案例是電源線引入的傳導(dǎo)干擾,需通過(guò)電源入口處的去耦網(wǎng)絡(luò)進(jìn)行抑制。

公共阻抗耦合

當(dāng)不同電路共享接地路徑時(shí),流經(jīng)公共阻抗的電流會(huì)產(chǎn)生耦合電壓。例如:電路A的接地電流會(huì)通過(guò)公共地阻抗調(diào)制電路B的參考電位,導(dǎo)致噪聲耦合。

輻射耦合(串?dāng)_)

導(dǎo)體中變化的電流產(chǎn)生交變電磁場(chǎng),進(jìn)而在鄰近導(dǎo)體中感應(yīng)出瞬態(tài)電流。此類(lèi)近場(chǎng)耦合效應(yīng)與布線間距、信號(hào)邊沿速率密切相關(guān)。

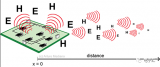

輻射發(fā)射的雙模特性

差模輻射(DM):由信號(hào)回路電流形成,輻射強(qiáng)度與環(huán)路面積成正比

共模輻射(CM):源于系統(tǒng)參考電位的浮動(dòng),通常比差模輻射強(qiáng)度高2-3個(gè)數(shù)量級(jí)

有效抑制CM輻射需通過(guò)優(yōu)化接地設(shè)計(jì),最小化共模電流路徑。

影響EMC的關(guān)鍵設(shè)計(jì)要素

工作電壓

高電源電壓提升信號(hào)擺幅,加劇電磁發(fā)射;低壓供電雖降低發(fā)射但可能影響接收靈敏度。

頻率特性

高頻信號(hào)產(chǎn)生更強(qiáng)的電磁輻射,特別是數(shù)字系統(tǒng)的開(kāi)關(guān)瞬態(tài)(di/dt可達(dá)10^9 A/s)會(huì)激發(fā)寬頻輻射。時(shí)鐘信號(hào)的周期性特征更易形成離散發(fā)射譜線。

接地策略

低頻系統(tǒng)(<1MHz):?jiǎn)吸c(diǎn)接地避免地環(huán)路

高頻系統(tǒng)(>10MHz):多點(diǎn)接地降低地阻抗

混合系統(tǒng):采用"低頻單點(diǎn)+高頻多點(diǎn)"的復(fù)合架構(gòu)

需特別注意將數(shù)字地與模擬地隔離,避免形成耦合路徑。

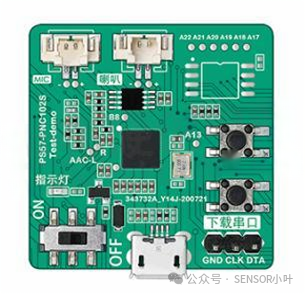

PCB布局

關(guān)鍵措施包括:

控制關(guān)鍵信號(hào)回流路徑

采用多層板構(gòu)建完整參考平面

對(duì)高速信號(hào)實(shí)施阻抗匹配

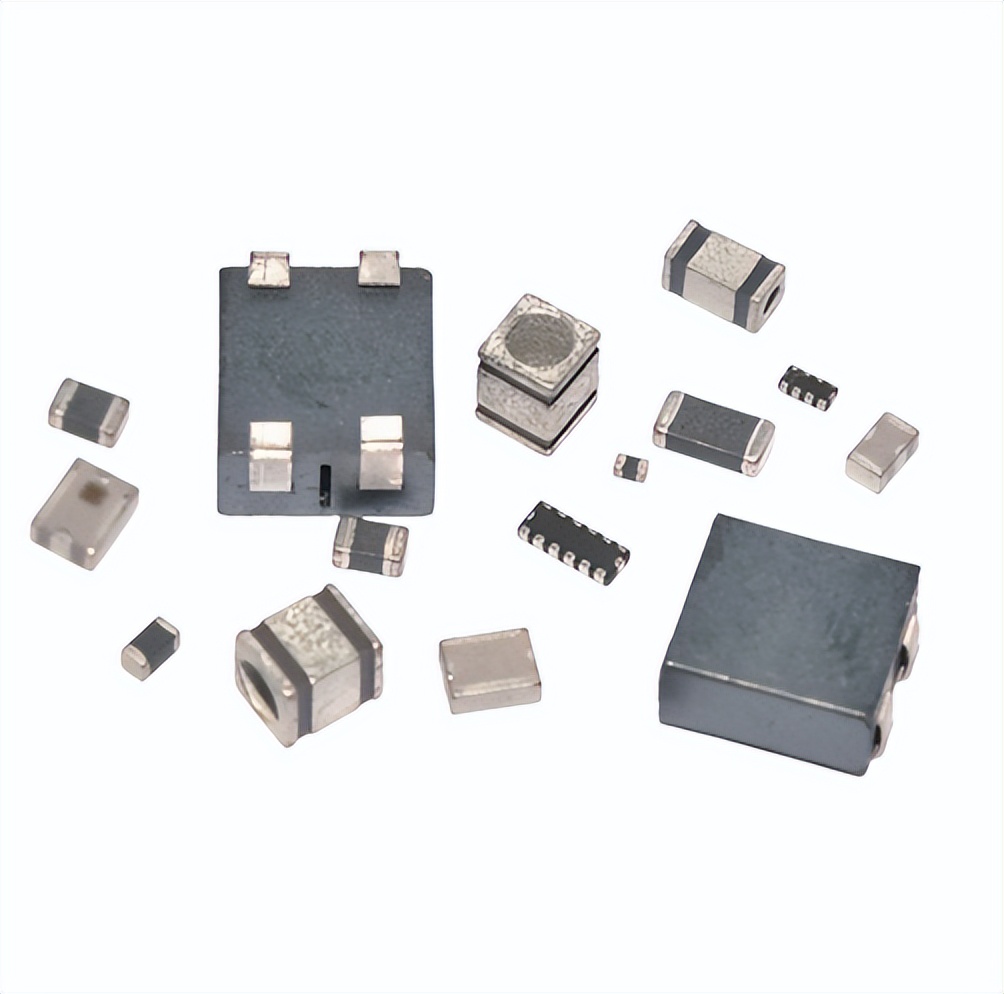

電源完整性

開(kāi)關(guān)瞬態(tài)引起的di/dt噪聲可通過(guò):

優(yōu)化電源分配網(wǎng)絡(luò)(PDN)阻抗

采用π型濾波網(wǎng)絡(luò)抑制高頻噪聲

DSP系統(tǒng)的三重噪聲抑制策略

源頭抑制:優(yōu)化時(shí)鐘電路設(shè)計(jì),采用擴(kuò)頻時(shí)鐘技術(shù)

路徑阻斷:通過(guò)屏蔽、濾波、合理布線切斷傳導(dǎo)/輻射路徑

接收加固:對(duì)敏感電路實(shí)施信號(hào)調(diào)理(如施密特觸發(fā)整形)

DSP降噪芯片降低噪音的技術(shù)

有三種防止干擾的方法: 1、抑制源發(fā)射。2、使耦合路徑盡可能無(wú)效。3、使接收設(shè)備對(duì)傳輸?shù)撵`敏度盡可能小。

-

emc

+關(guān)注

關(guān)注

172文章

4112瀏覽量

185934 -

電磁兼容性

+關(guān)注

關(guān)注

6文章

464瀏覽量

34092 -

DSP系統(tǒng)

+關(guān)注

關(guān)注

0文章

39瀏覽量

12810

發(fā)布評(píng)論請(qǐng)先 登錄

什么是電磁兼容性(EMC)?

解密EMC與EMI:電磁兼容性與電磁干擾?|深圳比創(chuàng)達(dá)電子.

深圳比創(chuàng)達(dá)電子EMC|EMC電磁兼容性:突破電磁干擾,實(shí)現(xiàn)穩(wěn)定通信.

EMC技術(shù)期刊-電工技術(shù)的發(fā)展和電磁兼容性

DSP系統(tǒng)中的電磁兼容探討

如何做好高速DSP系統(tǒng)的電磁兼容性和散熱設(shè)計(jì)?

EMC電磁兼容性行業(yè):技術(shù)前沿與市場(chǎng)挑戰(zhàn)

電磁兼容性(EMC)系統(tǒng)軟件化解決方案:基于三要素的工程實(shí)踐與技術(shù)演進(jìn)

電驅(qū)動(dòng)系統(tǒng)EMC電磁兼容性測(cè)試整改:傳導(dǎo)干擾技術(shù)

【技術(shù)】電磁兼容性(EMC)與高速DSP系統(tǒng)的設(shè)計(jì)挑戰(zhàn)

【技術(shù)】電磁兼容性(EMC)與高速DSP系統(tǒng)的設(shè)計(jì)挑戰(zhàn)

評(píng)論