中國(guó)金融市場(chǎng)已經(jīng)是全球最大的金融市場(chǎng)之一,隨著市場(chǎng)規(guī)模的不斷擴(kuò)大,金融市場(chǎng)的功能發(fā)揮日益明顯,服務(wù)相關(guān)產(chǎn)業(yè)和國(guó)民經(jīng)濟(jì)的能力不斷提高。金融交易系統(tǒng)(例如股票交易系統(tǒng))具有交易時(shí)間相對(duì)集中、交易指令和數(shù)據(jù)密集的特點(diǎn),對(duì)交易系統(tǒng)處理速度具有很高的要求。近年來,資本市場(chǎng)的快速發(fā)展和算法交易技術(shù)(尤其是高頻交易)在全世界范圍內(nèi)的應(yīng)用,使得交易所在低交易延時(shí)領(lǐng)域面臨著巨大的技術(shù)挑戰(zhàn)。

交易所對(duì)于交易系統(tǒng)延時(shí)測(cè)量監(jiān)控需求也越來越迫切,同時(shí)對(duì)于大規(guī)模數(shù)據(jù)密集型計(jì)算的實(shí)時(shí)性要求也越來越高。對(duì)于交易系統(tǒng)及環(huán)節(jié)的高精度延時(shí)測(cè)量,達(dá)到近實(shí)時(shí)的分析性能基本可以準(zhǔn)確快速的監(jiān)測(cè)股票交易系統(tǒng)性能和狀態(tài),但對(duì)于大規(guī)模實(shí)時(shí)交易數(shù)據(jù)分析,則需要達(dá)到更快的處理速度,實(shí)時(shí)性要求更高,直接關(guān)系到交易系統(tǒng)的服務(wù)質(zhì)量(QoS)。傳統(tǒng)的軟件技術(shù)或以軟件為核心的軟硬件加速技術(shù)難以滿足微秒級(jí)實(shí)時(shí)分析和實(shí)時(shí)響應(yīng)的要求,采用FPGA專用硬件結(jié)構(gòu)實(shí)現(xiàn)大規(guī)模數(shù)據(jù)密集型計(jì)算的并行加速稱為提高交易系統(tǒng)服務(wù)質(zhì)量的迫切需求。

針對(duì)金融網(wǎng)絡(luò)數(shù)據(jù)處理的技術(shù)研究而言,國(guó)外已經(jīng)預(yù)言或?qū)崿F(xiàn)了很多相關(guān)硬件加速和并行計(jì)算的FPGA實(shí)現(xiàn),其中Altera公司2008年面向蒙特卡羅算法(QMC)的FPGA加速模型建立,對(duì)價(jià)格衍生證券的實(shí)時(shí)精確估計(jì)判斷做出了很大的促進(jìn)作用。此外,2009年英國(guó)帝國(guó)理工學(xué)院和英國(guó)金融加速解決方案供應(yīng)商Celoxica合作,提出實(shí)現(xiàn)了一種叫“低延遲交易數(shù)據(jù)反饋計(jì)算模型”。針對(duì)現(xiàn)在越來越大的交易市場(chǎng)的變化數(shù)據(jù)(甚至超過gigabit),他們?yōu)橥顿Y者提供了網(wǎng)絡(luò)傳輸數(shù)據(jù)分析的FPGA加速處理方案,利用FGPA的可配置特點(diǎn),可選擇地實(shí)現(xiàn)對(duì)交易數(shù)據(jù)的壓縮,過濾,篩選。其性能優(yōu)越,每秒最多處理高達(dá)3.5M條信息,處理延遲也控制在微秒量級(jí)上。不但激活了投資者的投資熱情,同時(shí)也極大促進(jìn)了金融市場(chǎng)流動(dòng)性。

基于FPGA的硬件以太網(wǎng)協(xié)議跨層解析

在數(shù)據(jù)分析獲取過程中,以太網(wǎng)的協(xié)議解析占據(jù)了很大的時(shí)間比例。如果采用一般的軟件解包方法,時(shí)間一般延遲包括每一網(wǎng)絡(luò)層的解包時(shí)間和中間數(shù)據(jù)的傳輸時(shí)間,時(shí)間延遲可達(dá)毫秒級(jí)甚至更高。考慮到降低整個(gè)系統(tǒng)的數(shù)據(jù)傳輸延遲,進(jìn)而提升處理性能,提出以下兩種解決方案。

使用FPGA集成的可配置IP核。FPGA的IP核基于硬件原理實(shí)現(xiàn),在數(shù)據(jù)傳輸延遲和網(wǎng)絡(luò)數(shù)據(jù)解包能力上都大大優(yōu)于傳統(tǒng)的軟件處理過程,而且極大縮短了開發(fā)周期,其可靠性,可配置性,通用性都相當(dāng)出色。適合在項(xiàng)目的中前期作為數(shù)據(jù)輸入的模擬測(cè)試。但是具體面向此項(xiàng)目IP核也會(huì)有自身的冗余,在MAC層不能進(jìn)行自定義的協(xié)議解析,總的延遲大約在幾十微秒至幾百微秒。

針對(duì)本應(yīng)用設(shè)計(jì)基于跨層解析的以太網(wǎng)數(shù)據(jù)分析模型。由于套利計(jì)算的數(shù)據(jù)源的包格式固定,封裝簡(jiǎn)單,而且屬于旁路數(shù)據(jù),完全可以自行設(shè)計(jì)針對(duì)本應(yīng)用的專用數(shù)據(jù)解析功能部分,方案優(yōu)勢(shì)和創(chuàng)新點(diǎn)在于在MAC層跨層解析數(shù)據(jù)以及包過濾,數(shù)據(jù)接收與解析時(shí)間重疊。采用狀態(tài)機(jī)逐層進(jìn)行包過濾,在有限機(jī)器周期內(nèi)便可獲得需要計(jì)算的數(shù)據(jù),時(shí)間延遲可控制在微秒級(jí)。

基于FPGA的硬件以太網(wǎng)協(xié)議跨層解析能夠降低傳統(tǒng)軟件協(xié)議棧的數(shù)據(jù)包處理固有延遲(可能占據(jù)整個(gè)延遲的80%以上開銷),大大提高數(shù)據(jù)獲取和預(yù)處理效率。

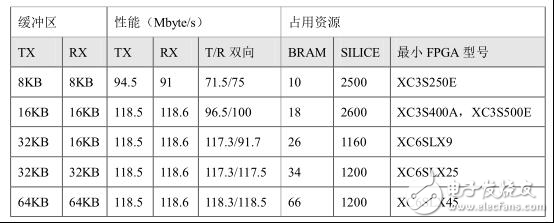

基于 FPGA 的千兆 TCP 硬協(xié)議棧,實(shí)現(xiàn) TCP 與 FIFO 之間的數(shù)據(jù)連接,內(nèi)部集成了千兆以太網(wǎng) MAC 層,ARP 處理,TCP 處理等功能。RGMII 接口,直接連接 PHY 芯片,10/100/1000M 自適應(yīng)。自動(dòng)迅速的 ARP 響應(yīng)。

硬邏輯的 TCP 協(xié)議棧,具有 listen 功能,可接受 1 個(gè) TCP 連接,完整的三次握手建立

連接(syn)、數(shù)據(jù)快速重傳、保活(keepalive)、窗口調(diào)整、被動(dòng)關(guān)閉(fin)等功能。 可設(shè)置 MAC 地址,IP 地址,端口號(hào),超時(shí)時(shí)間,以用于實(shí)時(shí)性高的場(chǎng)合可配置的緩沖區(qū)大小,以滿足不同成本和性能的應(yīng)用。

數(shù)據(jù)輸入和數(shù)據(jù)輸出為 FIFO 接口,使用獨(dú)立的時(shí)鐘。

適用于 xilinx 的 FPGA,spartan-3 系列,spartan-6 系列,virtex-4/5/6/7 系列不同配置的性能。

實(shí)時(shí)金融指數(shù)行情計(jì)算模型與并行調(diào)度策略

研究實(shí)時(shí)金融指數(shù)(本計(jì)劃書以股票ETF50為例)股票推導(dǎo)的計(jì)算模型與計(jì)算方法,根據(jù)數(shù)據(jù)計(jì)算類型的特點(diǎn)設(shè)計(jì)專用硬件處理單元的結(jié)構(gòu)模型;

研究有限計(jì)算資源條件下的行情數(shù)據(jù)緩存與并行調(diào)度策略,研究硬件計(jì)算資源劃分與共享技術(shù);

研究透明數(shù)據(jù)接口技術(shù),包括輸入端旁路高速數(shù)據(jù)獲取技術(shù)與實(shí)現(xiàn)方法以及輸出端的應(yīng)用接口技術(shù)。

基于FPGA的并行加速技術(shù)

研究基于FPGA的硬件千兆以太網(wǎng)數(shù)據(jù)獲取技術(shù),實(shí)現(xiàn)完全硬件的TCP/IP協(xié)議棧解析和數(shù)據(jù)包過濾;

研究行情驅(qū)動(dòng)的大規(guī)模專用套利數(shù)據(jù)處理單元結(jié)構(gòu)、數(shù)據(jù)緩存與并行分發(fā)機(jī)制以及數(shù)據(jù)流水調(diào)度算法。

研究面向同構(gòu)計(jì)算單元(同種計(jì)算模型)和異構(gòu)計(jì)算單元(異種推導(dǎo)模型)協(xié)同的FPGA資源劃分技術(shù),對(duì)資源進(jìn)行優(yōu)化配置,在有限計(jì)算資源條件下獲得最高的并行加速性價(jià)比。

實(shí)時(shí)金融指數(shù)行情的可配置與可擴(kuò)展技術(shù),充分考慮FPGA專用邏輯特點(diǎn)提供計(jì)算模型的配置與合約推導(dǎo)的擴(kuò)展方案。

研究實(shí)時(shí)金融指數(shù)行情數(shù)據(jù)的高速分發(fā)及應(yīng)用接口技術(shù),采用高速傳輸總線結(jié)構(gòu)實(shí)現(xiàn)實(shí)時(shí)金融指數(shù)行情數(shù)據(jù)的提取和管理。

基于FPGA的并行加速技術(shù)方案

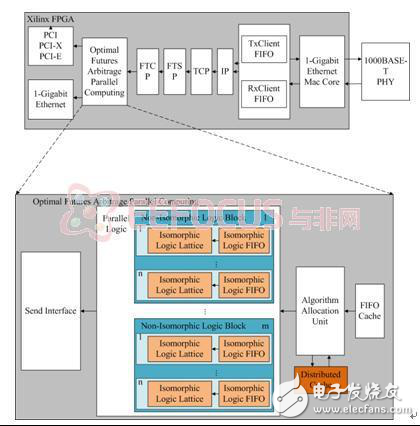

圖為系統(tǒng)結(jié)構(gòu)圖,主要由數(shù)據(jù)接收模塊、股票信息并行處理模塊、數(shù)據(jù)發(fā)送模塊組成。數(shù)據(jù)接收模塊主要負(fù)責(zé)協(xié)議包的跨層解析以及包過濾。股票信息并行處理模塊是整個(gè)系統(tǒng)的算法核心,采用高速并行方式分析股票信息,計(jì)算相關(guān)指數(shù),并通過數(shù)據(jù)發(fā)送模塊快速發(fā)布。在股票信息并行處理模塊中,算法定向單元負(fù)責(zé)調(diào)度下層的異構(gòu)邏輯塊,異構(gòu)邏輯塊通過同構(gòu)邏輯晶格完成最基礎(chǔ)的數(shù)據(jù)計(jì)算。在股票信息并行處理模塊中,將所有的數(shù)據(jù)存儲(chǔ)于FPGA內(nèi)部的分布式RAM中,突破了IO傳輸?shù)钠款i。

圖7 FPGA計(jì)算系統(tǒng)結(jié)構(gòu)圖

北京太速科技有限公司 一直致力于大數(shù)據(jù)智能計(jì)算平臺(tái)產(chǎn)品開發(fā)。基于 FPGA的微秒級(jí)實(shí)時(shí)金融平臺(tái) 歡迎參與合作。

來源:北京太速科技有限公司

-

FPGA

+關(guān)注

關(guān)注

1643文章

21949瀏覽量

613721

發(fā)布評(píng)論請(qǐng)先 登錄

實(shí)時(shí)仿真板卡SimuCard*

通信中的調(diào)制指數(shù)具體怎么計(jì)算?

請(qǐng)問怎么在ucosII中實(shí)現(xiàn)微秒級(jí)的延時(shí)?

1553B通信與定時(shí)器實(shí)現(xiàn)微秒精度

基于windows仿真光學(xué)遙感微秒實(shí)時(shí)通信

基于windows仿真光學(xué)遙感微秒實(shí)時(shí)通信

4通道光耦 PS2801-4(NEC2801-4), 2011年價(jià)格行情指數(shù)

FPGA如何解決金融科技遇上的延時(shí)問題

利用AI與數(shù)據(jù)中心規(guī)模的加速計(jì)算相結(jié)合的強(qiáng)大指數(shù)級(jí)算力

金融機(jī)構(gòu)如何構(gòu)建實(shí)時(shí)計(jì)算能力

產(chǎn)業(yè)導(dǎo)讀 | 量子計(jì)算如何精準(zhǔn)“滴灌”金融行業(yè)?

基于FPGA與PCI總線的實(shí)時(shí)控制計(jì)算機(jī)的設(shè)計(jì)與實(shí)現(xiàn)

基于FPGA微秒級(jí)實(shí)時(shí)金融指數(shù)行情計(jì)算

基于FPGA微秒級(jí)實(shí)時(shí)金融指數(shù)行情計(jì)算

評(píng)論