核心要點

受控阻抗布線通過匹配走線阻抗來防止信號失真,從而保持信號完整性。

高速PCB設計中,元件與走線的阻抗匹配至關重要。

PCB材料的選擇(如低損耗層壓板)對減少信號衰減起關鍵作用。

受控阻抗布線如何保障信號完整性

為實現電路信號完整性,需遵循以下設計規范:避免直角走線、隔離時鐘信號與電源信號、保持元件間最短距離。

受控阻抗布線通過調整走線尺寸和環境參數,使其特性阻抗與設計目標匹配,從而確保信號傳輸過程中的完整性。隨著信號速度提升(甚至達到GHz級且面積縮小),信號完整性成為關鍵考量。該技術能維持信號強度,使其從源端到終端的傳輸過程保持穩定。

受控阻抗布線在電路中的行為

電路中除源端和負載外還存在大量元件。能量從元件輸出引腳經走線流向負載時會產生失真和損耗。若能量未被負載完全吸收,會反射回源端,引發疊加或抵消效應(如振鈴現象),導致信號完整性受損。

阻抗不匹配時,電路可能表現異常。通過匹配走線阻抗可抑制信號反射。當源端與負載阻抗匹配時,能量沿走線傳輸效率最高,實現從源端到走線、再從走線到負載的高效耦合。這種基于阻抗匹配的布線技術稱為受控阻抗布線,可有效消除失真、振鈴和信號丟失。

受控阻抗布線設計方法

1. 元件阻抗匹配

首先需匹配電路中元件的阻抗。輸入引腳的高阻抗與輸出引腳的低阻抗會導致失配,通過在輸入/輸出引腳間添加端接元件可實現阻抗匹配。

2. 走線阻抗匹配

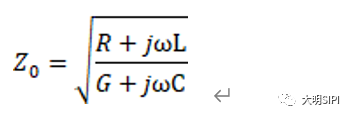

通過調整走線幾何尺寸(長、寬、厚度)及環境參數(如介質常數)實現目標阻抗。走線特性阻抗由電阻、感抗、容抗和電導共同決定。設計良好的受控阻抗布線可使阻抗在跨層傳輸時保持恒定(典型值范圍:25–125 ?)。

PCB材料的介質常數和介質厚度影響走線阻抗。高速設計優先選用低介電常數、低損耗角正切的層壓板材料,以提升信號性能,減少失真和相位抖動。低損耗材料制造的PCB能顯著改善高頻設計的信號完整性。

PCB中的受控阻抗設計實例

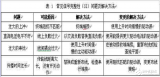

在多層電路板中,走線位于層間,需通過兩側層壓板厚度實現阻抗匹配。以下是多層PCB中常見的受控阻抗結構示例:

微帶線類型 | 描述 |

嵌入式微帶線 | 走線夾于平面層間,一側為平面層,另一側為層壓板與空氣介質組合。 |

偏移帶狀線 | 走線兩側完全由層壓板覆蓋。 |

邊緣耦合偏移帶狀線 | 兩條受控阻抗走線置于兩平面層之間。 |

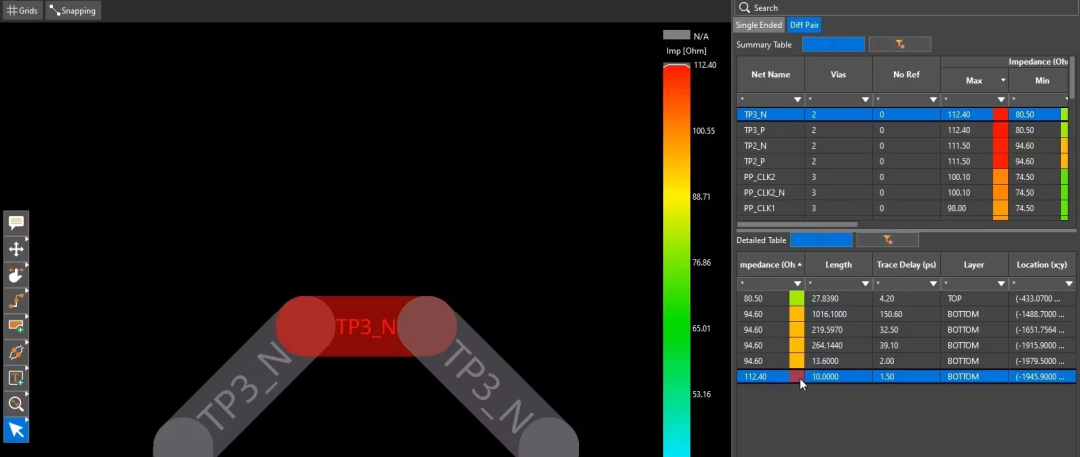

OrCAD X 24.1版本優化了阻抗與耦合設計流程,提供更高效的受控阻抗布線支持。

在OrCAD X 中應用受控阻抗布線

OrCAD X 提供了一套全面的工具,專門用于幫助設計人員實現受控阻抗布線。這些功能允許精確控制 PCB 走線的阻抗。

功能 | 描述 | 對受控阻抗布線的支持 |

疊層設計配置 | 定義PCB疊層結構,指定材料屬性、層數與厚度。 | 通過控制信號走線與參考平面間距,確保阻抗一致性。 |

設計規則定義 | 設置電氣、物理及制造約束(如阻抗、線寬、過孔尺寸) | 嚴格遵循阻抗規范,降低信號完整性風險。 |

實時阻抗分析 | 設計過程中即時反饋阻抗值。 | 快速識別并修正阻抗失配,確保最終電路符合電氣性能標準 |

設計內耦合分析 | 評估相鄰走線間的耦合效應。 | 調整走線間距與布局,減少串擾并維持阻抗穩定。 |

| 高速布線與SI分析集成 | 結合信號完整性分析優化高頻信號走線。 | 通過阻抗匹配減少反射與信號衰減,提升高頻信號質量。 |

在處理高速、高頻關鍵信號時,信號完整性必須全程保持。受控阻抗布線是PCB設計的核心實踐,可確保信號從源端到負載的無損傳輸。當走線阻抗匹配時,信號完整性失效概率將降至最低。

OrCAD X提供全套工具保障走線阻抗匹配,助力實現最優性能。

文章來源:Cadence

-

阻抗匹配

+關注

關注

14文章

358瀏覽量

31261 -

阻抗

+關注

關注

17文章

970瀏覽量

46995 -

PCB設計

+關注

關注

396文章

4774瀏覽量

89063 -

信號完整性

+關注

關注

68文章

1432瀏覽量

96404

發布評論請先 登錄

看我在設計電路板時是如何確保信號完整性的

如何確保PCB設計信號完整性

信號完整性簡介及protel信號完整性設計指南

受控阻抗布線技術確保信號完整性

受控阻抗布線技術確保信號完整性

評論