Verilog和SystemVerilog定義了4種描述信號狀態: 1, 0, X, and Z。1和0無疑是真實存在的信號狀態. 而Z用來表示高阻態,X用來表示不確定的狀態。

X信號可以有意或無意地被創建,最常見的X信號存在于未被初始化的memory register,這里X用來表示這些memory在reset之前的的未知狀態 。其他一些可以產生X的場景包括了不同的driver驅動同一塊邏輯到不同的邏輯值,或者是在low power中的關斷信號,又或者是一些超過選擇范圍的多比特信號。 有些設計者會對design中那些dont care的信號設為X,讓綜合工具在做優化的時候來隨機選擇0或者1進行優化。也有些設計者為了debug的目的在設計中對那些不會用到的邏輯值設X,這樣在做仿真的時候如果使用到這些邏輯,說明電路有問題,而仿真工具產生的X可以檢查到這些邏輯。有意地設置一些X信號是比較有爭議的做法。在做lint檢查的時候也會被標識出來。但是有些X狀態由于仿真器識別的原因(verilog X optimism)會產生錯誤的仿真結果。這就屬于RTl的bug了。

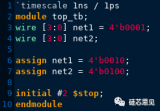

第一個verilog X optimism的例子來自if...else語句:

|

1 2 3 4 5 6 |

always_ff@(posedge clk)begin if(cond) c <= a; else c <= b; end |

Verilog LRM 指出如果if...else的條件是X狀態,那么這個條件就會被當作false處理,在這里只有else語句會被執行。

在實際設計中有一種情況可能會產生這種問題:cond信號來自于memory。比如漢明碼SECDED(single error correction double error detection)解碼器,其檢測的序列是儲存漢明碼的寄存器,這段序列是否錯誤的cond是由這些寄存器經過一段組合邏輯產生,當cond為TRUE時輸出錯誤信號error=1。在reset之前這些寄存器都是X狀態,原本錯誤信號應該是error=1,但是在仿真中由于verilog X optimism這種特性,寄存器的X經過組合邏輯傳播到cond,導致最后將cond=X判斷為FALSE,輸出錯誤信號為0,這就與實際電路行為相違背了。

Verilog X optimism的另外一個例子是case語句:

|

1 2 3 4 5 6 |

always_ff@(posedge clk)begin case(cond) 1'b0 : c = a; 1'b1 : c = b; endcase end |

在case語句中如果cond為X的話,c將會保留原值。這里原本是描述了一個mux的行為,但由于X optimism的原因,仿真行為與RTL描述不一致。

此外,Verilog X optimism還會影響到0/1->X/Z的處理。下面的這些狀態轉移都會被視為posedge:

0->1, 0->X, 0->Z, X->1, Z->1

0->X or X->1實際上不一定是posedge,但在仿真中,他們都會被當作posedge處理。

-

寄存器

+關注

關注

31文章

5421瀏覽量

123290 -

Verilog

+關注

關注

28文章

1365瀏覽量

111789

原文標題:verilog——X optimism

文章出處:【微信號:ic_frontend,微信公眾號:數字前端ic芯片設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

使用Verilog/SystemVerilog硬件描述語言練習數字硬件設計

用Verilog/SystemVerilog快速實現一個加法樹

SystemVerilog 3.1a語言參考手冊

基于Verilog的順序狀態邏輯FSM的設計與仿真

SystemC 和SystemVerilog的比較

Verilog HDL代碼描述對狀態機綜合的研究

基于Verilog硬件描述語言的IEEE標準硬件描述語言資料合集免費下載

System Verilog與verilog的對比

SystemVerilog語言介紹匯總

System Verilog與verilog的概念有何不同

使用Verilog/SystemVerilog硬件描述語言練習數字硬件設計

FPGA學習-SystemVerilog語言簡介

從Verilog PLI到SystemVerilog DPI的演變過程

SystemVerilog相比于Verilog的優勢

Verilog和SystemVerilog定義了4種描述信號狀態

Verilog和SystemVerilog定義了4種描述信號狀態

評論