概述

AD9520-2提供多路輸出時(shí)鐘分配功能,具有亞皮秒級(jí)抖動(dòng)性能,并且片內(nèi)集成鎖相環(huán)(PLL)和電壓控制振蕩器(VCO)。片內(nèi)VCO的調(diào)諧頻率范圍為2.02 GHz至2.335 GHz。也可以使用最高2.4 GHz的外部3.3 V/5 V VCO/VCXO。

數(shù)據(jù)表:*附件:AD9520-2 12路LVPECL 24路CMOS輸出時(shí)鐘發(fā)生器技術(shù)手冊(cè).pdf

AD9520-2串行接口支持SPI和I^2^C端口。封裝內(nèi)EEPROM能夠通過(guò)串行接口進(jìn)行編程,其可存儲(chǔ)用于上電和芯片復(fù)位的用戶定義寄存器設(shè)置。

AD9520-2具有12路LVPECL輸出,分為四組。任何一路1.6 GHz LVPECL輸出都可以重新配置為兩路250 MHz CMOS輸出。若應(yīng)用需要LVDS驅(qū)動(dòng)器而非LVPECL驅(qū)動(dòng)器,請(qǐng)參考AD9522-2。每組3路輸出具有一個(gè)分頻器,其分頻比(從1至32)和相位失調(diào)或粗調(diào)時(shí)間延遲均可設(shè)置。

AD9520-2提供64引腳LFCSP封裝,可以采用3.3 V單電源供電。外部VCO的工作電壓可高達(dá)5.5 V。獨(dú)立的輸出驅(qū)動(dòng)器電源可以為2.375 V至3.465 V。

AD9520-2的額定工作溫度范圍為?40°C至+85°C標(biāo)準(zhǔn)工業(yè)溫度范圍。

應(yīng)用

- 低抖動(dòng)、低相位噪聲時(shí)鐘分配

- SONET、10Ge、10GFC、同步以太網(wǎng)、OTU2/3/4的時(shí)鐘產(chǎn)生和轉(zhuǎn)換

- 前向糾錯(cuò)(G.710)

- 為高速ADC、DAC、DDS、DDC、DUC、MxFE提供時(shí)鐘

- 高性能無(wú)線收發(fā)器

- 自動(dòng)測(cè)試設(shè)備(ATE)和高性能儀器儀表

- 寬帶基礎(chǔ)設(shè)施

特性

- 低相位噪聲鎖相環(huán)(PLL)

- 片內(nèi)VCO的調(diào)諧頻率范圍為2.02 GHz至2.335 GHz

- 可選外部3.3 V/5 V VCO/VCXO至2.4 GHz

- 1路差分或2路單端基準(zhǔn)輸入

- 支持最高250 MHz的CMOS、LVDS或LVPECL參考

- 參考輸入接受16.62 MHz至33.3 MHz晶振

- 可選參考時(shí)鐘倍頻器

- 參考監(jiān)控功能

- 自動(dòng)/手動(dòng)參考保持和參考切換模式,恢復(fù)式切換

- 參考間無(wú)毛刺切換

- 從保持模式自動(dòng)恢復(fù)

- 可選數(shù)字或模擬鎖定檢測(cè)

- 可選零延遲工作

- 12路1.6 GHz LVPECL輸出分為4組

- 每組3路輸出,共享一個(gè)帶相位延遲的1至32分頻器

- 加性輸出抖動(dòng)低至225 fs rms

- 分組輸出的通道間偏斜 < 16 ps

- 可以將每路LVPECL輸出配置為2路CMOS輸出(f

OUT≤ 250 MHz)

- 上電時(shí)所有輸出自動(dòng)同步

- 提供手動(dòng)輸出同步

- SPI和I^2^C兼容型串行控制端口

- 64引腳LFCSP

- 非易失性EEPROM存儲(chǔ)配置設(shè)置

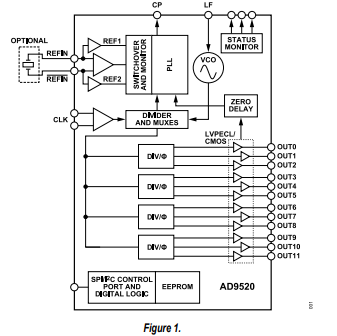

框圖

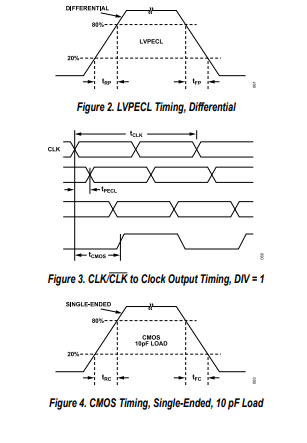

時(shí)序圖

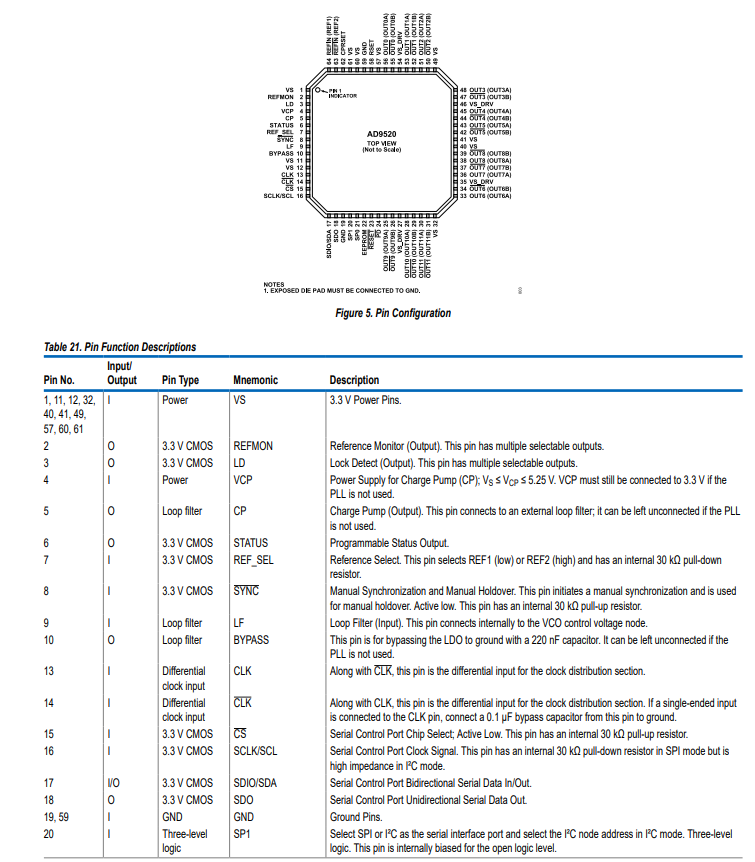

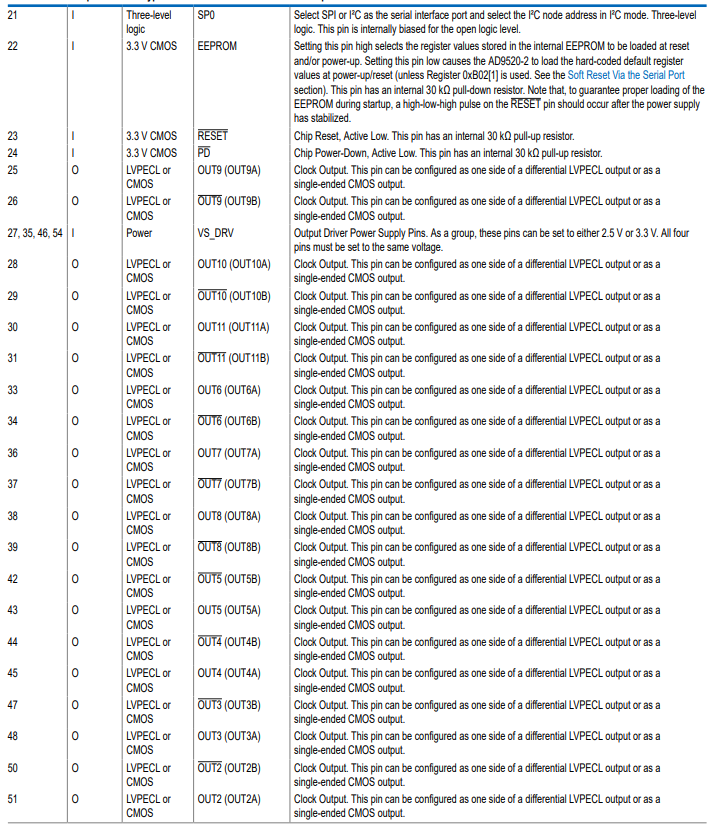

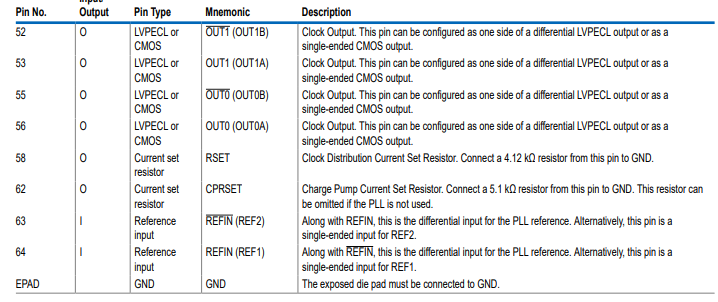

引腳配置描述

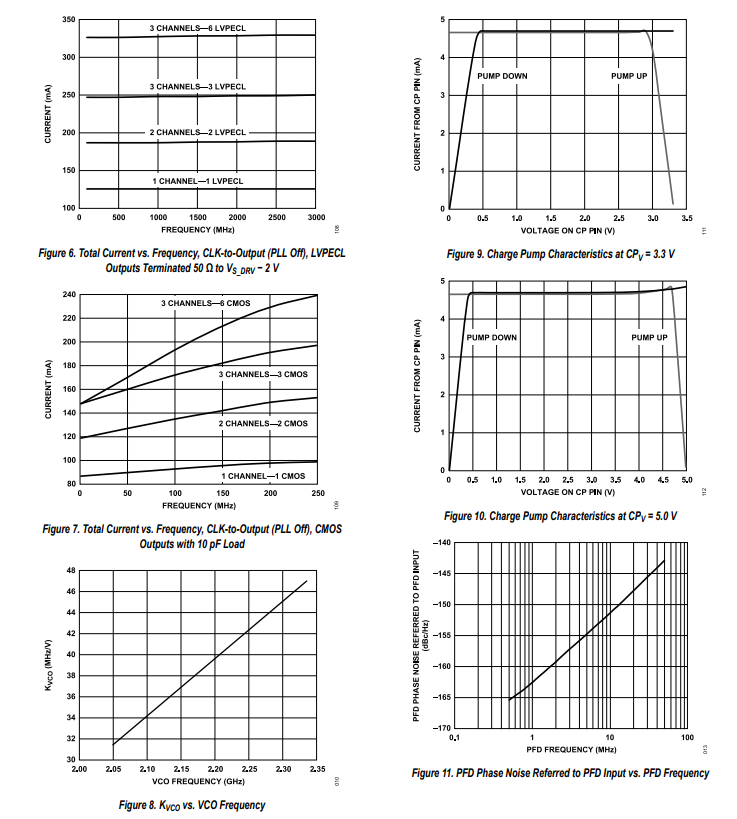

典型性能特征

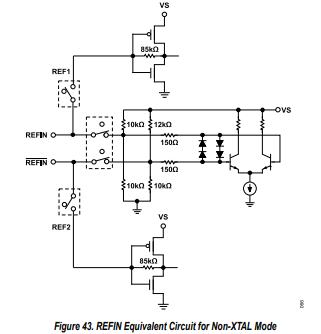

這增加了驅(qū)動(dòng)器所需的電壓擺幅,并克服了偏移。差分參考輸入可以由交流耦合LVDS或交流耦合LVPECL信號(hào)驅(qū)動(dòng)。

單端輸入可以由直流耦合CMOS電平信號(hào)或交流耦合正弦波或方波驅(qū)動(dòng)。為避免單端交流耦合輸入信號(hào)停止擺動(dòng)時(shí)輸入緩沖器抖動(dòng),用戶可以設(shè)置寄存器0x18[7],將直流偏置點(diǎn)下移140 mV。為增加隔離和降低功耗,每個(gè)單端輸入可以獨(dú)立斷電。

當(dāng)選擇差分參考輸入時(shí),差分參考輸入接收器通電;當(dāng)PLL斷電時(shí),該接收器斷電。當(dāng)選擇單端參考輸入時(shí),單端緩沖器斷電。當(dāng)PLL斷電或所選參考獨(dú)立斷電時(shí),單端緩沖器斷電。

在差分模式下,參考輸入引腳內(nèi)部自偏置,因此它們可以接受交流耦合信號(hào)。如果差分REFIN由單端信號(hào)驅(qū)動(dòng),未使用的一側(cè)({REFIN}})應(yīng)通過(guò)合適的電容去耦到靜地。圖43展示了REFIN的等效電路。

晶體模式與差分模式非常相似。用戶通過(guò)設(shè)置enable XTAL位,并在REFIN和**overline{text{REFIN}}**引腳之間連接一個(gè)串聯(lián)諧振、基頻切割晶體,來(lái)啟用一個(gè)穩(wěn)幅放大器。

參考切換

AD9520 - 2支持雙單端CMOS輸入,以及單差分參考輸入。雙單端參考輸入(REF1引腳和REF2引腳)之間的PLL參考時(shí)鐘切換,可確保參考時(shí)鐘之間的相位連續(xù)性。此功能支持網(wǎng)絡(luò)和其他應(yīng)用,這些應(yīng)用要求在不出現(xiàn)過(guò)多參考時(shí)鐘瞬變的情況下切換參考時(shí)鐘。與自動(dòng)保持模式結(jié)合使用時(shí),AD9520 - 2可實(shí)現(xiàn)最差情況下頻率偏差在±10 ppm以內(nèi)的參考時(shí)鐘切換。

AD9520 - 2在單端模式下具有直流偏移功能。此功能旨在消除參考輸入在交流耦合且參考時(shí)鐘不連續(xù)時(shí)抖動(dòng)的風(fēng)險(xiǎn)。使用參考切換器時(shí),輸入信號(hào)(啟用AD9520 - 2的直流偏移功能時(shí)為直流耦合CMOS電平)應(yīng)具有最小輸入幅度。或者,輸入可以交流耦合且啟用直流偏移功能,但要注意直流偏移功能會(huì)增加輸入幅度。

參考切換可以通過(guò)寄存器0x01C手動(dòng)或自動(dòng)執(zhí)行,或使用REF_SEL引腳執(zhí)行。要啟用切換,必須通過(guò)將寄存器0x01C的第7位設(shè)置為1來(lái)禁用保持放大器。如果不滿足此條件,PLL將不會(huì)切換。

自動(dòng)相對(duì)切換可通過(guò)REFMON引腳啟動(dòng)。在編程寄存器0x01F為0x07且寄存器0x01C為0x06后,REFMON引腳被編程為在REF1有效時(shí)發(fā)出高電平信號(hào),在REF2有效時(shí)發(fā)出低電平信號(hào)。當(dāng)REF1再次有效時(shí),REFMON引腳再次變?yōu)楦唠娖剑瞬糠直O(jiān)控鎖定狀態(tài)。STATUS引腳也可用于此功能,并且可以確保PLL在切換期間不會(huì)接收新選擇的參考時(shí)鐘的上升沿。對(duì)于與新選擇的參考時(shí)鐘對(duì)齊的故障切換功能,鎖定到正在切換的參考時(shí)鐘是必需的。可以通過(guò)禁用寄存器0x01C[7]中的直流偏移功能來(lái)禁用此功能。

不支持自動(dòng)非相對(duì)切換。

參考分頻器R

參考輸入被路由到參考分頻器R。R是一個(gè)14位計(jì)數(shù)器,可以設(shè)置為0到16,383之間的任何值(通過(guò)SPI接口寫(xiě)入時(shí)為0到16,382,因?yàn)橛?個(gè)除法器)。R的輸出除以VCO頻率除以N分頻器得到的PFD輸入。應(yīng)用的分頻比必須不超過(guò)最大值(見(jiàn)規(guī)格),以防止PFD處出現(xiàn)反沖。

-

pll

+關(guān)注

關(guān)注

6文章

889瀏覽量

136401 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1900瀏覽量

133200 -

VCO

+關(guān)注

關(guān)注

13文章

311瀏覽量

70197 -

AD9520

+關(guān)注

關(guān)注

0文章

8瀏覽量

6628

發(fā)布評(píng)論請(qǐng)先 登錄

AD9520-3BCPZ時(shí)鐘發(fā)生器

AD9520-2超低噪聲PLL時(shí)鐘合成器評(píng)估板

具有自動(dòng)hoLDOver和靈活的參考輸入電路的AD9520

AD9520-2 12路LVPECL/24路CMOS輸出時(shí)鐘發(fā)生器,集成2.2 GHz VCO

AD9523時(shí)鐘發(fā)生器的性能特點(diǎn)及應(yīng)用分析

AD9520-0:12路LVPECL/24路CMOS輸出時(shí)鐘發(fā)生器,集成2.8 GHz VCO

AD9523-1:低抖動(dòng)時(shí)鐘發(fā)生器,14路LVPECL/LVDS/HSTL輸出或29路LVCMOS輸出 數(shù)據(jù)手冊(cè)

AD9525: 8路LVPECL輸出低抖動(dòng)時(shí)鐘發(fā)生器

AD9520-3:12集成2 GHz壓控振蕩器數(shù)據(jù)表的LVPECL/24 CMOS輸出時(shí)鐘發(fā)生器

AD9520-1:12集成2.5 GHz壓控振蕩器數(shù)據(jù)表的LVPECL/24 CMOS輸出時(shí)鐘發(fā)生器

AD9520-2:12集成2.2 GHz壓控振蕩器數(shù)據(jù)表的LVPECL/24 CMOS輸出時(shí)鐘發(fā)生器

AD9520-5:12 LVPECL/24 CMOS輸出時(shí)鐘發(fā)生器數(shù)據(jù)表

AD9522-5:12 LVDS/24 CMOS輸出時(shí)鐘發(fā)生器數(shù)據(jù)表

集成2.2 GHz VCO數(shù)據(jù)表的AD9522-2:12 LVDS/24 CMOS輸出時(shí)鐘發(fā)生器

AD9520-4:12集成1.6 GHz壓控振蕩器數(shù)據(jù)表的LVPECL/24 CMOS輸出時(shí)鐘發(fā)生器

AD9520-2 12路LVPECL/24路CMOS輸出時(shí)鐘發(fā)生器技術(shù)手冊(cè)

AD9520-2 12路LVPECL/24路CMOS輸出時(shí)鐘發(fā)生器技術(shù)手冊(cè)

評(píng)論