概述

AD9546 采用數字化時鐘技術,可在系統中高效傳輸和分配時鐘信號。數字化時鐘具有設計靈活性,且可使用可擴展的時鐘傳輸系統,并具有良好的相位(時間)對齊控制。這些特性使 AD9546 成為必須滿足 ITU-T G.8273.2 D 類的 IEEE^?^ 1588^?^ 邊界時鐘的同步要求的網絡設備設計的首選。數字時鐘還與要求將頻率和相位精確傳輸到多個使用端點的應用有關(例如,將同步系統參考 (SYSREF) 時鐘分配到 ADC 通道陣列)。

AD9546 支持現有和新興的國際電信聯盟 (ITU) 標準,通過服務提供商分組網絡,可交付頻率、相位和時刻,這些分組網絡包括 ITU-G.8262、ITU-T G.812、ITU-T G.813、ITU-T G.823、ITU-T G.824、ITU-T G.825 和ITU-T G.8273.2。

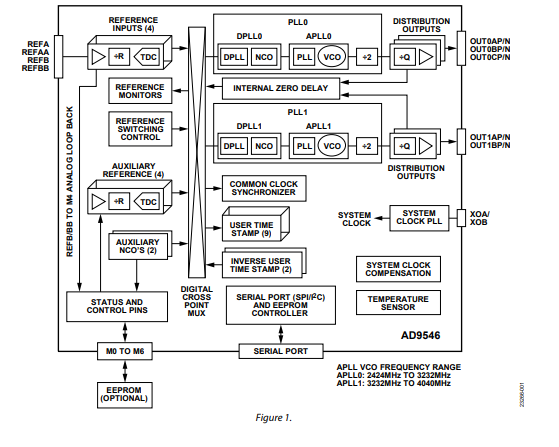

將 AD9546 的 10 個時鐘輸出同步為多達八個輸入基準電壓源中的任意一個。數字鎖相環 (DPLL) 減少了與外部基準電壓源相關的時序抖動,而模擬鎖相環 (APLL) 提供了具有低抖動輸出時鐘的頻率轉換。數字控制的環路和保持電路即使在所有參考輸入失敗時仍可持續產生低抖動輸出信號。

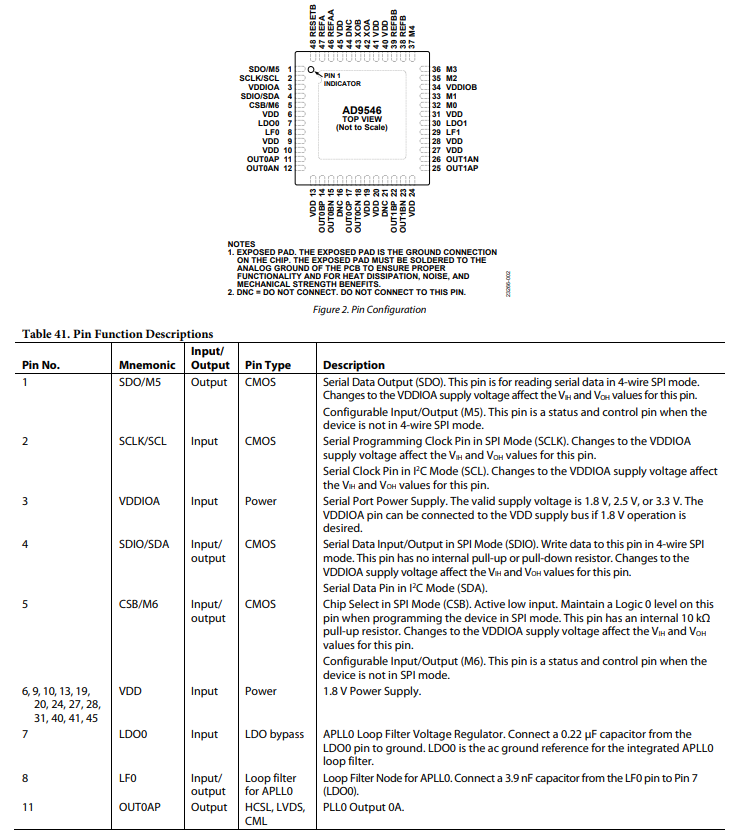

AD9546 提供 48 引腳 LFCSP (7 mm × 7 mm) 封裝,可在 ?40°C 至 +85°C 的溫度范圍內工作。

在整個數據手冊中,當僅涉及多功能引腳名稱的單個功能時(例如,針對SDO/M5 的 M5),可參考該功能。

數據表:*附件:AD9546雙DPLL數字時鐘同步器技術手冊.pdf

應用

- 5G 時序傳輸高精度同步

- 全球定位系統 (GPS)、精確時間協議 PTP (IEEE 1588) 和同步以太網 (SyncE) 抖動濾除和同步

- 光傳送網絡 (OTN)、同步數字體系 (SDH) 以及宏基站和小蜂窩基站。小型基站時鐘(基帶和射頻)

- Stratum 2、Stratum 3e 和 Stratum 3 保持、去除信號抖動和相位瞬態控制

- JESD204B 支持模數轉換器 (ADC) 和數模轉換器 (DAC) 時鐘

- 運營商級以太網

特性

- 數字時鐘傳輸子系統

- 9 個獨立的 UTS 塊(時間戳出口)

- 2 個獨立的 IUTS 塊(時間戳入口)

- 雙 DPLL 可同步 1 Hz 到 750 MHz 物理層時鐘,可在提供頻率轉換的同時去除噪聲基準電壓源的信號抖動

- 符合 ITU-T G.8262 和 Telcordia GR-253 標準

- 支持 Telcordia GR-1244、ITU-T G.812、ITU-T G.813、ITU-T G.823、ITU-T G.824、ITU-T G.825 和 ITU-T G.8273.2

- 針對低至 50 ppb (5 × 10

?8) 的頻率偏移,可進行持續頻率監控和基準電壓源驗證 - 兩個 DPLL 都配有帶有 24 位可編程模塊的 24 位小數分頻器

- 可編程數字環路濾波器帶寬:0.0001 Hz 至 1850 Hz

- 兩個獨立的可編程輔助 NCO(1 Hz 至 65,535 Hz,分辨率 < 1.37 pHz),適合 PTP 應用中的 IEEE-1588 第 2 版伺服反饋

- 自動和手動保持和基準電壓源切換,實現零延遲、無中斷或相位增建

- 基于可編程優先級的基準電壓源切換,支持手動、自動可逆和自動不可逆模式

- 5 對時鐘輸出引腳,每對都可用作差分 LVDS/HCSL/CML 或用作 2 個單端輸出(1 Hz 至 500 MHz)

- 2 個差分或 8 個單端輸入基準電壓源

- 交叉點多路復用器將參考輸入與 PLL 互連

- 支持嵌入式(模塊化)輸入/輸出時鐘信號

- 快速 DPLL 鎖定模式

- 提供內部功能,可兼具晶體諧振器或晶體振蕩器的低相位噪聲特點,以及 TCXO 或 OCXO 的頻率穩定性和精度

- 針對自主初始化提供外部 EEPROM 支持

- 1.8 V 單電源供電,帶有內部調節功能

- 內置溫度監視器/警報和溫度補償,可增強零延遲性能

框圖

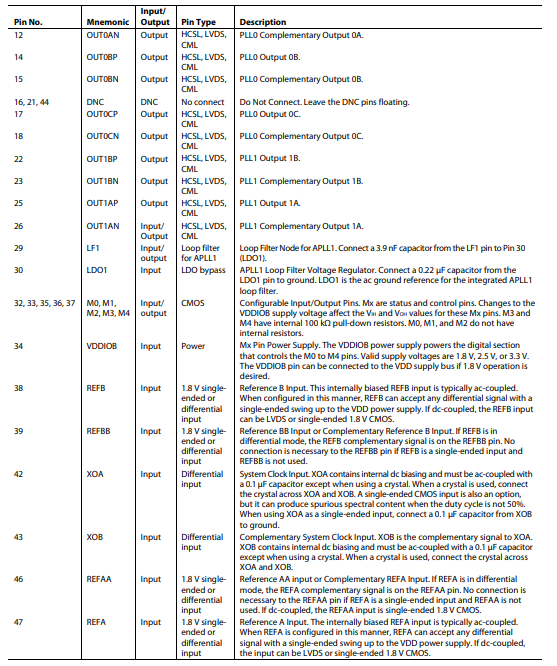

引腳配置描述

數字化時鐘技術可實現精確的定時傳輸(頻率和相位),在空間上分離的設備之間通過數字時間碼進行同步(假設所有設備都能訪問公共參考時鐘信號)。

數字化時鐘系統由多個定時節點組成,每個節點依賴于共享的外部時基(公共時鐘參考)。由于每個節點共享相同的公共時鐘參考,且節點增量以相同速率變化,因此所有節點都具有相同的時間尺度。盡管所有節點都處于同一尺度,但并不能保證它們共享同一時刻。數字化時鐘依賴于用戶在每個節點設置的同步信號,最終使所有節點實現時間對齊。數字化時鐘的一個獨特特性是能夠通過數字總線在節點之間交換數字時間碼,這意味著可以向一個或多個數字總線(時鐘聚合)發送多個時鐘,以路由多個模擬時鐘信號來構建系統。AD9546包含實現數字化時鐘節點所需的所有構建模塊。

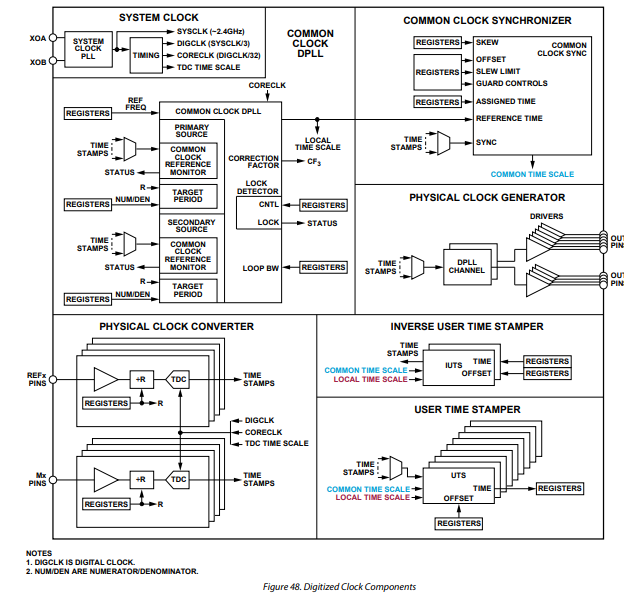

圖48展示了AD9546中實現的完整數字化時鐘節點的各個組件。這些數字化時鐘組件包括:

- 系統時鐘PLL,用于生成系統時鐘頻率,以實現內部定時功能(詳見“系統時鐘PLL”部分)

- 公共時鐘DPLL,用于與參考時基(公共時鐘參考)進行鎖相,并維持本地時間尺度

- 物理時鐘轉換器,用于將系統時鐘的時間戳轉換為物理時鐘

- 物理時鐘發生器,用于將從公共時間尺度導出的時間戳轉換為物理時鐘輸出信號

- ACCS,通過為本地時間尺度分配時刻來創建公共時間尺度

- UTS,用于將內部時間戳轉換為基于公共時間尺度的時間碼,并將這些時間碼提供給用戶用于外部使用

- IUTS,用于將用戶提供的基于公共時間尺度的一系列時間碼轉換為內部時間戳

圖48展示了多種時間戳源。某些數字化時鐘組件需要能夠連接到任意一個時間戳源,這就是為什么這些組件在其輸入處包含時間戳選擇多路復用器。

系統時鐘PLL組件

系統時鐘PLL通常使用外部晶體諧振器作為頻率源,這往往能提供最佳的整體相位噪聲性能。系統時鐘PLL從外部頻率源(約2.4GHz)合成高頻內部系統時鐘信號,為設備提供基本的內部定時。設備使用系統時鐘來生成時間戳(詳見“時間數字轉換器(TDC)”部分)。

請注意,內部系統時鐘信號是公共時鐘DPLL組件用于生成本地時間尺度的兩個頻率源之一。

公共時鐘DPLL組件

公共時鐘DPLL的作用是生成本地時間尺度。公共時鐘DPLL使用系統時鐘進行內部定時,但其相位鎖定到參考時基,即公共時鐘參考。公共時鐘DPLL的輸出是本地時間尺度,它累積了公共時鐘參考的周期,并為數字化時鐘組件提供內部時間感知。

公共時鐘DPLL固有的閉環架構意味著其運行會產生誤差,校正因子3(CF3)有效地補償了系統時鐘的波動。請注意,CF3信號可用于AD9546的系統時鐘補償功能模塊(詳見“補償方法3”部分)。

物理時鐘轉換器

物理時鐘轉換器有一個輸入,用于接收外部時鐘信號,提供可選的整數頻率分頻功能,并將上升沿時鐘轉換為數字時間戳。然后,這些時間戳可供需要時間戳源的數字化時鐘組件使用。

物理時鐘發生器

物理時鐘發生器利用AD9546的DPLL通道和輸出分配驅動器,從時間戳生成模擬時鐘輸出信號。在數字化時鐘應用中,時間戳源自公共時間尺度。由于DPLL可以從這些時間戳中獲取其參考輸入,因此物理時鐘發生器的輸出由模擬時鐘信號組成。

-

時鐘

+關注

關注

11文章

1863瀏覽量

132733 -

DPLL

+關注

關注

1文章

26瀏覽量

14165 -

數字化

+關注

關注

8文章

9171瀏覽量

62973

發布評論請先 登錄

DAY-1000數字音頻同步器

同步器的作用

AD9546: Dual DPLL Digitized Clock Synchronizer Data Sheet

AD9543:四路輸入、10路輸出、雙DPLL/IEEE 1588同步器和抖動清除器

LMK5B33216 3 DPLL、3 APLL、2路輸入、16路輸出網絡同步器數據表

AD9546雙DPLL數字時鐘同步器技術手冊

AD9546雙DPLL數字時鐘同步器技術手冊

評論