目前全球電子產業鏈的核心增長動力集中于AI服務器、交換機與各種先進設備如電動汽車、高端醫療產品,智能手機等。

研報顯示

全球PCB市場2024年增速近6.0%,其中HDI板和18層以上多層板成為增速最快的品類,增速超15%,也是受到了以上需求的驅動。

隨著PCB速率和頻率不斷增加,PCB板趨向于多層高密化,選擇合適基材并設計出滿足SI要求的疊層成為高速信號設計的核心工作之一。

PCB改版是研發人員最不期望看到的事情,而PCB選材或疊層問題是造成PCB改版的最常見的原因之一。不良的PCB選材或疊層設計會導致傳輸線阻抗失配,插損超標等嚴重的信號完整性問題。

如何才能減少或者避免因為疊層原因造成的改版?

其最大的挑戰在于如何跨越“PCB工廠的阻抗經驗修正過程”鴻溝,以實現對疊層的阻抗與插損的精確仿真能力。

當前,高速信號SI工程師在前期花了大量的努力進行疊層、阻抗和插損等仿真計算,但到PCB加工時還是需要按照PCB工廠通過FA獲取經驗值后再對阻抗重新計算并調整線寬間距,甚至調整幅度過大時需要對疊層及阻抗進行改版重新設計。

這種情況的出現源于其影響因素錯綜復雜且不透明:

PCB基材的玻纖結構眾多、不同RC對應不同的DK/DF,PCB工藝的銅厚、層壓后的厚度/DK/DF的變化、阻抗仿真軟件的精度、PCB工廠的經驗DK、銅箔粗糙度的表征與測量等等關系錯綜復雜且不透明的參數及計算過程。任何一個參數不當,都會造成阻抗及損耗模擬的偏差,這樣設計制造出來的實際產品就很難符合預期性能。

下面我們將介紹如何通過“疊層、阻抗與插損” 集成化高精度設計與仿真系統幫助PCB工廠實現去經驗化達到疊層設計的“一版成功”。

要想解決這個問題,核心有兩點:

一是準確的DK仿真

二是建立高精度的仿真模型

PCB板的橫截面,介質原材料是玻璃纖維和樹脂的混合物。玻璃纖維布類似于我們穿的衣服,交織在一起,有標準的規格,其余部分是樹脂。

我們通過軟件將這種復雜變化的介質層在Z軸方向上簡單地分成多個相對均勻的介質層,這樣原本是單一的DK值變成了多個DK值。我們可以精確地知道在每個區域DK的波動范圍,通過建立這種模型來代表DK的準確分布,然后根據銅線的電磁場分布來計算對應的DK值,進而計算阻抗值。

傳統的阻抗仿真軟件可以理解為一個純粹的阻抗計算器,用戶決定輸入的參數,即單一的DK值,然后軟件根據自身的模型算出阻抗值。而我們的方案可以認為是一種更為先進的架構,阻抗控制由三個主要因素構成,包括疊層設計、阻抗計算和工藝控制。這樣就把所有影響到阻抗的因素考慮進去,形成一種系統集成的軟件,可以實現更為精確的阻抗控制。

利用這個方案,我們就可以擺脫原先板廠的經驗DK法,使得這種設計加工從黑盒子狀態變成一種透明去經驗化的狀態。

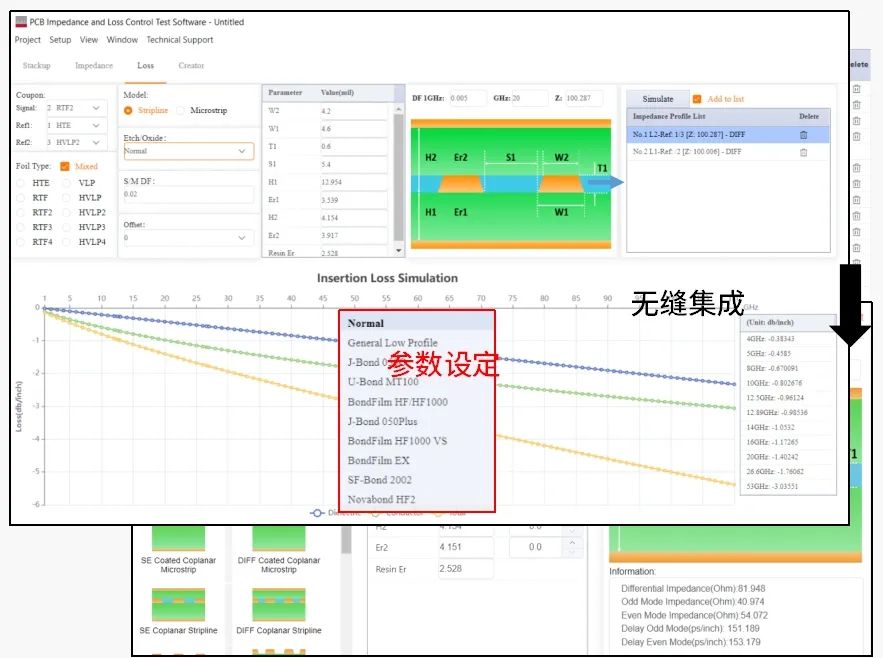

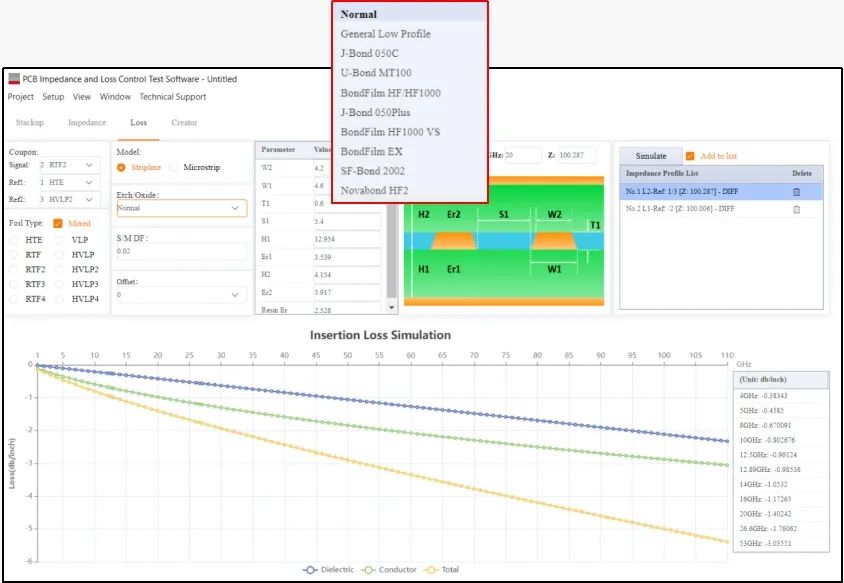

軟件的整體界面情況如上圖。左側是材料選擇界面,我們支持常用的材料供應商。選擇材料后,可以定義其為Core、PP或銅箔,然后將其添加到右側的疊層設計中。由于軟件的無縫集成,相關參數會自動從疊層設計中提取到阻抗計算器中,以進行阻抗測量。

另外,我們的方案并沒有使用Ra或Rz進行建模,而是使用銅箔和藥水的類型作為參數進行建模。以上是我們軟件的插損仿真界面,首先選擇銅箔的類型,然后選擇銅箔加工的方法和藥水類型。我們可以提供這些參數給客戶,再根據疊層結構、線寬等參數以及DF值,計算出最終的插損值。

這種方法的準確度高,我們與PCB板廠合作,使用量產數據對模型進行訓練和驗證,使其模擬插損更加精準。在插損仿真方面,我們可以做到誤差在10%以內。如果加工工藝更好一些,5%的誤差也是可以實現的。這比行業內其他軟件的準確度高很多。

智能設備、AI、高速計算等高端應用的性能對高頻高速多層高密PCB的阻抗和損耗控制需從材料選型、工藝精度、設計仿真、測試驗證等都提出了更高的要求,對高頻高速多層高密PCB板的信號完整性提出了更嚴格要求。

復雜結構帶來的挑戰,材料選擇的優化需求、加工工藝的高精度要求以及測試驗證的嚴格標準這些因素共同作用,使得在整個設計和制造過程中必須采取更精細的控制措施,以確保最終產品的高性能和高可靠性。

關于是德科技

是德科技(NYSE:KEYS)啟迪并賦能創新者,助力他們將改變世界的技術帶入生活。作為一家標準普爾 500 指數公司,我們提供先進的設計、仿真和測試解決方案,旨在幫助工程師在整個產品生命周期中更快地完成開發和部署,同時控制好風險。我們的客戶遍及全球通信、工業自動化、航空航天與國防、汽車、半導體和通用電子等市場。我們與客戶攜手,加速創新,創造一個安全互聯的世界。

-

pcb

+關注

關注

4351文章

23405瀏覽量

406532 -

仿真

+關注

關注

51文章

4234瀏覽量

135282 -

疊層

+關注

關注

0文章

29瀏覽量

10054

原文標題:PCB設計師必看:如何僅用1個軟件讓改版率暴降

文章出處:【微信號:是德科技KEYSIGHT,微信公眾號:是德科技KEYSIGHT】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

pcb改版時怎么自動標號不改變pcb原有的元器件標號

CAD云線怎么畫?CAD云線繪制技巧

如何使用帶FIFO的串口來減少接收中斷次數

如何使用帶FIFO的串口來減少接收中斷次數

Ben Eater's修改版時鐘模塊的資料分享

PCB電路的開發階段:使用仿真軟件可大幅度減少變更次數和成本

如何使用帶FIFO的串口來減少接收中斷次數

與設計并行的DFM分析助力有效減少設計改版

如何減少PCB雜散電容的影響

如何使用硬件FIFO來減少接收中斷次數

DRC規則是指什么?怎樣使用DRC規則減少PCB改版次數呢?

是德科技如何助力減少PCB改版次數

是德科技如何助力減少PCB改版次數

評論