在萬物互聯的智能時代,國產軟硬件技術的突破正成為推動產業升級的核心動力。RT-Thread Smart(簡稱: RT-Smart)操作系統與嘉楠科技K230芯片的深度融合,為AI邊緣計算領域帶來了一站式國產化解決方案,以“快速啟動、高效AI加速、安全可靠”等特性,重新定義了智能終端開發的邊界。

一、國產芯+國產系統:自主可控的AI底座

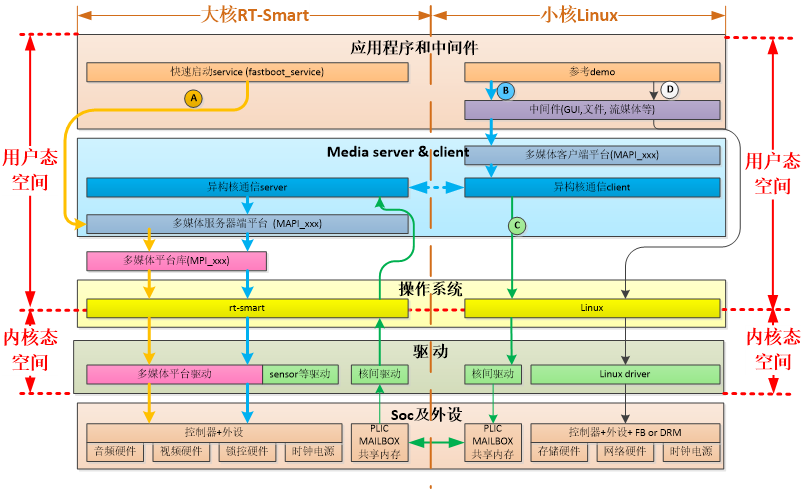

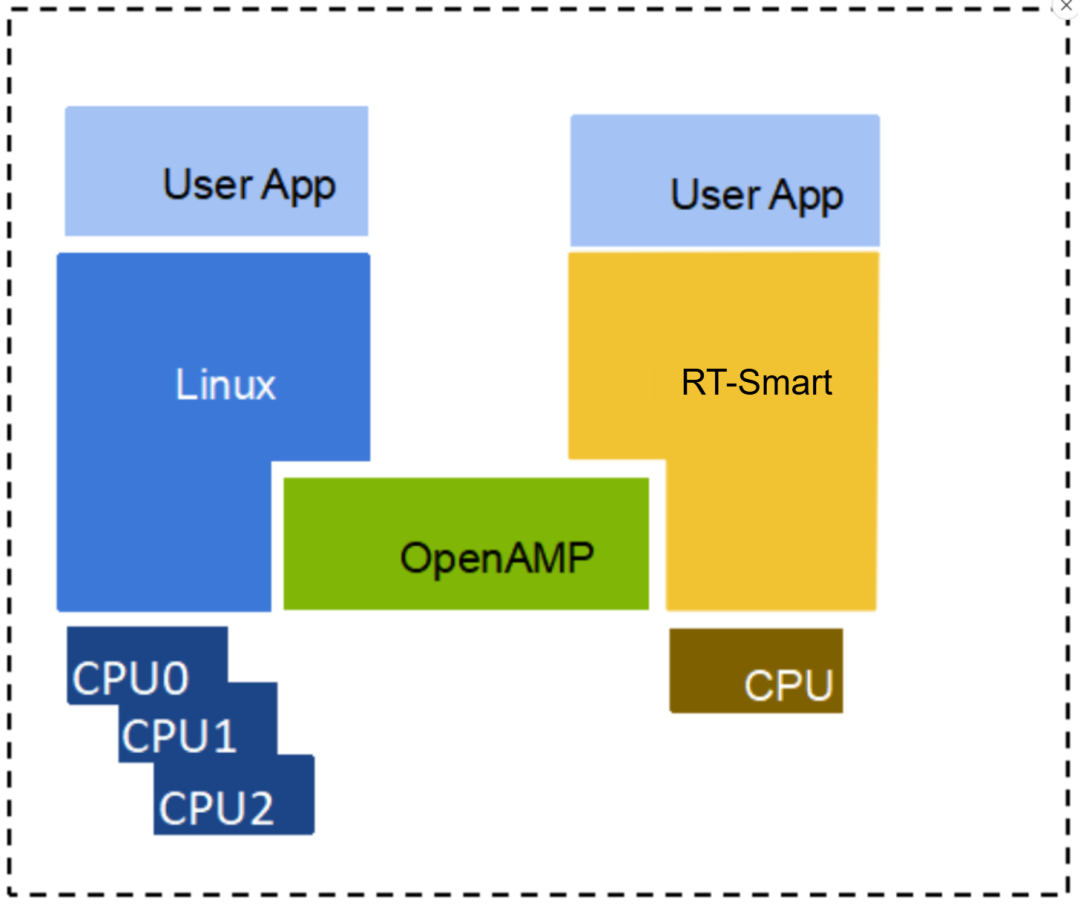

K230芯片作為國產RISC-V架構的高性能AIOT芯片,內置神經網絡加速器(KPU),支持多種AI計算,為圖像識別、語音處理等場景提供強大的算力支撐。RT-Thread Smart憑借其混合架構設計(用戶態與內核態分離),既保障了系統安全性,又通過POSIX接口全兼容特性無縫對接應用態的AI算法框架,實現算法快速移植與部署。

二、智能加速:AI算法與K230NPU的完美協同

在K230芯片的神經網絡加速器加持下RT-Thread Smart實現了AI推理性能的飛躍。通過優化的驅動框架,系統可直接調用K230的硬件加速單元,將AI算法的推理時延降低至毫秒級。例如,在安防攝像頭場景中,使用YOLO算法,系統可實時分析視頻流,精準識別人員、車輛等目標,同時保持300毫秒內快速啟動的特性,滿足應急響應需求。此外,RT-Thread Smart支持OpenCV、MicroPython等開源庫,開發者可結合K230的算力,靈活調用預置算法或自定義模型。

三、極致體驗: RT-Smart多核架構優化與特性

RT-Smart版本 針對 K230/K230D 多核架構進行了深度優化,充分發揮其硬件性能優勢,主要特性包括:

實時性保障機制: 支持Vector指令集向量擴展。RVV的引入為處理器提供了向量處理和并行計算的能力,可以加速各種應用,如圖像處理、信號處理、機器學習、科學計算等,滿足嚴苛的實時性要求。

安全可靠用戶態環境:RT-Smart支持用戶態應用,支持將系統的大部分系統組件及驅動移到內核之外,以一個個單獨的服務進程運行。

完整POSIX接口規范:RT-Smart 在用戶態完整兼容PSE53 API標準:對多進程進行支持,包括fork,vfork,完整的網絡支持,具備標準的Socket Abstraction Layer(SAL),并支持UNIX套接字,netlink等;支持POSIX Signal,threads等。

豐富的軟件組件生態: RT-Smart 集成針對大容量存儲設備提供掉電的安全文件系統,在任何異常掉電情況下,保證文件系統完整無損,支持 littleFs, FatFs, RomFs, RamFs 等文件系統,助力開發者快速構建功能豐富的嵌入式應用。

高效的多核間通信機制: RT-Smart 對多核間性能深度優化,每個核的重啟不會影響到其他核的任務運行;針對在進行一些系統操作時會對其他核造成的抖動問題進行了深度優化。

RT-Smart基于 K230/K230D 多核 RISC-V 處理器構建的高性能實時操作系統,為嵌入式系統開發提供了強大的軟件平臺。該解決方案充分利用了 K230/K230D 的硬件優勢,并結合 RT-Smart 的軟件特性,能夠滿足物聯網、邊緣計算和人工智能等領域對實時性、性能和能效的嚴苛要求。

-

嵌入式操作系統

+關注

關注

1文章

121瀏覽量

31866 -

RT-Thread

+關注

關注

32文章

1368瀏覽量

41499 -

RISC-V

+關注

關注

46文章

2477瀏覽量

48247

發布評論請先 登錄

嘉楠科技勘智K230D芯片賦能正點原子K230D BOX開發板

【AI開發板】正點原子K230D BOX開發板來了!一款性能強悍且小巧便攜的AI開發板!

RT-Thread操作系統應用開發寒假師資培訓

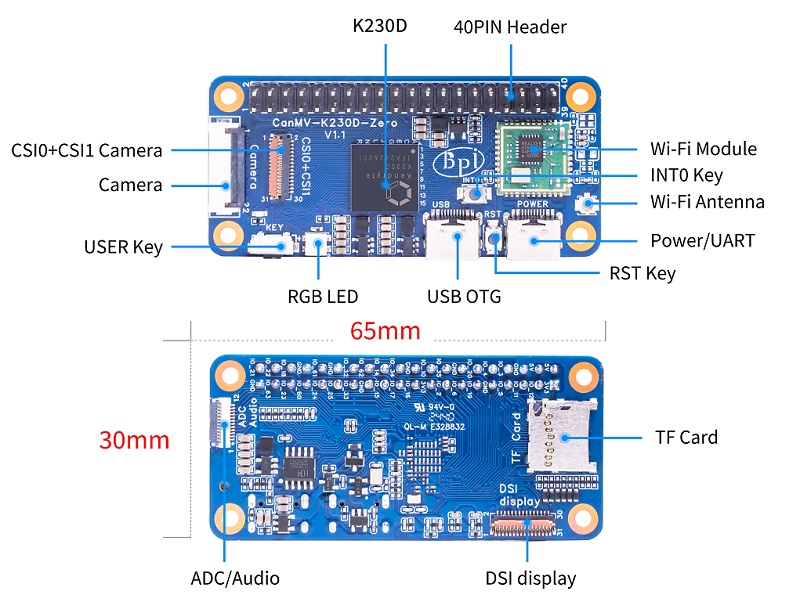

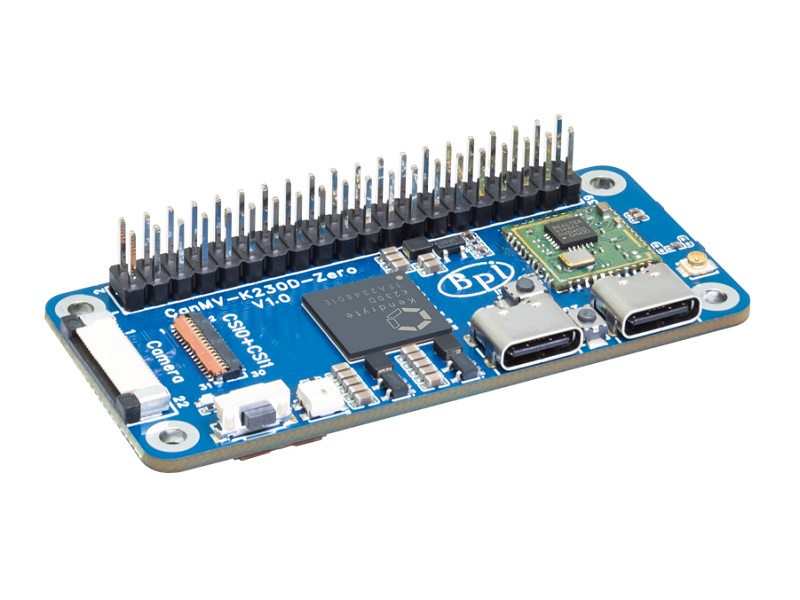

Banana Pi BPI-CanMV-K230D-Zero :AIoT 應用的 Kendryte K230D RISC-V

RT-Thread聯合河北大學發起嵌入式操作系統專業班-保定站

香蕉派開發板BPI-CanMV-K230D-Zero 嘉楠科技 RISC-V開發板公開發售

香蕉派開發板BPI-CanMV-K230D-Zero 嘉楠科技 RISC-V開發板公開發售

多核RISC-V處理器供應商超睿科技全力支持RT-Thread Smart,共同賦能“大芯片”生態

新書發布——《RT-Thread嵌入式實時操作系統內核、驅動和應用開發技術》

RT-Thread Safety AUTO成功適配芯來RISC-V車規內核

嘉楠科技發布K230D芯片,強化AIoT領域高性能計算

RT-Thread出席第六屆中國嵌入式技術大會,共話嵌入式操作系統與智能工業

香蕉派 BPI-CanMV-K230D-Zero 采用嘉楠科技 K230D RISC-V芯片設計

Banana Pi BPI-CanMV-K230D-Zero 采用嘉楠科技 K230D RISC-V芯片設計

RT-Thread Smart攜手K230/K230D打造多核RISC-V高性能嵌入式操作系統

RT-Thread Smart攜手K230/K230D打造多核RISC-V高性能嵌入式操作系統

評論