來源:OpenFPGA

在現代技術發展的浪潮中,開源項目已經成為了推動技術創新和發展的核心力量。無論是人工智能、區塊鏈、云計算,還是傳統的嵌入式開發、操作系統,開源項目都在其中扮演著至關重要的角色。它們不僅促進了技術的快速迭代,也為全球開發者提供了一個共享和合作的平臺。

相對來說,FPGA領域的開源項目目前還沒有能改變整個行業的開源項目(促進行業發展,提升行業的知名度),目前我覺得Yosys或Verilator有一些“勢頭”。同時,有些開源項目建立之初就是為了這個目的,但是能不能成為你心目中的“燈塔”,就需要越來越多的工程師參與進去。今天給大家帶來一個開源項目-Open Logic。

鏈接

https://github.com/open-logic/open-logic

愿景

像stdlib致力于為 C/C++ 項目服務一樣,Open Logic旨在為 HDL 項目服務。

Open Logic可以重復使用、獨立于供應商/工具的方式實現常用組件,并根據寬松的開源許可證(針對 FPGA 使用修改的 LGPL,請參閱License.txt)提供源碼,因此代碼可用于商業項目(大大的贊)。

Open Logic雖然是用 VHDL 編寫的,但 System Verilog 也可以輕松調用。

介紹

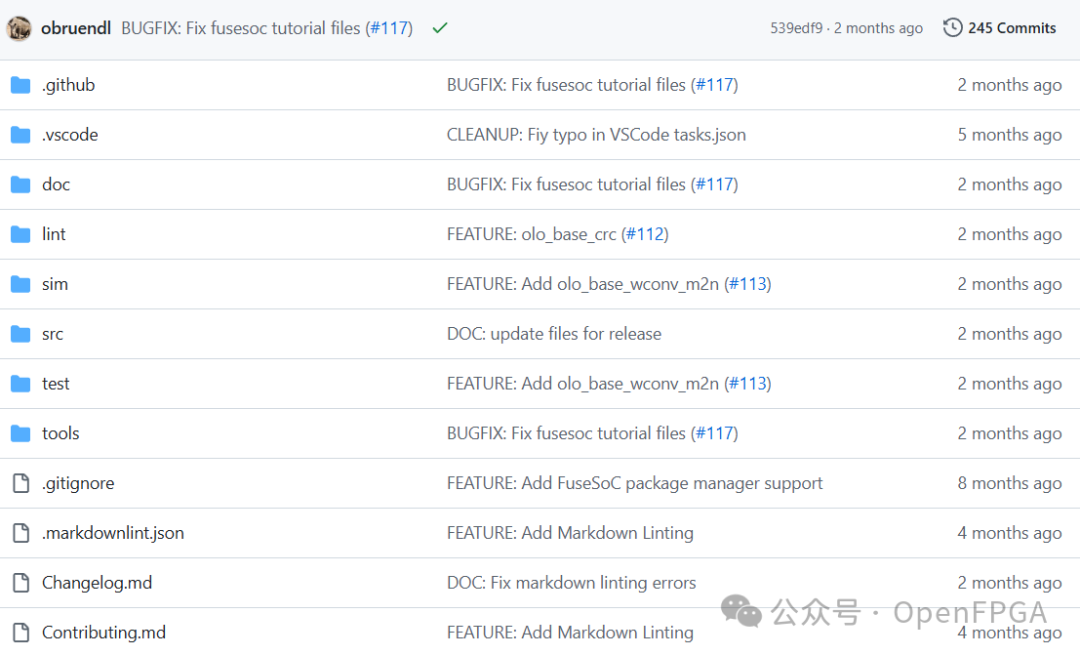

Open Logic 由Oliver Bründler創建,Oliver 將模塊分為三個不同的組:base模塊、AXI 模塊和intf(接口)模塊。base文件夾包含一些基本和非基本邏輯操作的模塊,從 FIFO 存儲器或解碼器到跨時鐘域同步器。在intf模塊中,可以找到與 SPI 或 UART 等接口相關的模塊。最后,AXI包含從 AXI 從屬模塊到 AXI 主模塊。

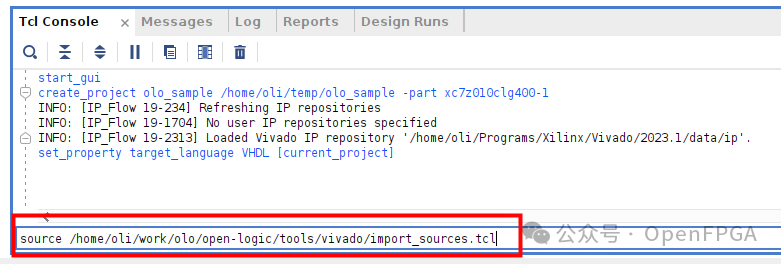

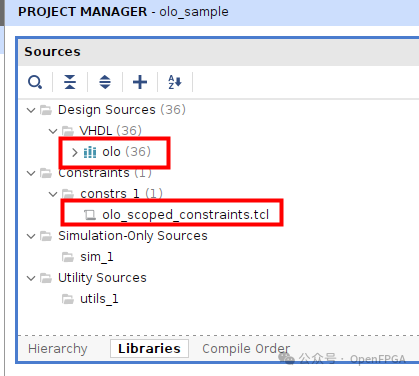

為了在 FPGA 設計中使用這些模塊,該項目包含一組與 FPGA 供應商的 IDE 工具兼容的腳本,這些腳本將庫添加到項目中olo_,其中包含 Open Logic 項目中可用的所有模塊。

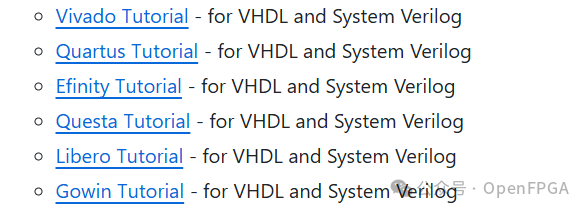

詳細的使用步驟,項目里都有詳細的使用鏈接:

按照自己使用的EDA工具,查看使用教程即可(easy、easy、easy...)

總結

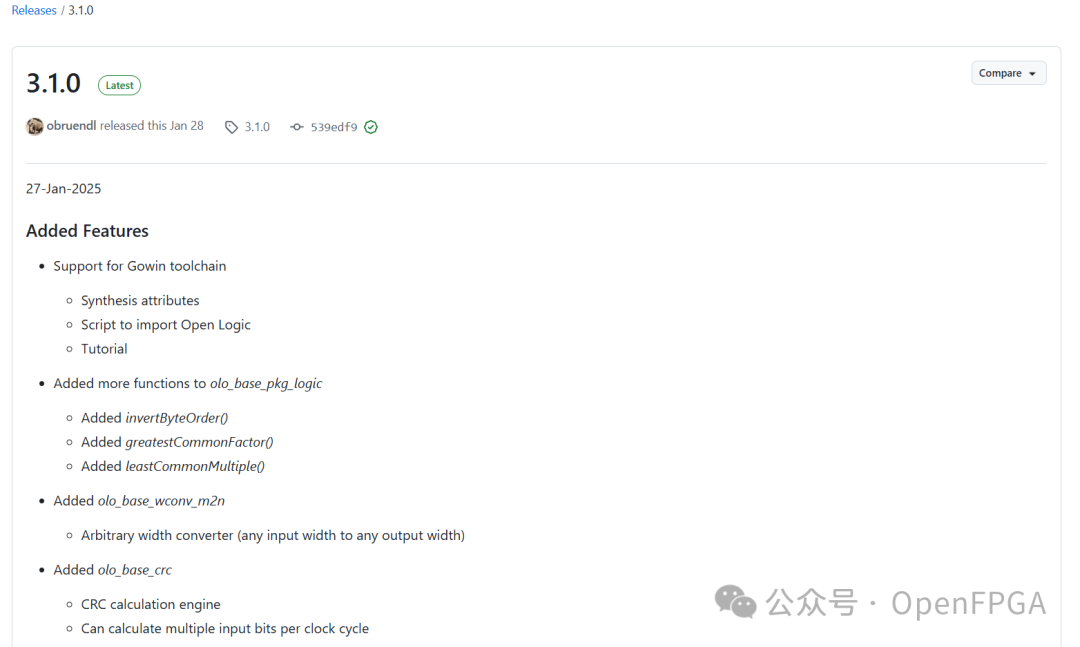

今天介紹的項目還在“茁壯”成長,目前最新的版本3.1.0,幾乎每個月都在增長,增加了對 Gowin EDA 以及新模塊的支持。

FPGA 開源生態系統與其他開源社區相差甚遠,但它正在突飛猛進,需要每個FPGA工程師努力去維護,即使提一個小小的BUG也是對該類項目重大的貢獻。

-

FPGA

+關注

關注

1646文章

22059瀏覽量

619152 -

嵌入式

+關注

關注

5153文章

19708瀏覽量

318076 -

操作系統

+關注

關注

37文章

7163瀏覽量

125728 -

開源

+關注

關注

3文章

3714瀏覽量

43901

原文標題:FPGA標準庫-Open Logic

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

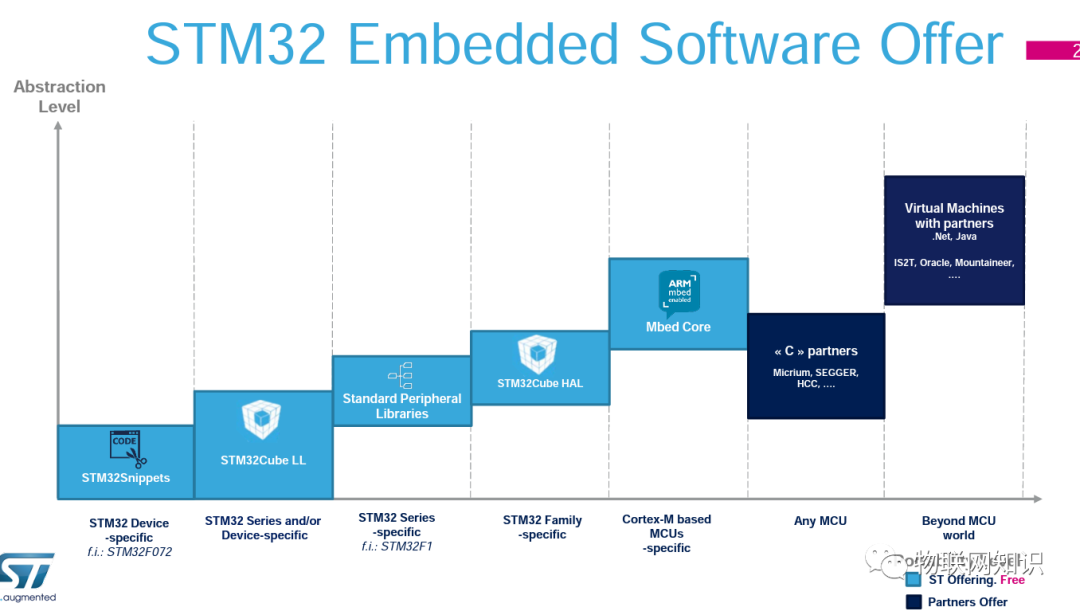

STM32標準庫、HAL庫和LL庫介紹

FPGA標準庫Open Logic介紹

FPGA標準庫Open Logic介紹

評論