隨著通訊速度的提升,出現(xiàn)了很多差分傳輸接口,以提升性能,降低電源功耗和成本。早期的技術(shù),諸如emitter-coupled logic(ECL),使用不變的負(fù)電源供電,在當(dāng)時(shí)用以提升噪聲抑制。隨著正電壓供電技術(shù)發(fā)展,諸如TTL和CMOS技術(shù),原先的技術(shù)優(yōu)點(diǎn)開(kāi)始消失,因?yàn)樗麄冃枰恍?5.2V或-4.5V的電平。

在這種背景下,ECL轉(zhuǎn)變?yōu)閜ositive/pseduo emitter-coupled logic (PECL),簡(jiǎn)化了板級(jí)布線,摒棄了負(fù)電平供電。PECL要求提供800mV的電壓擺幅,并且使用5V對(duì)地的電壓。LVPECL類(lèi)似于PECL也就是3.3V供電,其在電源功耗上有著優(yōu)點(diǎn)。

當(dāng)越來(lái)越多的設(shè)計(jì)采用以CMOS為基礎(chǔ)的技術(shù),新的高速驅(qū)動(dòng)電路開(kāi)始不斷涌現(xiàn),諸如current mode logic(CML),votage mode logic(VML),low-voltage differential signaling(LVDS)。這些不同的接口要求不同的電壓擺幅,在一個(gè)系統(tǒng)中他們之間的連接也需要不同的電路。

· 轉(zhuǎn)換原因?

1、?電平特性差異?

a)LVPECL電平的差分?jǐn)[幅較大(典型值約800mV),共模電壓較高(約1.3V-1.9V),需外部端接電阻匹配;而LVDS差分?jǐn)[幅較小(350mV),共模電壓較低(約1.2V),且LVDS接收端內(nèi)置端接電阻?。

b)直接連接可能導(dǎo)致LVDS接收端共模電壓超出范圍或信號(hào)幅度不足?。

2、?應(yīng)用場(chǎng)景需求?

a)LVPECL常用于高速時(shí)鐘或數(shù)據(jù)傳輸場(chǎng)景(如FPGA輸出),而LVDS因低功耗特性更適合長(zhǎng)距離或低功耗設(shè)計(jì)??。

b)不同器件間接口不兼容時(shí)需電平轉(zhuǎn)換(如FPGA輸出LVPECL,但接收端僅支持LVDS)?

· 轉(zhuǎn)換方式

1、直流耦合

LVPECL到LVDS 的直流耦合結(jié)構(gòu)需要一個(gè)電阻網(wǎng)絡(luò),如圖1.1中所示,設(shè)計(jì)該網(wǎng)絡(luò)時(shí)有這樣幾點(diǎn)必須考慮:首先,我們知道當(dāng)負(fù)載是50Ω接到Vcc-2V 時(shí),LVPECL 的輸出性能是最優(yōu)的,因此我們考慮該電阻網(wǎng)絡(luò)應(yīng)該與最優(yōu)負(fù)載等效;然后我們還要考慮該電阻網(wǎng)絡(luò)引入的衰減不應(yīng)太大,LVPECL 輸出信號(hào)經(jīng)衰減后仍能落在LVDS 的有效輸入范圍內(nèi)。注意LVDS 的輸入差分阻抗為100Ω,或者每個(gè)單端到虛擬地為50Ω,該阻抗不提供直流通路,這里意味著LVDS輸入交流阻抗與直流阻抗不等.經(jīng)計(jì)算,電阻值為:R1=182Ω,R2=48Ω,R3=48Ω。電阻靠近接收側(cè)放置。

(a)等效電路 (b)LVPECL到LVDS的連接

圖1.LVPECL到LVDS的直流耦合結(jié)構(gòu)

2、交流耦合

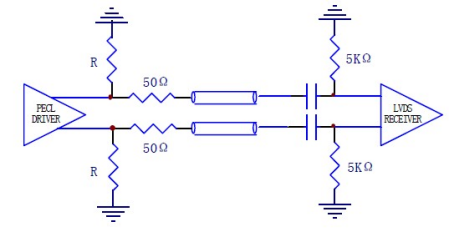

LVPECL 到LVDS 的交流耦合結(jié)構(gòu)如圖2 所示,LVPECL 的輸出端到地需加直流偏置電阻(142Ω到200Ω),同時(shí)信號(hào)通道上一定要串接50Ω電阻,以提供一定衰減。LVDS 的輸入端到地需加5KΩ電阻,以提供近似0.86V 的共模電壓。

圖2.LVPECL到LVDS的交流耦合結(jié)構(gòu)

在信號(hào)轉(zhuǎn)換方面,LVPECL到LVDS的轉(zhuǎn)換則需要考慮衰減電阻和交流耦合電容的放置,以及LVDS接收器的重新偏置。相反,LVDS到LVPECL的轉(zhuǎn)換也需要適當(dāng)?shù)?a target="_blank">電路設(shè)計(jì)和元件選擇。

LVDS和LVPECL各有其特點(diǎn)和應(yīng)用場(chǎng)景。LVDS適用于板內(nèi)信號(hào)傳輸和高速變化信號(hào)的傳輸,而LVPECL則適用于背板傳輸和長(zhǎng)線纜傳輸?shù)刃枰獜?qiáng)驅(qū)動(dòng)能力和高傳輸速度的應(yīng)用。不過(guò),雖然LVPECL到LVDS的轉(zhuǎn)換可以通過(guò)電路的設(shè)計(jì)可以實(shí)現(xiàn),這邊建議客戶盡量選用相同類(lèi)型波形的差分傳輸接口,畢竟電路轉(zhuǎn)換會(huì)有很多其他不確定的影響。

-

晶振

+關(guān)注

關(guān)注

34文章

3167瀏覽量

69384 -

lvds

+關(guān)注

關(guān)注

2文章

1078瀏覽量

66959 -

LVPECL

+關(guān)注

關(guān)注

2文章

34瀏覽量

18210 -

揚(yáng)興科技

+關(guān)注

關(guān)注

1文章

144瀏覽量

2837 -

差分晶振

+關(guān)注

關(guān)注

0文章

119瀏覽量

393

發(fā)布評(píng)論請(qǐng)先 登錄

淺談LVDS、CML、LVPECL三種差分邏輯電平之間的互連

SiTime差分晶振的LVDS、LVPECL、HCSL、CML模式相互轉(zhuǎn)換過(guò)程介紹

差分晶振-LVPECL到LVDS的連接

差分晶振-LVPECL到LVDS的連接

評(píng)論