概 述

HPMicro MCU的TRIGMUX具有濾波功能,為部分輸入信號提供了數字濾波器,支持濾刺模式、延時模式、濾峰模式和濾谷模式。但這濾波器僅針對外部從引腳的輸入信號,不能對內部的信號進行濾波。

為了解決這一問題,本組件使用PLB實現了濾波器,同樣支持濾刺模式、延時模式、濾峰模式和濾谷模式,通過配置TRIGMUX,既能夠對外部引腳輸入信號進行濾波,又能夠對能夠連接到TRIGMUX的信號進行濾波。

濾波器設計介紹

!

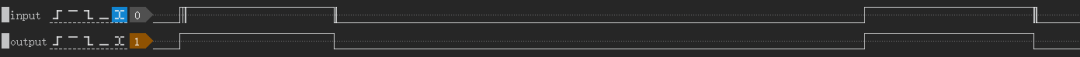

濾刺模式(Rapid Change Mode)

濾波器輸入翻轉后,輸出也會立即翻轉,之后會在一定時間內無視濾波器的輸入。這個模式下,濾波器輸出會緊隨輸入,同時會避免輸出信號出現毛刺。

概要設計

- 該設計分為2級,第1級為TYPE_B邏輯單元(輸出OUT0作為鎖存信號),第2級為TYPE_A邏輯單元。

-TYPE_B的設計

?原始信號的邊沿信號作為PLB TYPE_B邏輯單元的輸入信號IN0;?PLB輸出信號為OUT0,同時作為PLB TYPE_B邏輯單元的輸入信號IN1;?PLB輸出信號為OUT1,同時作為PLB TYPE_B邏輯單元的輸入信號IN2;?定義真值表如下:

| IN2 | IN1 | IN0 | Operation |

|---|---|---|---|

| 0 | 0 | 0 | cnt值保持不變 |

| 0 | 0 | 1 | cnt值加1 |

| 0 | 1 | 0 | cnt值加1 |

| 0 | 1 | 1 | cnt值加1 |

| 1 | x | x | cnt值從cmp0中獲取,cmp0的值為0 |

?OUT0的輸出邏輯為:cnt值跟cmp0相比較,當cnt值大于cmp0時,out0輸出為1,否則為0。?OUT1的輸出邏輯為:cnt值跟cmp1相比較,當cnt值大于等于cmp1時,out1輸出為1,否則為0。cmp1的數值可設置,就是用戶需要定義的延時時間,單位為 plb clock tick;?cnt初始值為0。

-TYPE_A的設計

?原始信號作為PLB TYPE_A邏輯單元的輸入信號IN0;?原始信號的邊沿信號作為PLB TYPE_A邏輯單元的輸入信號IN1;?TYPE_B邏輯單元的輸出信號OUT0作為TYPE_A邏輯單元的輸入信號IN2;?TYPE_A邏輯單元的輸出信號OUT0作為TYPE_A邏輯單元的輸入信號IN3;?定義真值表如下:

| IN3 | IN2 | IN1 | IN0 | Out0 |

|---|---|---|---|---|

| 0 | 0 | x | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 1 | 1 | x | x | 1 |

| 1 | 0 | x | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 0 | 1 | x | x | 0 |

| 0 | 0 | 0 | 1 | 1 |

?OUT0即為濾波后的輸出信號。

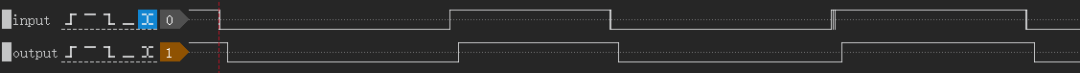

延時模式(Delay Mode)

濾波器輸入翻轉后需要保持一定時間,濾波器輸出才會翻轉。

概要設計

-原始信號作為PLB TYPE_B邏輯單元的輸入信號IN0,原始信號的邊沿信號作為PLB TYPE_B邏輯單元的輸入信號IN2;

-PLB輸出信號為OUT0,同時作為PLB TYPE_B邏輯單元的輸入信號IN1;

-定義真值表如下:

| IN2 | IN1 | IN0 | Operation | 備注 |

|---|---|---|---|---|

| 0 | 0 | 0 | cnt值保持不變 | 穩定態 |

| 0 | 0 | 1 | cnt值加1 | |

| 0 | 1 | 0 | cnt值減1 | |

| 0 | 1 | 1 | cnt值保持不變 | 穩定態 |

| 1 | 0 | 0 | cnt值加1 | 信號抖動 |

| 1 | 0 | 1 | cnt值從cmp1中獲取,cmp1的值為0 | 上升沿 |

| 1 | 1 | 0 | cnt值從cmp2中獲取,cmp2的值為2*cmp0 | 下降沿 |

| 1 | 1 | 1 | cnt值減1 | 信號抖動 |

-OUT0的輸出邏輯為:cnt值跟cmp0相比較,當cnt值大于等于cmp0時,out0輸出為1,否則為0。cmp0的數值可設置,就是用戶需要定義的延時時間,單位為 plb clock tick;

-cnt初始值為0;

-OUT0即為濾波后的輸出信號。

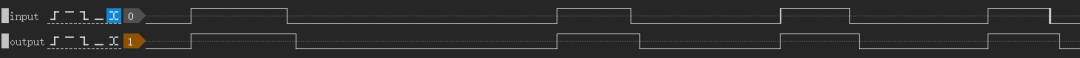

濾峰模式(Stable Low Mode)

濾波器輸入置邏輯0后,需要保持一定時間,濾波器輸出才會置邏輯0,而濾波器輸入置1,濾波器輸出會立即置1。

概要設計

-原始信號作為PLB TYPE_B邏輯單元的輸入信號IN0;

-PLB輸出信號為OUT0,同時作為PLB TYPE_B邏輯單元的輸入信號IN1;

-定義真值表如下:

| IN1 | IN0 | Operation |

|---|---|---|

| x | 1 | cnt值從cmp1中獲取,cmp1的值為0 |

| 1 | 0 | cnt值加1 |

| 0 | 0 | cnt值保持不變 |

-OUT0的輸出邏輯為:cnt值跟cmp0相比較,當cnt值小于cmp0時,out0輸出為1,否則為0。cmp0的數值可設置,就是用戶需要定義的延時時間,單位為 plb clock tick;

-cnt初始值為cmp0;

-OUT0即為濾波后的輸出信號。

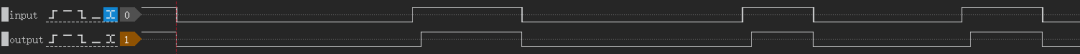

濾谷模式(Stable High Mode)

濾波器輸入置邏輯1后,需要保持一定時間,濾波器輸出才會置邏輯1,而濾波器輸入置0,濾波器輸出會立即置0。

概要設計

-原始信號作為PLB TYPE_B邏輯單元的輸入信號IN0;

-PLB輸出信號為OUT0,同時作為PLB TYPE_B邏輯單元的輸入信號IN1;

-定義真值表如下:

| IN1 | IN0 | Operation |

|---|---|---|

| x | 0 | cnt值從cmp1中獲取,cmp1的值為0 |

| 0 | 1 | cnt值加1 |

| 1 | 1 | cnt值保持不變 |

-OUT0的輸出邏輯為:cnt值跟cmp0相比較,當cnt值大于等于cmp0時,out0輸出為1,否則為0。cmp0的數值可設置,就是用戶需要定義的延時時間,單位為 plb clock tick;

-cnt初始值為0;

-OUT0即為濾波后的輸出信號。

使用介紹

!

在應用程序中的CMakeLists.txt中添加如下內容,使能PLB濾波器組件:

set(CONFIG_HPM_PLB_FILTER 1)

應用程序調用如下API進行配置:

voidplb_filter_init(filter_config_t*cfg)

具體可參考 hpm_sdk/samples/drivers/plb/filteroutput 示例

以上內容來自:https://kb.hpmicro.com/2024/12/27/plb實現濾波器/

先楫社區堅持開源共享、互惠互利,貼近每一個開發者,一步一個腳印,一點一滴積累,為成為更好的我們而不斷努力。

心之所向,銳意進取,星辰大海,恣意成長。

-

mcu

+關注

關注

146文章

17824瀏覽量

360241 -

濾波器

+關注

關注

162文章

8065瀏覽量

180990 -

PLB

+關注

關注

0文章

5瀏覽量

9424

發布評論請先 登錄

fir濾波器的設計和實現

有源濾波器中數字低通濾波器的設計及其DSP實現

基于Matlab的FIR帶通濾波器設計與實現

詳細解析濾波器的定義,濾波器的特性,濾波器的工作原理,濾波器的分類,濾波器的典型電路原理圖

FIR濾波器的FPGA設計與實現

高斯濾波器的原理和實現

開年干貨來襲:PLB實現濾波器

開年干貨來襲:PLB實現濾波器

評論