1. JESD204B 基本協議

其實使用到ADI的東西,基本也就沒有太去關注協議這些東西,只是簡簡單單的有個了解就行,在實際調試的時候,用的也是Xilinx的評估版的JESD的IP,基本不需要自己做什么工作就能夠把整個系統運行起來了。

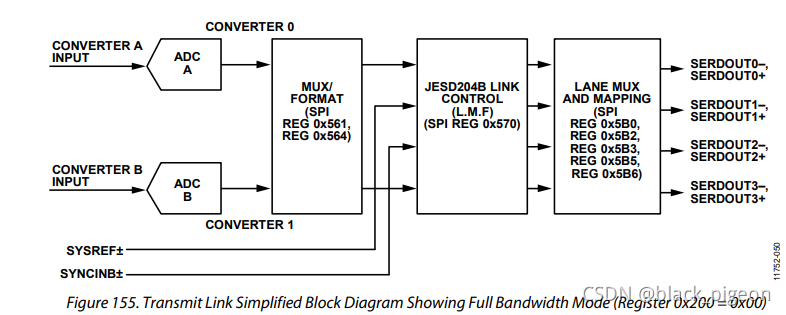

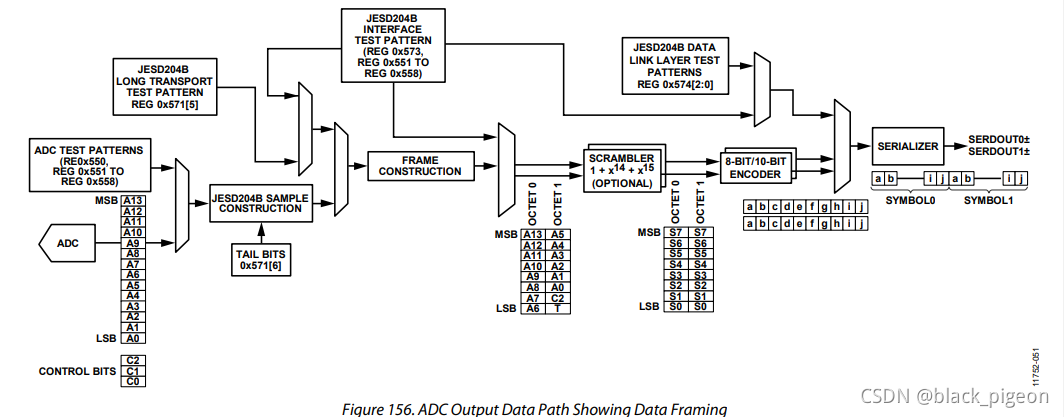

下面這個圖是AD9680的一個基本的結構框圖,可以看到這個ADC的作用就對輸入的信號進行采集量化,在JESD204B鏈路建立之后,按照特定的格式組成數據幀,然后將數據幀通過JESD的接口將數據發送到FPGA上。其實基于JESD 204B的ADC和DAC在使用的時候,只需要去弄清楚鏈路是如何建立的就基本宣告JESD的驅動成功了。

1.1 JESD204B鏈路參數

在JESD 204B的鏈路建立的過程中,最重要就是需要去關注鏈路所需要的參數,這些參數是后面對FPGA當中JESD IP的配置和對AD9680配置十分重要的,JESD IP的手冊可以參考PG066和PG198這兩個手冊。

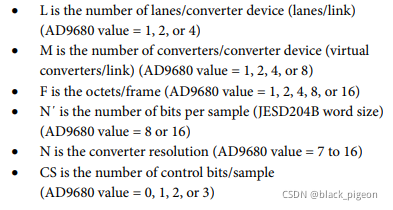

無論是JESD的發送還是接收,關于鏈路建立的關鍵參數都是一致的,如下面從AD9680的手冊當中截取出來的一些參數。

通過這些參數能夠確定JESD鏈路當中所需要使用到的LANE的數量,JESD該如何來進行組幀,組成的數據幀當中哪些位是數據位哪些位是控制位,組成的數據幀是對應哪一個ADC當中的哪一個轉換器的。舉個基于AD9680和FPGA進行全帶寬傳輸的簡單的例子,

L=4,M=2,F=2, N’=16, N=14, CS=2, K=32對應到JESD的鏈路當中就是

L=4需要4個lane來建立JESD 204鏈路,從FPGA角度來看就是需要使用到4個高速收發器接口。

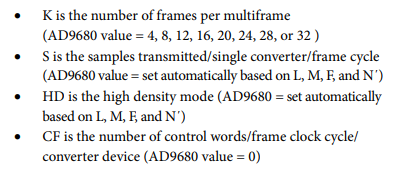

M=2產生ADC數據的數據來源有兩個,如下面的圖中所示

N’=16表示一個采樣點中包含16bit數據,N=14表示ADC的采樣精度為14bit,CS=2表示在傳輸JESD的數據的時候有兩位的控制位,這樣就能夠很好地理解N’,N和CS的關系了。一般情況下一個采樣點包含了具體的數據和控制位。

F=2表示一個數據幀當中有兩個字節的數據,這兩個字節剛好能夠表示一個采樣點。

K=32表示一個多幀當中有32個數據幀,通過前面的F參數,不難計算出一個多幀包含有64個字節的數據。

上面只是一個對JESD鏈路當中參數的一個簡單的介紹,在實際的使用的時候,就是多看手冊,弄清楚每個參數在具體的應用當中的作用就OK了。

下圖是一個ADC采樣點經采樣后從傳輸層經過數據鏈路層,最終經過物理層進行傳輸的過程,在這個過程中,可以看到在具體的數據幀黨總,上面介紹的一些關鍵的參數的具體的表現形式。

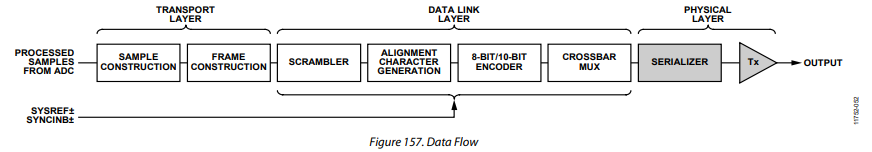

1.2 JESD 204B的分層

就像學習以太網的時候,要先了解一下OSI的涉及參考模型一樣,在JESD當中,也有一個參考的數據分層的物理模型,下圖所示的就是一個簡單的JESD 204B的分層。主要有三個層級,分別是傳輸層,數據鏈路層和物理層。

傳輸層:傳輸層負責將庶幾乎打包映射到有字節組成的JESD204B數據幀當中。傳輸層的映射關系是由鏈路層的設置的參數來決定的。

數據鏈路層:數據鏈路層負責數據傳輸的底層的功能,這些功能包括對數據進行加擾,插入用于多芯片同步,通道對齊等控制字符,完成8B10B轉換,發送初始通道對齊序列(ILAS)等。ILAS是一個比較重要的序列,這個序列當中包含了鏈路的一些信息,在接收方當中,可以通過這個序列來知道當前鏈路的一個配置的狀態。

物理層:物理層就是負責將數據進行傳輸的層,在我這里也就是指的FPGA和AD9680之間具體的高速接口了。

1.3 鏈路建立的過程

在我進行JESD204B的調試過程中,我認為最重要的一步就是鏈路建立的過程,只要能夠正確地建立起JESD204B鏈路的link,那么后續的工作就比較簡單了。因此首先需要弄清楚鏈路建立的一個過程。

在JESD204B subclass1中鏈路的建立主要包含一下幾個步驟:

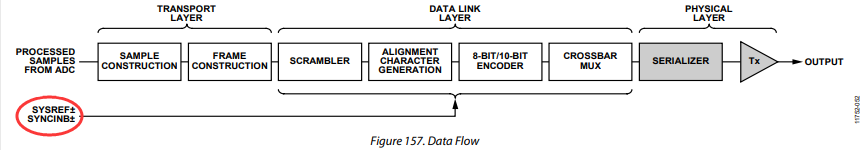

Code Group Synchronization (CGS) and SYNCINB±

Initial Lane Alignment Sequence (ILAS)

User Data and Error Detection

1.3.1 CGS & SYNC

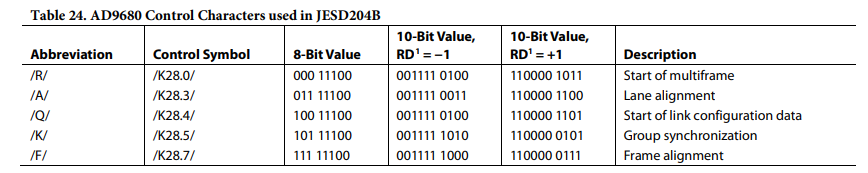

在CSG階段,簡而言之就是一個同步的階段,如果對Xilinx的高速接口有一定的了解的話,就知道高速接口當中是如何實現數據和時鐘的恢復和數據的對齊的,在CSG階段,JESD的發送器會不停的發送/K28.5/字符。在JESD的接收器當中,就會根據所接收到的數據來檢測是否接收到了/K28.5/字符,如果檢測到了,就會使SYNC信號拉高,從而提示JESD發送器,當前已經檢測到了/K28.5/也即已經同步上了。

這里需要提一下SYNC信號,在前面數據鏈路層當中,我們可以在數據鏈路層當中,有兩個用于控制數據鏈路層的信號,分別是sysref和sync。JESD204B子類1是否同步上,跟這兩個信號有著很緊密的關系。

舉個簡單的例子,ADC 轉換器AD9680作為JESD的發送方,FPGA作為JESD的接收方,兩者一個共同的參考信號sysref,鏈路是否建立是根據LMFC與sysref共同來決定的,作為數據的接收方,FPGA若成功檢測到當前已經同步上,需要拉高sync,告訴AD9680當前FPGA已經能夠同步了,數據的發送方才會進行下一步的操作。若sync一直不拉高,那么鏈路的建立將會一直處于CGS階段,在JESD當中也就只能接收到/K28.5/(0xBC).

JESD常用的字符如下:

1.3.2 ILAS 階段

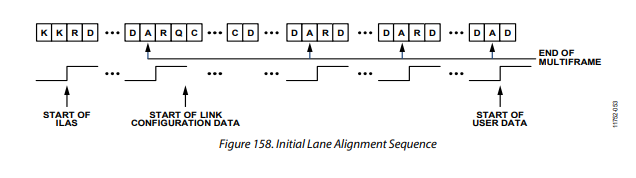

在這個階段當中,JESD的發送方,會發送JESD鏈路的配置信息。ILAS階段一般包含4個多幀。每個多幀以/R/字符表示開始,以/A/字符表示多幀結束。

在第一個多幀當中,填充的主要是0~255的遞增數。

在第二個多幀當中,以/R/字符表示開始,然后發送一個Q字符,用于表示開始發送鏈路配置數據,從第三個字符開始發送鏈路配置數據,鏈路配置數據一共14個字符,其余地方用遞增數進行填充。

第三個和第四個多幀,結構和第一個多幀一致。

1.3.3 用戶數據

在ILAS階段完成之后,就可以進行用戶數據傳輸了。這些東西在JESD的IP里面都已經集成地很好了,在使用IP地時候,能夠大大地減輕設計的難度。

-

接口

+關注

關注

33文章

9000瀏覽量

153715 -

dac

+關注

關注

44文章

2409瀏覽量

193687 -

鏈路

+關注

關注

1文章

76瀏覽量

14253 -

JESD204B

+關注

關注

6文章

82瀏覽量

19585

原文標題:JESD204B接口簡介

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

jesd204b

JESD204B的系統級優勢

JESD204B串行接口時鐘的優勢

JESD204B協議有什么特點?

JESD204B協議介紹

JESD204B的優勢

JESD204B協議概述

JESD204B SystemC module 設計簡介(一)

JESD204B標準及演進歷程

JESD204B使用說明

一文詳解JESD204B協議

一文詳解JESD204B協議

評論