隨著市場對嵌入式設備的功能需求越來越高,集成了嵌入式處理器和實時處理器的主控方案日益增多,以便更好地平衡性能與效率——實時核負責高實時性任務,A核處理復雜任務,兩核間需實時交換數據。然而在數據傳輸方面,傳統串行接口盡管成本較低,但其傳輸速率相對較慢;反之,并行接口雖然傳輸速度快,但成本卻比較高。因此,單芯片多核異構處理器就成為能夠滿足需求的理想選擇。

RISC-V作為一種開源指令集架構,以其簡潔性、一致性、可擴展性以及高編譯效率,為實時性處理場景提供了強大的支持。將A核與RISC-V核結合作為單芯多核異構方案,可以有效利用RISC-V的這些優勢,實現高性能與高實時性的有效結合。

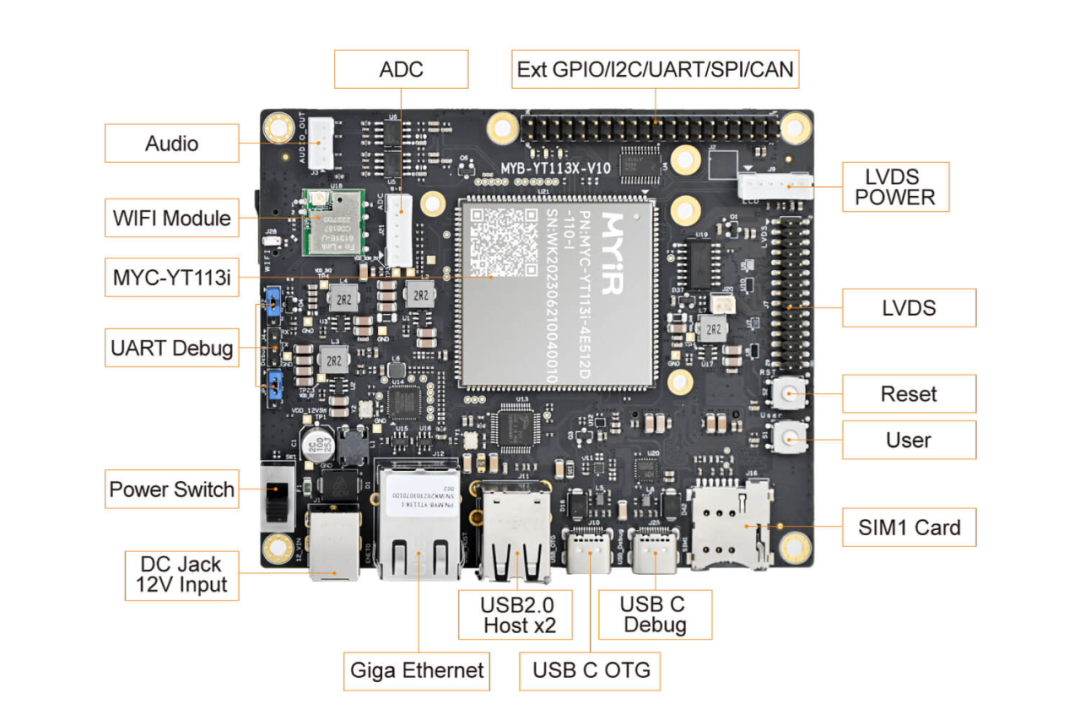

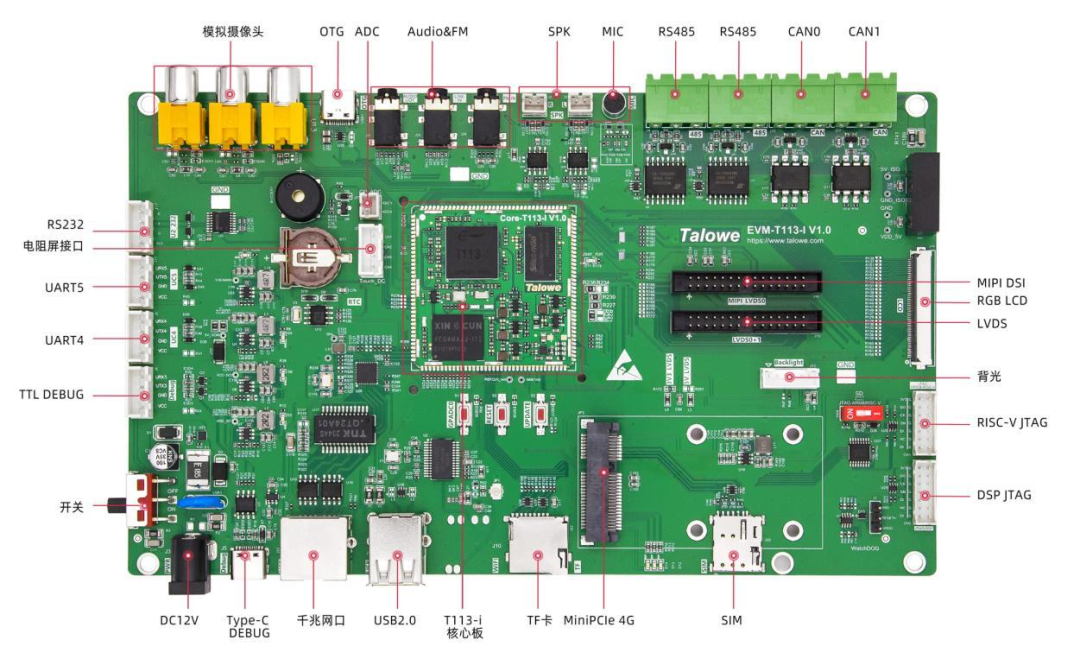

本文將以OK113i-S開發板為例,為大家介紹RISC-V核的資源和應用案例。

1、OK113i-S開發板的RISC-V核

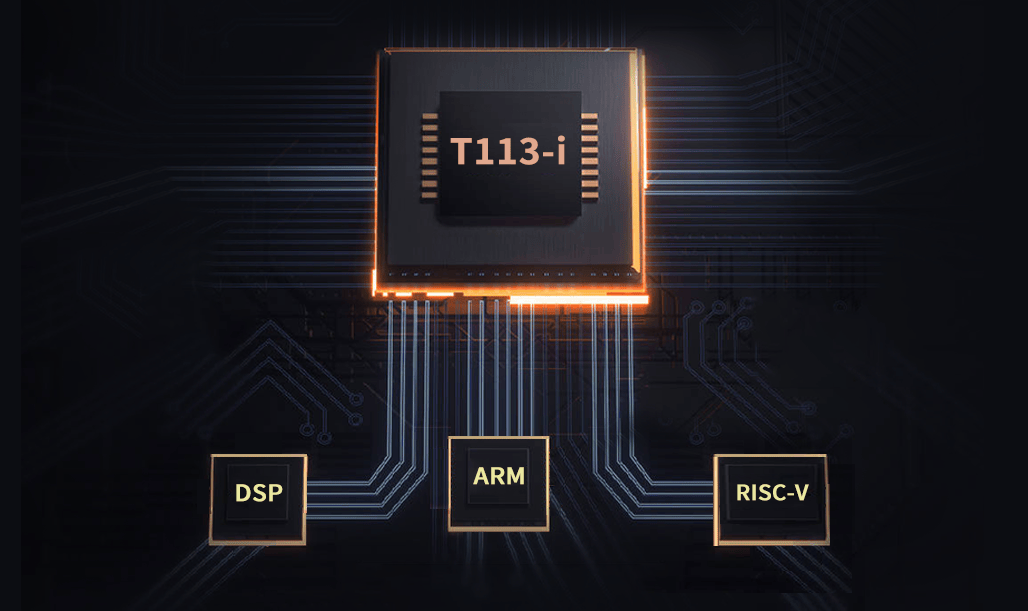

飛凌嵌入式OK113i-S開發板是一款基于全志T113-i工業級處理器開發的高性價比開發板,集成了雙核Cortex-A7 CPU、64位玄鐵C906 RISC-V和DSP,能夠提供高效的計算能力和性價比。尤為值得一提的是,其內置的RISC-V核心作為一款超高能效的實時處理器,主頻峰值可達1008MHz,并標準配備了內存管理單元,能夠流暢運行RTOS系統或裸機程序,進一步提升了應用靈活性。

1.1 RISC-V核的特性

(1) 最高主頻可達1008MHz;

(2) 32KB指令緩存;

(3) 32KB數據緩存;

(4) 可運行于超大容量的DDR

... ...

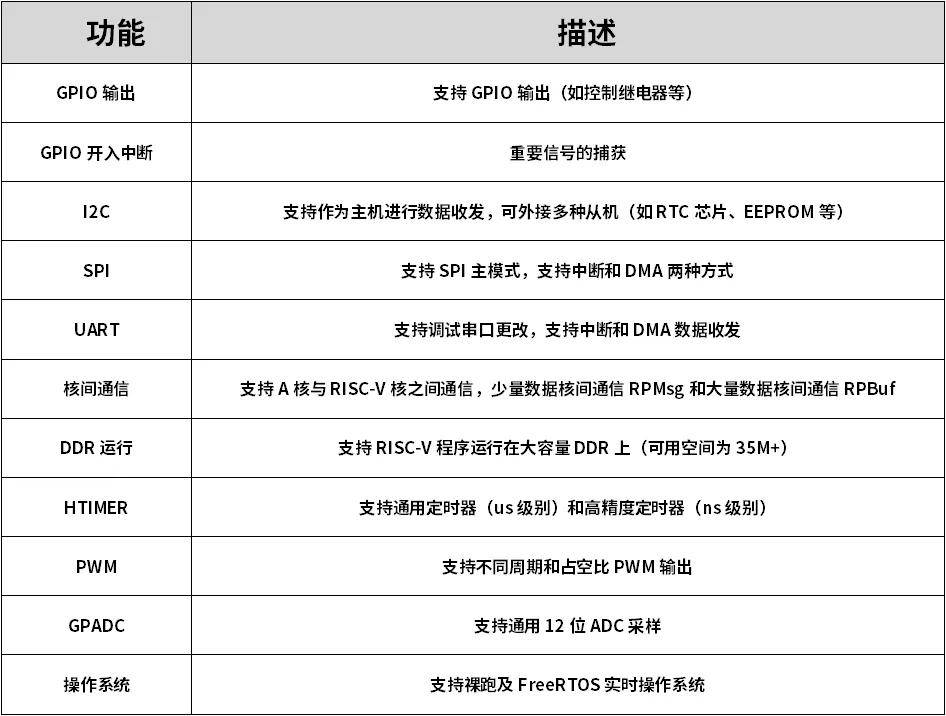

1.2 RISC-V核的接口資源

2、應用實例

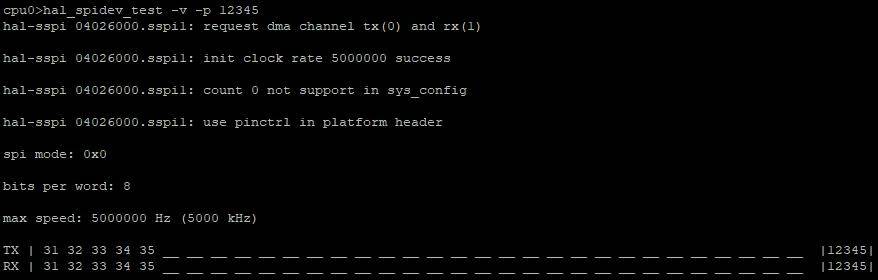

2.1 SPI數據收發

本案例為SPI回環測試,即將SPI的MOSI和MISO兩個引腳短接進行數據收發。

(1) 功能介紹

(2) 效果實現

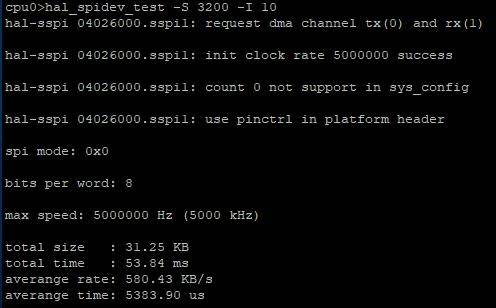

SPI發送和接收的FIFO均為64個,在底層hal庫程序中,當數據長度小于64字節時,采用中斷方式,當FIFO大于等于64字節時,采用DMA模式。

中斷方式傳輸效果:

DMA方式傳輸效果:

在DMA傳輸方式下,SPI速率默認為5Mbit/s,案例中平均傳輸速率為580.43KB/s,即4.6Mbit/s,接近理論值。

2.2 核間通信RPbuf

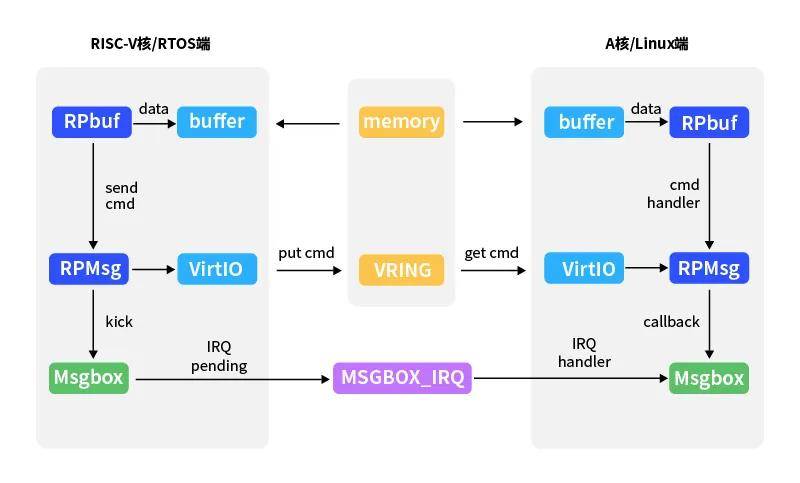

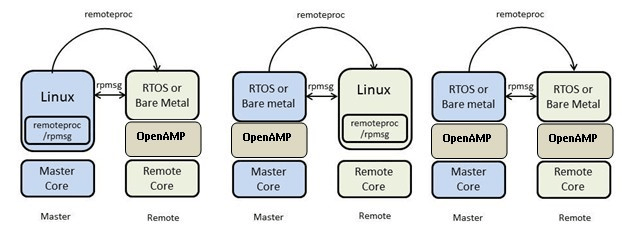

RPbuf是全志基于RPMsg所實現一套高帶寬數據傳輸的框架。RPMsg是基于共享內存和Msgbox中斷實現的一套核間通信機制,RPMsg除去頭部的16字節數據外,單次最多可發送496字節有效數據。因此,全志基于RPMsg實現了一套大數據量傳輸機制RPbuf,實現原理是在DDR中放置傳輸的數據,通過RPMsg傳輸DDR的地址和大小。我們以單次32KB數據傳輸為例進行展示。

(1) 功能介紹

? VirtIO:一套虛擬化數據傳輸框架,用于管理共享內存VRING;

? VRING:由VirtIO管理的一個環形共享內存;

? Msgbox:全志提供的一套消息中斷機制,已與linux內核中原生的mailbox框架適配;

? MSGBOX_IRQ:Msgbox中斷;

? RPMsg:基于VirtIO管理的共享內存所實現一套少量數據傳輸的框架;

? RPbuf:全志基于RPMsg所實現一套大量數據傳輸的框架。

由上圖可知(以RISC-V核向A核發送數據為例),RPbuf首先將數據放置在DDR中,再將緩沖區首地址和大小通過RPMsg發送至A核(RPMsg將緩沖區首地址和大小放入VRING,然后請求Msgbox中斷,A核收到這個中斷后,在回調函數中使用RPMsg接口函數來從VRING中取出cmd)。

隨后A核從cmd handler中獲取緩沖區內的地址和長度,最后在應用層讀取數據,從而完成雙核間的數據傳輸。

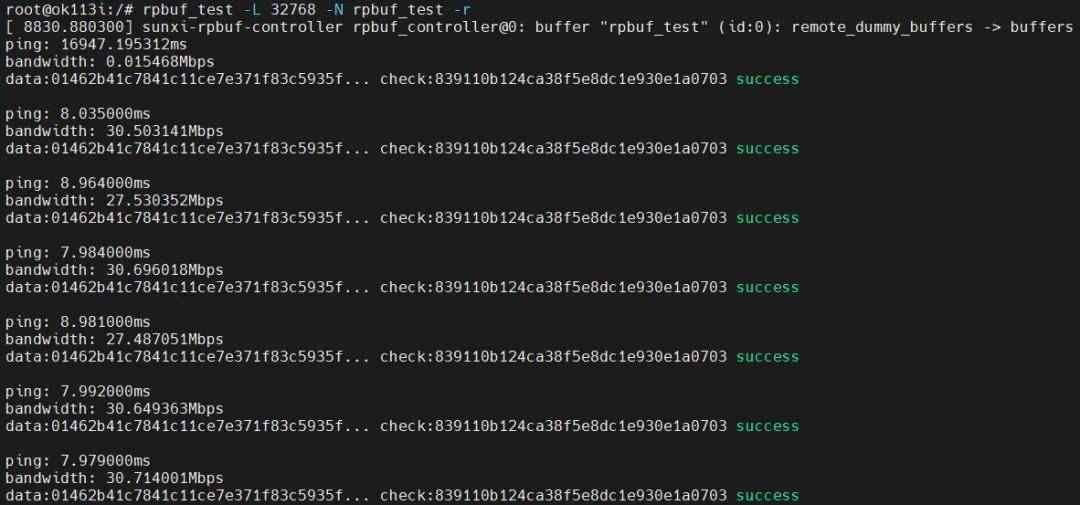

(2) 效果展示

由上圖測試效果可以看到,帶寬大約為27~30Mbps。

以上就是飛凌嵌入式OK113i-S開發板RISC-V核部分外設的使用方法,是不是感覺和單片機的開發一樣簡單方便呢?

-

嵌入式

+關注

關注

5138文章

19524瀏覽量

314702 -

開發板

+關注

關注

25文章

5499瀏覽量

102091 -

多核異構

+關注

關注

0文章

19瀏覽量

5513 -

RISC-V

+關注

關注

46文章

2477瀏覽量

48236 -

全志T113

+關注

關注

0文章

61瀏覽量

561

發布評論請先 登錄

飛凌嵌入式T527核心板獲得【OpenHarmony生態產品兼容性證書】

智能配電新紀元:基于飛凌嵌入式T536核心板的DTU解決方案

國產開發板—米爾全志T113-i如何實現ARM+RISC-V+DSP協同計算?

智能配電新紀元:基于飛凌嵌入式T536核心板的DTU解決方案

ARM + RISC-V核間通信方案,基于全志T113-i的OpenAMP非對稱架構

飛凌嵌入式T113-i開發板RISC-V核的實時應用方案

飛凌嵌入式T113-i開發板RISC-V核的實時應用方案

評論