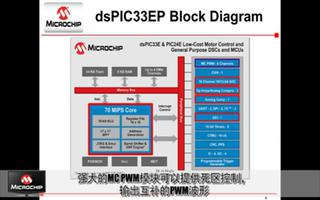

由于人們不斷要求電源具有更高性能和更高功率密度,開關(guān)頻率也變得越來越高, 這要求數(shù)字控制器產(chǎn)品順應(yīng)市場趨勢的變化。Microchip 專為電源應(yīng)用而設(shè)計(jì)的dsPIC33EP ‘GS’ 系列數(shù)字信號控制器就是一種典型的示例。該系列器件引入了新的性能,可縮短線性差分方程(LDE)的執(zhí)行時(shí)間并減少系統(tǒng)的總延時(shí)。這些性能有助于提高控制環(huán)路(1 個(gè)或多個(gè))的采樣率和減少相位損耗,從而實(shí)現(xiàn)環(huán)路增益性能的提升。

在數(shù)字供電單元(PSU)中,有幾個(gè)與單片機(jī)相關(guān)的影響環(huán)路增益性能的因素。這些因素包括最大采樣率、執(zhí)行補(bǔ)償算法(1 個(gè)或多個(gè))所需的時(shí)間、模數(shù)轉(zhuǎn)換器(ADC)的采樣/轉(zhuǎn)換時(shí)間以及單片機(jī)的運(yùn)行速度。對于峰值電流模式控制轉(zhuǎn)換器而言,比較器的速度以及控制數(shù)模轉(zhuǎn)換器(DAC)的精度/速度也會(huì)對 PSU 的環(huán)路增益性能產(chǎn)生影響。因此在挑選特定應(yīng)用所需的單片機(jī)時(shí)需要考慮到所有這些因素。下面,讓我們一起來了解下 Microchip dsPIC33EP ‘GS’ 系列器件如何提升新一代電源應(yīng)用的環(huán)路增益性能。

新型 dsPIC33EP 系列器件最顯著的特點(diǎn)是運(yùn)行頻率的提高。與現(xiàn)有 dsPIC33FJ 系列器件相比,新型 dsPIC33EP 系列器件的運(yùn)行頻率已提高到 70 MHz,實(shí)現(xiàn)了 2,000萬條指令每秒(MIPS)的最大增幅。以執(zhí)行速率為 250 kHz 即 60 條指令的控制環(huán)路為例,如果dsPIC33FJ 系列器件則會(huì)消耗總共 15 MIPS 或 30%的可用資源。而如果換成新的 dsPIC33EP 系列處理器并執(zhí)行相同的采樣率,同一控制環(huán)路代碼只會(huì)消耗 20%的可用 CPU 資源。而如果遷移到新的 dsPIC33EP 系列器件,那么在消耗同樣比例的 MIPS 時(shí),控制環(huán)路的執(zhí)行速率可達(dá)到 350 kHz。進(jìn)一步分析表明,在特定的交叉頻率下,相位損耗可以減少 29%。如公式1 所示,我們可以通過采樣頻率與交叉頻率的關(guān)系計(jì)算出相位損耗。

公式1:因采樣而產(chǎn)生的相位損耗

在大多數(shù)使用數(shù)字補(bǔ)償器的 PSU 中,通常由一個(gè)簡易的 LDE 來進(jìn)行功率級控制的管理。使用 LDE 是眾所周知的一種常用方式,但數(shù)字化實(shí)現(xiàn)方法有利于實(shí)施非線性控制算法。不過,本文將不就非線性技術(shù)展開討論。

LDE 的大小取決于補(bǔ)償器的順序以及用于將連續(xù)頻率函數(shù)變換為離散頻率函數(shù)的方法(向前/向后歐拉、雙線性變換等)。簡單來說,LDE 就是將控制誤差和先前的控制輸出進(jìn)行線性組合以產(chǎn)生電流控制輸出的數(shù)學(xué)表達(dá)式。見公式2 的 3P3Z 線性差分方程示例。

公式2:3P3Z 線性差分方程

從圖中可以看出,對于 3P3Z 補(bǔ)償器而言需要 7 個(gè)乘法和加法來確定所需的控制輸出。這類算術(shù)非常適合 dsPIC33 系列器件的架構(gòu)。在 7 個(gè)單周期指令中,使用乘法累加(MAC)指令就可以完成這些指令的處理。但是這將會(huì)產(chǎn)生額外的軟件開銷, 包括:推入/彈出工作寄存器、工作寄存器數(shù)據(jù)的輸入/輸出、重置數(shù)組,以及鉗位

/縮放控制輸出。這一開銷可能會(huì)影響控制環(huán)路的執(zhí)行速率從而造成相位裕度減少。

如前所述,當(dāng) MIPS 增加時(shí)控制環(huán)路的執(zhí)行時(shí)間減少了很多。對于新型 dsPIC33EP‘GS’系列器件來說,由于添加了備用工作寄存器因而性能得以進(jìn)一步提升。這些器件提供兩個(gè)額外的工作寄存器存儲(chǔ)區(qū),每個(gè)區(qū)域各有 15 個(gè)工作寄存器,也可作永久寄存器使用。這意味著在器件初始化階段就可以將諸如鉗位限制、縮放因子、指針系數(shù)等數(shù)據(jù)預(yù)先加載到合適的備用工作寄存器中。然后我們可以將這些寄存器區(qū)域關(guān)聯(lián)至一個(gè)既定的中斷優(yōu)先級,使得只有控制環(huán)路軟件才有機(jī)會(huì)進(jìn)行訪問。這樣就消除了將工作寄存器推入/彈出堆棧的需要,也將減少在執(zhí)行補(bǔ)償算法時(shí)將數(shù)據(jù)輸入工作寄存器所需的開銷。

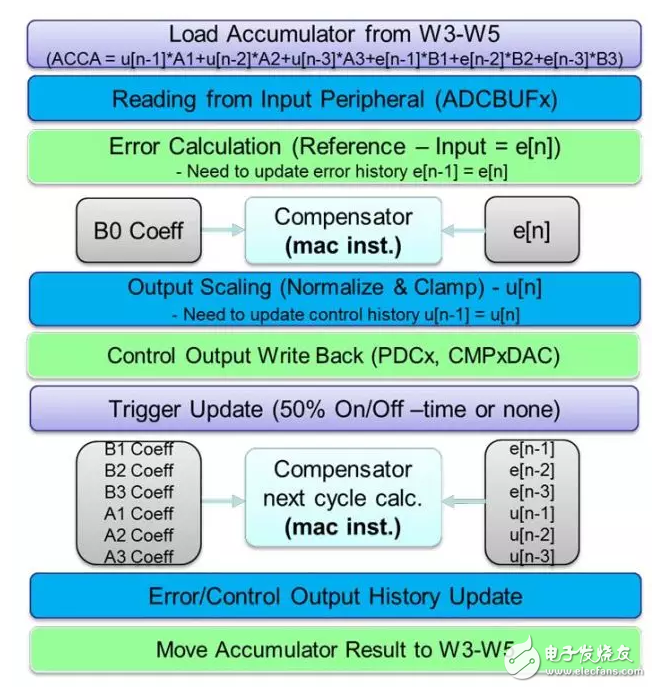

圖 1 是借助 Microchip 硬件加速補(bǔ)償器功能來成功使用備用工作寄存器組的一個(gè)示例。尤其要牢記的是,特定指令需要特定的寄存器,這限制了數(shù)據(jù)可以存儲(chǔ)的地方。

圖 1:備用工作寄存器示例

我們來看一下高頻控制環(huán)路中備用工作寄存器對 MIPS 消耗的影響。之前使用dsPIC33FJ 器件時(shí),若每隔一個(gè)開關(guān)周期要調(diào)用一次補(bǔ)償算法,而現(xiàn)在使用新型器件,消耗相同的 MIPS 可能每一個(gè)開關(guān)周期就能調(diào)用一次補(bǔ)償算法。圖 1 所示的是因采樣過程而產(chǎn)生的相位損耗。相位損耗程度取決于交叉頻率和采樣頻率。因此, 如果采樣速率增加一倍,則相位損耗程度會(huì)減少一半。也就是說,在使用了備用工作寄存器后,因器件運(yùn)行速度的影響所造成的相位損耗減少的比例從 29%提高到了50%。

現(xiàn)在我們舉例來說明因采樣頻率造成的相位損耗減少。比如,在采樣頻率為 175 kHz、帶寬為 10 kHz 的系統(tǒng)中,計(jì)算出的相位損耗大約為 10度。而在同樣一個(gè)系統(tǒng)中,如果采樣頻率為 350 kHz,則相位損耗僅為 5 度。與 dsPIC33FJ 系列器件相 比,dsPIC33EP 系列器件在使用相同比例 MIPS 的條件下可以實(shí)現(xiàn)更多的相位裕度。

上文表明,dsPIC33EP 系列器件的備用工作寄存器和更快的執(zhí)行速度可以獲得較高的采樣頻率,從而減少了相位損耗。接下來,我們再討論一下其它可增加相位裕度并進(jìn)而提升環(huán)路增益性能的特定于器件的外設(shè)與技巧。

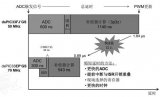

dsPIC33EP ‘GS’系列器件包含一個(gè)集成了多個(gè)逐次逼近寄存器(SAR)內(nèi)核的新型 12 位 ADC。該器件能夠同時(shí)對多個(gè)模擬輸入進(jìn)行采樣,并且只需不到 300 ns 的時(shí)間即可獲得專用 12 位結(jié)果。而專用 SAR 內(nèi)核會(huì)持續(xù)跟蹤輸入信號,這意味著采樣是同步進(jìn)行的,沒有額外的采樣時(shí)間。當(dāng) ADC 檢測到一個(gè)觸發(fā)事件時(shí)就會(huì)自動(dòng)啟動(dòng)轉(zhuǎn)換過程。請記住在控制環(huán)路中,采樣/轉(zhuǎn)換時(shí)間被視作一種延時(shí),該 ADC 將采樣/轉(zhuǎn)換總延時(shí)降至最低,進(jìn)而減少相位裕度損耗。

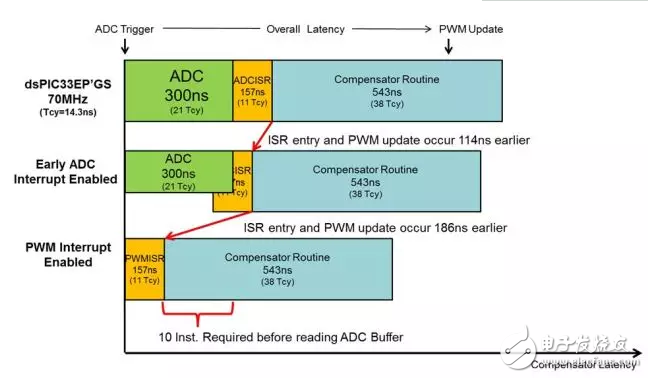

該 ADC 擁有一個(gè)獨(dú)特的性能,即可在轉(zhuǎn)換完成之前產(chǎn)生中斷。這一 ADC 早期中斷功能,一旦允許,可有助減少從 ADC 完成轉(zhuǎn)換到控制環(huán)路軟件啟動(dòng)(中斷)之間的中斷延遲。最大的可選早期中斷時(shí)間為 8 個(gè) ADC 時(shí)鐘(Tad)。在吞吐率最快的情況下,這將進(jìn)入補(bǔ)償算法所需的時(shí)間減少了 114 ns。這是另一種減少控制環(huán)路軟件中總延時(shí)的方法。詳情請參見圖 2 所示的 ADC 早期中斷。

圖 2:ADC 早期中斷時(shí)序

ADC 模塊的另一個(gè)特性是包含多個(gè)數(shù)字比較器,可經(jīng)過配置以便當(dāng)轉(zhuǎn)換后的模擬結(jié)果(未)超出給定的一組限值時(shí)引發(fā)中斷。這一性能看上去似乎不會(huì)直接影響采樣頻率,但事實(shí)上是絕對會(huì)的。當(dāng)軟件只在故障狀態(tài)下才會(huì)運(yùn)行,這種情況消耗的MIPS 更少。這意味著我們是能夠增加控制環(huán)路采樣率的。這高度依賴于軟件,而且并不是所有的應(yīng)用程序都能夠利用這個(gè)新功能的優(yōu)勢。但是,在諸如輸入電壓及溫度監(jiān)控等應(yīng)用中,它可以減少 CPU 的工作負(fù)荷。

為了進(jìn)一步減少從 ADC 觸發(fā)到控制輸出回寫的時(shí)間,可以使用 PWM ISR 來代替 ADC 中斷服務(wù)程序(ISR)和 ADC 早期中斷功能。在通用情況下,PWM 會(huì)觸發(fā) ADC 以啟動(dòng)轉(zhuǎn)換過程,但是現(xiàn)在它也將同時(shí)產(chǎn)生自身的中斷事件。憑借PWM ISR 內(nèi)的補(bǔ)償算法,軟件將在獲取 ADC 的電流反饋數(shù)據(jù)之前開始執(zhí)行補(bǔ)償算法。軟件執(zhí)行和 ADC 轉(zhuǎn)換完成之間大概有 143 ns 的時(shí)間。也就是說,當(dāng)單片機(jī)以最大的器件頻率運(yùn)行時(shí), 從 ADC 結(jié)果緩沖區(qū)取數(shù)之前需要放置至少 10 條指令。如果補(bǔ)償算法是以這樣的一種方式建構(gòu)以便可以使用這一技術(shù),那么 它將能夠把進(jìn)入補(bǔ)償程序的時(shí)間減少45%。圖2 即帶有 PWM 中斷服務(wù)程序的早期中斷時(shí)序示例。要特別注意的是,這個(gè)方法只能在專用 SAR 內(nèi)核的時(shí)序可預(yù)測的情況下應(yīng)用。

補(bǔ)償算法的結(jié)構(gòu)對更新控制輸出變量所需時(shí)間的影響非常大。有了備用工作寄存器, 該算法的寫法可以改為在更新控制輸出之前,只需將電流誤差乘以系數(shù) B0,所得結(jié)果再加上前一個(gè)周期的累加輸出即可。當(dāng)然,落后的標(biāo)準(zhǔn)化和鉗位仍然存在,但 是這將顯著減少控制輸出回寫時(shí)間而無需使用專用的累加器。圖 3 所示的即如何建構(gòu)補(bǔ)償算法以實(shí)現(xiàn)最快更新時(shí)間的范例。現(xiàn)在,一旦進(jìn)入補(bǔ)償算法,控制輸出回寫 只需要不到 300 ns 的時(shí)間。在接下來的章節(jié)中,我們將會(huì)清楚地了解它的作用。

圖 3:3P3Z 硬件加速補(bǔ)償框圖

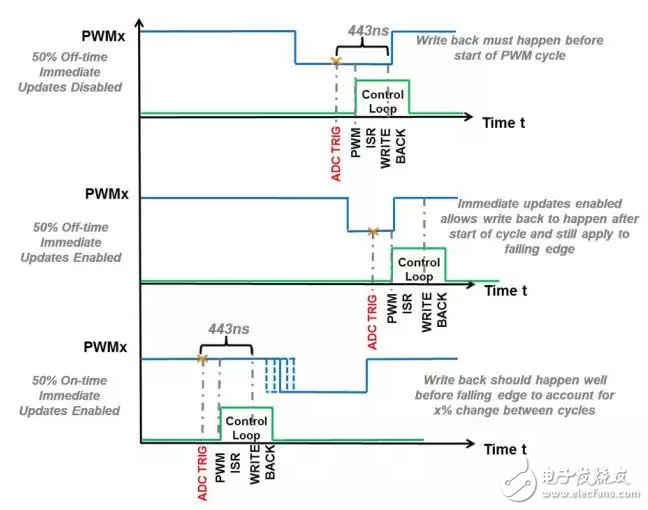

現(xiàn)在讓我們來看看所有這些不同的功能對于相位損耗的影響。在電壓模式控制和平均電流模式控制系統(tǒng)中,我們有機(jī)會(huì)在 50%關(guān)斷時(shí)間里對輸出電容電壓和電感電流進(jìn)行采樣。而最常見的方法是在 50%導(dǎo)通時(shí)間里進(jìn)行采樣,以便有足夠的時(shí)間在下一個(gè) PWM 周期開始之前處理該控制算法。有了上述所有功能,就能夠很容易地在關(guān)斷時(shí)間里對控制反饋信號進(jìn)行采樣,并在下一個(gè) PWM 周期開始之前完成控制輸出回寫。圖 4 所示為一個(gè)實(shí)現(xiàn)范例中不同開關(guān)頻率條件下估計(jì)的占空比限值,而圖 7 所示為 50%關(guān)斷時(shí)間時(shí)序圖。相位裕度的增加依賴于占空比,如果以 50%的占空比進(jìn)行平均,那么與 50%導(dǎo)通時(shí)間條件下的測量相比,相位損耗會(huì)減少一半。

圖 4:不同觸發(fā)機(jī)制下最小/最大導(dǎo)通時(shí)間的關(guān)系

dsPIC33EP ‘GS’ 系列器件擁有即時(shí)更新模式,一旦啟用,將會(huì)在寫入特殊功能寄存器(SFR)的同一周期完成 PWM 參數(shù)更新。這適用于相位、周期、死區(qū)時(shí)間和占空比,分辨率均為 1 ns。在 50%關(guān)斷時(shí)間的情況下,我們曾提到控制輸出回寫要在下一個(gè) PWM 周期開始之前完成,這就限制了在給定開關(guān)頻率條件下的最大導(dǎo)通時(shí)間。而如果啟用即時(shí)更新功能,這個(gè)問題就不存在了。這一性能使得我們現(xiàn)在可以繼續(xù)提高占空比限值和/或開關(guān)頻率限值,從而有助于更進(jìn)一步減少相位裕度損耗。圖5所示為兩種 50%關(guān)斷時(shí)間實(shí)現(xiàn)方式的時(shí)序圖。

圖 5:50%導(dǎo)通/關(guān)斷時(shí)間觸發(fā)時(shí)序圖

減少相位裕度誤差最好的情況就是在 50%導(dǎo)通時(shí)間里對控制反饋信號進(jìn)行采樣而同時(shí)確保新的控制輸出被施加到當(dāng)前 PWM 周期的后一個(gè)邊沿。這意味著我們要基于同一 PWM 周期內(nèi)剛被調(diào)用的補(bǔ)償器輸出對 PWM 占空比的有效邊沿進(jìn)行更新。而這將促成數(shù)字系統(tǒng)中可能實(shí)現(xiàn)的最佳相位裕度。然而我們要注意的是,這只是實(shí)現(xiàn)最佳用 例的情況,由于受限于最小導(dǎo)通時(shí)間,并不能在所有的應(yīng)用中實(shí)現(xiàn)。請參見圖 6 不同開關(guān)頻率條件下占開關(guān)周期不同比例的最小導(dǎo)通時(shí)間。以開關(guān)頻率為 100 kHz 的升壓 PFC 為例,所需最小導(dǎo)通時(shí)間的周期占比將接近于 10%。由于最小占空比發(fā)生在 AC 線電壓的峰值,在額定 220V 輸入電壓條件下,占空比要求約為 22%,這就留出了充足的余量進(jìn)行即時(shí)更新,以應(yīng)對控制輸出的大幅變化。隨著輸入電壓進(jìn)一步 增加,即時(shí)更新看上去逐漸趨同于周期更新的結(jié)束,并且相位裕度也將減少。然而, 這種情況只發(fā)生在標(biāo)稱條件之外。如圖 7 所示,我們還可以看到 50%導(dǎo)通時(shí)間觸發(fā)用例時(shí)序圖與 50%導(dǎo)通時(shí)間觸發(fā)機(jī)制的對比。

我們使用同步降壓轉(zhuǎn)換器結(jié)合本文討論的所有技巧進(jìn)行了實(shí)踐。結(jié)果顯示,采樣速率從每隔一個(gè) PWM 周期(175 kHz)增加到了每一個(gè) PWM 周期(350 kHz)但無需消耗更多的 MIPS,補(bǔ)償器被編寫成可實(shí)現(xiàn)到控制輸出變量的快速回寫,PWM 中斷也生成用以處理控制環(huán)路,同時(shí)采用 50%導(dǎo)通時(shí)間并啟用即時(shí)更新功能。我們可以觀察到相位裕度因此增加了大約 16 度。環(huán)路增益性能開始稍顯穩(wěn)定并維持在相位裕度僅為 46 度的水平,并最終趨近于 62 度模擬環(huán)路。本文所討論的減少相位損耗的技巧并不是萬能的;但是它們適用于范圍廣泛的設(shè)計(jì)并且能在一定程度上提升環(huán)路增益。

-

數(shù)字電源

+關(guān)注

關(guān)注

28文章

535瀏覽量

109762

發(fā)布評論請先 登錄

有像Proteus那樣的DSPIC33 EP系列的虛擬電路模擬器?

dsPIC33FJ16GS504兼容dsPIC

基于dsPIC33F GS系列的1KVA離線UPS參考設(shè)計(jì)方

dsPIC33設(shè)計(jì)的GS系列DSC數(shù)字LED照明技術(shù)

大聯(lián)大品佳集團(tuán)推出基于Microchip產(chǎn)品的新能源汽車OBC電源解決方案

高性能電機(jī)控制單片機(jī)— dsPIC33EP256MC506 系列

數(shù)字電源入門工具包演示

dsPIC33EP128GS808開發(fā)板功能特性及用戶指南

dsPIC33EP GS系列是Microchip新一代16-bit高性能MCU

Microchip專家技術(shù)文章:使用dsPIC33EP‘GS’系列器件提升數(shù)字電源的環(huán)路增益性能

Microchip專家技術(shù)文章:使用dsPIC33EP‘GS’系列器件提升數(shù)字電源的環(huán)路增益性能

評論