以下文章來源于CAE工程師筆記 ,作者CAE工程師筆記Tony

隨著基于半導體技術的電子器件和產(chǎn)品在生產(chǎn)和生活中廣泛應用,以集成電路為核心的半導體產(chǎn)業(yè)已成為推動國民經(jīng)濟發(fā)展的支柱型產(chǎn)業(yè)。為了滿足消費者對電子產(chǎn)品輕薄化、高性能和低功耗的發(fā)展需求,半導體集成電路和集成電路封裝技術也朝著高密度集成和系統(tǒng)化發(fā)展方向前進。

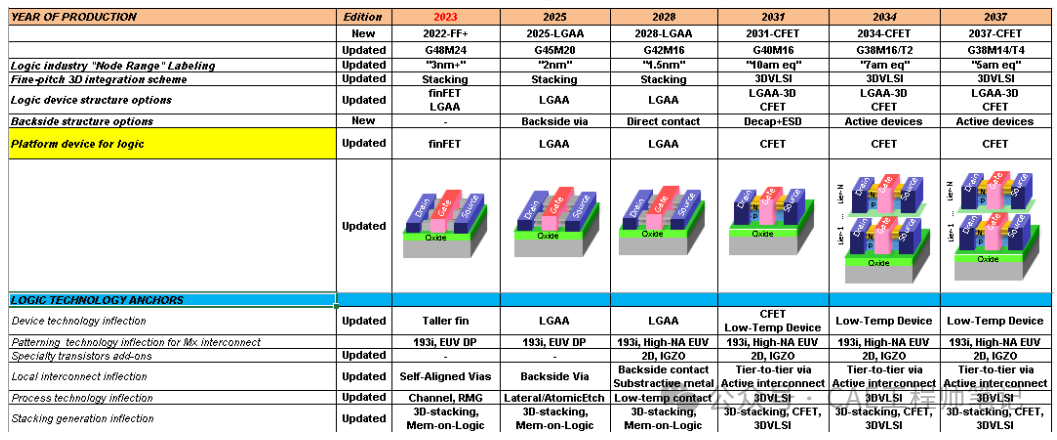

近年來 5G、AI、Autopilot、HPC 等新興領域的發(fā)展,要求電子器件具有更低的信號傳輸延遲和更大的數(shù)據(jù)吞吐量。此外,隨著集成電路晶體管特征尺度逐步逼近物理極限,進一步提升單顆芯片的集成度面臨技術難度和成本激增的嚴峻問題,先進電子封裝技術被認為是延續(xù)摩爾定律的關鍵途徑。

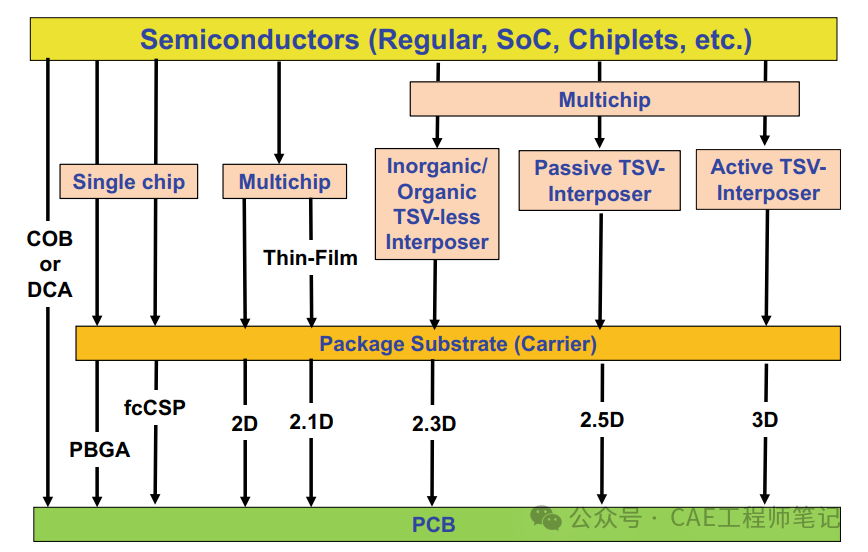

全球半導體行業(yè)領域內(nèi)對于先進封裝技術和傳統(tǒng)封裝技術通過是否有焊線進行區(qū)分。傳統(tǒng)封裝通常采用引線框架作集成電路線路互通和支撐連接的載具,典型的傳統(tǒng)封裝形式由雙列直插式封裝(DIP)、小外形封裝(SOP)、小型方塊平面封裝(QFP)等,隨著智能移動終端、物聯(lián)網(wǎng)、人工智能和大數(shù)據(jù)等新興領域的快速擴展,全球封裝市場為適應小型化,高集成的需求在不斷擴容。當前已發(fā)展三維集成封裝、晶圓/面板級扇出型封裝等先進封裝技術。越來越多的芯片被集成到一個封裝體中,促使電子封裝向系統(tǒng)級封裝(System In Package)和異構(gòu)集成(Heterogeneous Integration)方向發(fā)展。

系統(tǒng)級封裝(System In Package)基于多種先進封裝互連技術,將多個不同功能模塊集成組裝在一個封裝包內(nèi)。國際半導體技術路線圖(ITRS 2005)在組裝與封裝中對系統(tǒng)級封裝定義為:

系統(tǒng)級封裝是采用任意組合, 將數(shù)個具有不同功能的有源電子器件、可選擇性的無源器件及如機電系統(tǒng)或光學器件等組裝成為具有多種功能的單個標準封裝件,從而形成一個系統(tǒng)或者子系統(tǒng)。

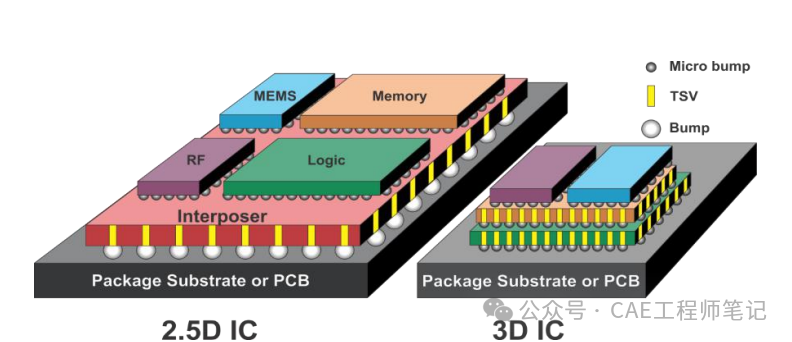

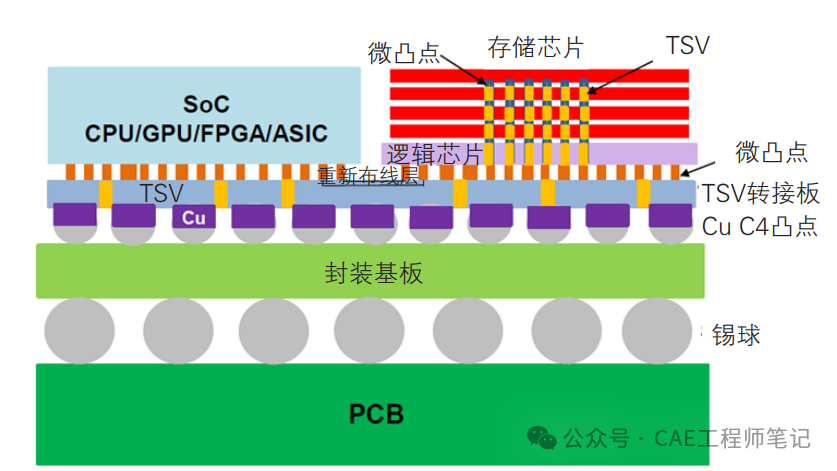

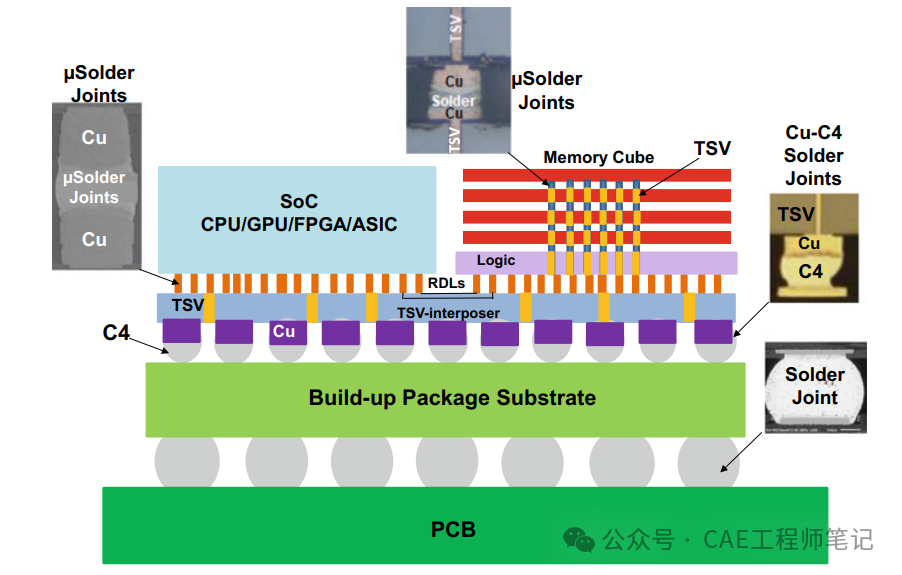

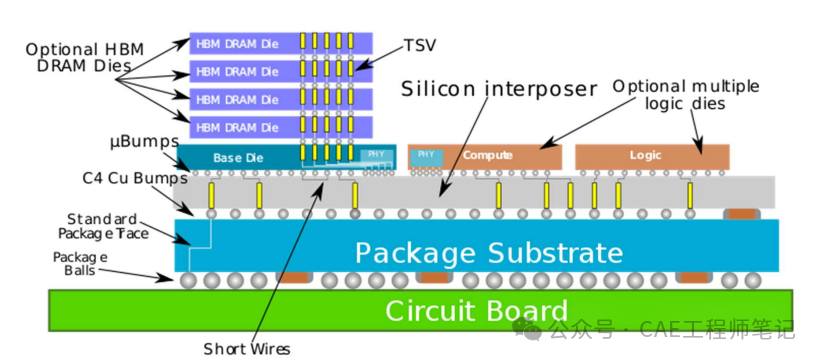

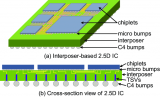

行業(yè)內(nèi)為了實現(xiàn)元器件更小尺寸和封裝密度更高、成本更低的發(fā)展目標, 2.5D/3D 封裝技術作為系統(tǒng)封裝的關鍵封裝技術已經(jīng)成為未來重點發(fā)展的方向。2.5D/3D 封裝都是基于此前二維平面封裝 X-Y 平臺的基礎上,通過TSV技術在 Z 方向?qū)崿F(xiàn)芯片互連或者堆疊。2.5D 封裝是通過 TSV 技術將多個芯片通過硅轉(zhuǎn)接板互連,多個芯片堆疊在內(nèi)含有 TSV 的硅轉(zhuǎn)接板的頂部,因此硅轉(zhuǎn)接板是芯片和基板之間的橋梁,能夠為系統(tǒng)提供更多的 I/O 帶寬。而3D封裝是將具有 TSV 結(jié)構(gòu)的芯片疊合起來在 Z 向完成互連,將平面組裝發(fā)展為具有縱向高度的立體組裝,具有更高的集成度。

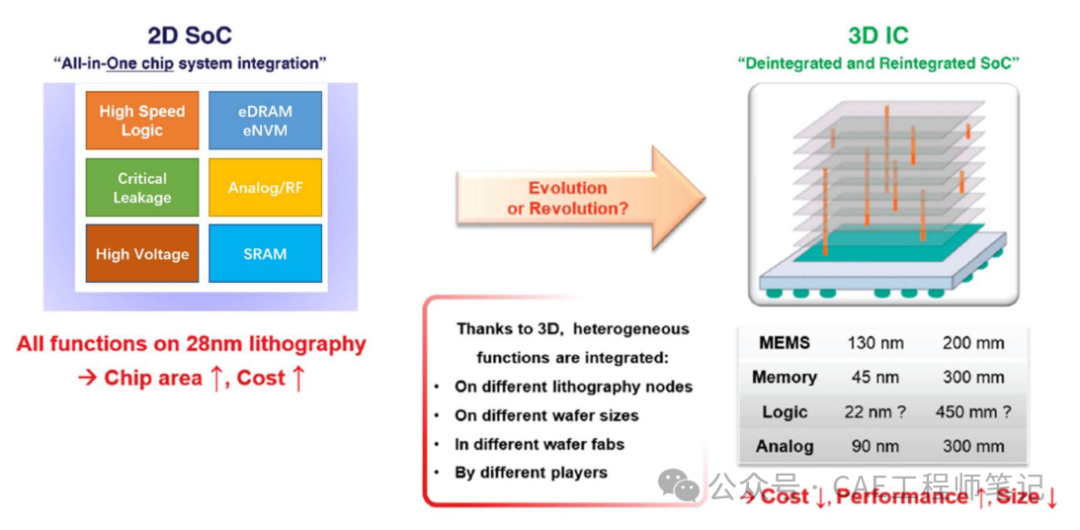

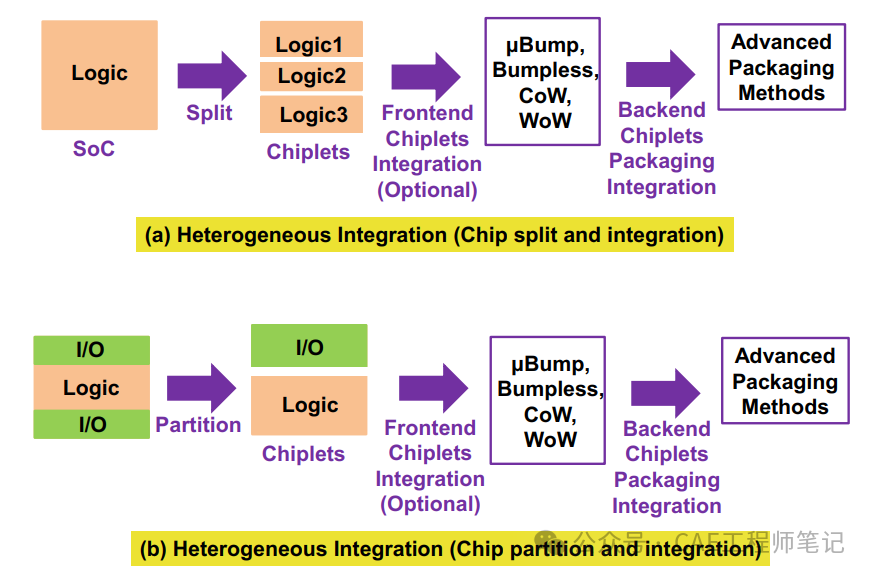

芯片異構(gòu)集成是使用先進封裝技術將來自不同晶圓制造廠商且具有不同晶圓尺寸和特征技術節(jié)點或具有不同材料和功能的系列芯片,采用并排或堆疊方式布局到轉(zhuǎn)接板或封裝基板上組成系統(tǒng)或子系統(tǒng),從而構(gòu)成集成度更高、性能更強、功能更多的更高級的系統(tǒng)級封裝技術。

異構(gòu)集成面向更細節(jié)距、更多輸入輸出端口、更高密度和更高性能的應用,可以使整個封裝系統(tǒng)性能得到數(shù)量級上的提升。異構(gòu)集成是在同一個封裝中集成多個芯片,使得這個封裝體具有特定的且更復雜的功能和更小的成形因子,而與將大部分功能集成到一個芯片中的系統(tǒng)級芯片(SoC)有著明顯的不同。

舉例來說,為了進一步提高芯片的處理能力,通常會增加 SoC 的核數(shù),進一步提高晶體管微縮化,這不僅會造成設計研發(fā)周期延長和成本劇增,還會使得單顆芯片的面積增加,從而使生產(chǎn)良率降低。

采用異構(gòu)集成技術進行整合,可以將 SoC 分割成更小的芯片(Chiplet)進行制造,從而可以從同樣大小的晶圓上獲得更多的芯片,使得生產(chǎn)良率提升數(shù)倍,并大大降低成本。并且不同功能的芯片有著不同的最優(yōu)工藝制程,采用相同工藝制程制造不同功能的芯片反而使芯片的性能得不到有效發(fā)揮。

異構(gòu)集成封裝系統(tǒng)中集成了多種不同功能的芯片,為滿足芯片之間及芯片與外部電路的高效交流,必須為之建立低延遲、高帶寬的信號傳輸路徑,這就需要采用包括轉(zhuǎn)接板、互連焊點、硅通孔(TSV)或模塑通孔(TMV)在內(nèi)的封裝技術。

2.5D 異構(gòu)集成封裝技術在橫向縱向技術對比上具有顯著的性能提升、成本可控和效率提高等優(yōu)勢:

封裝效率高,高集成。同一封裝體內(nèi)可多芯片組合貼裝,減少封裝體積。

降低系統(tǒng)成本。相比傳統(tǒng)封裝,可以實現(xiàn)多芯片多模塊互連在一個系統(tǒng)里,節(jié)省更多系統(tǒng)設計和產(chǎn)出成本。

低功耗,穩(wěn)定性好,電性能高。相比而言焊點數(shù)目減少,封裝體積重量降低,元器件互連路線縮短。

應用更廣泛。可以在光通信系統(tǒng),傳感器系統(tǒng)以及 MEMS 系統(tǒng)等更多領域。

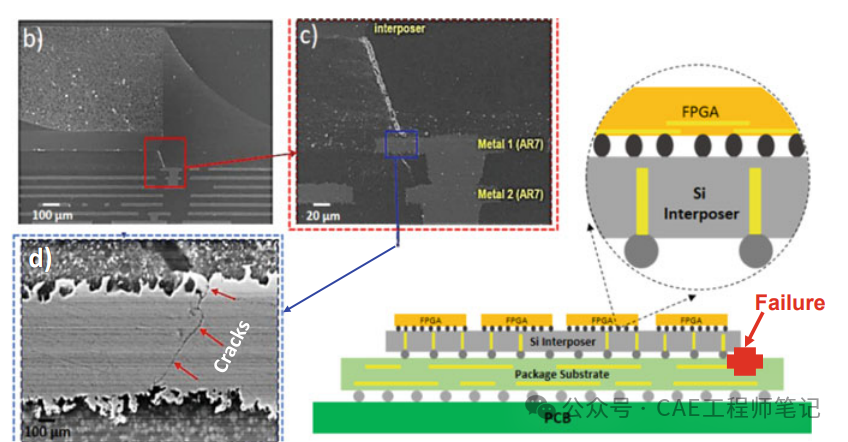

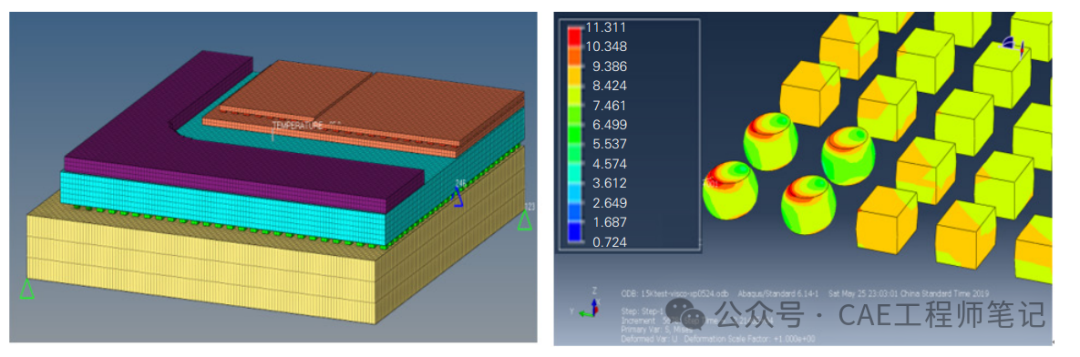

2.5D 異構(gòu)集成封裝結(jié)構(gòu)精細且復雜,為保護脆弱的互連焊點,降低互連線路的電容電感,通常采用底部填充膠(Underfill)、環(huán)氧模塑料(EMC)、低介電常數(shù)材料(Low-k Dielectric)等多種材料構(gòu)成復合材料體系。因此,封裝結(jié)構(gòu)中存在許多材料界面,由于界面兩側(cè)材料結(jié)合力較弱且不同材料性質(zhì)差異較大,主要是熱膨脹系數(shù)(CTE)和彈性模量的差異,導致封裝器件在制造、測試和服役過程中界面開裂甚至大范圍剝離。

2.5D 異構(gòu)集成封裝通常采用跨尺度互連焊點進行多級裝配,從而滿足超高輸入輸出端口數(shù)量的需要,處于不同級別的互連焊點經(jīng)歷回流次數(shù)不同且由于應用尺寸的差異,導致這些跨尺度互連焊點力學性能具有較大差異。

例如在三維堆疊的 HBM芯片之間,以及 GPU 與硅轉(zhuǎn)接板之間的微凸點互連尺寸小于 25 μm,轉(zhuǎn)接板與封裝基板之間的 C4 焊點尺寸在 100 μm 左右,而封裝基板與 PCB 板之間的 BGA 焊點尺寸可以達到數(shù)百微米。互連焊點作為芯片與外部電路連接和交流的重要通道,它是最容易出現(xiàn)可靠性問題的薄弱環(huán)節(jié)。

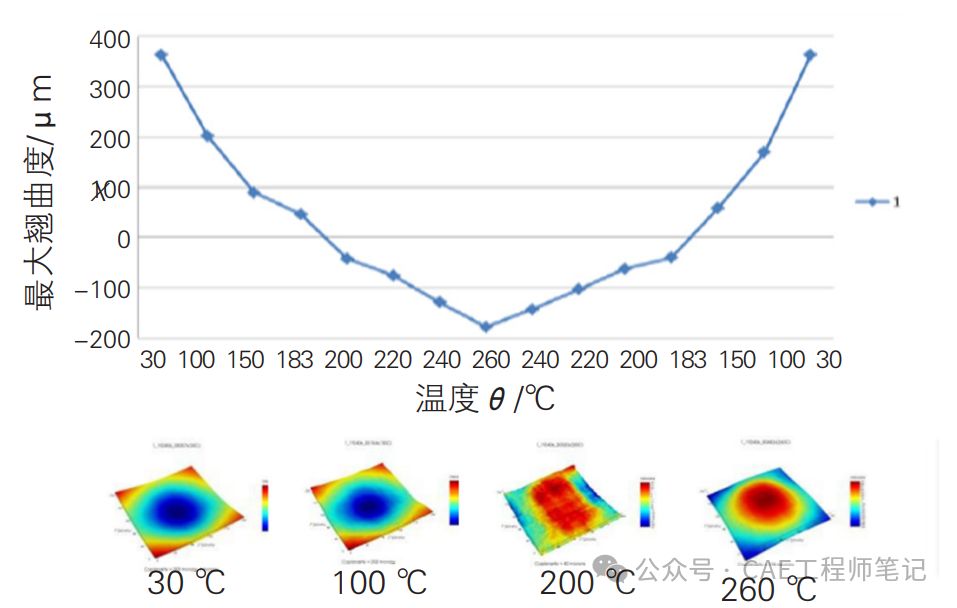

同時多層不同材質(zhì)的結(jié)構(gòu)分布會使得整個封裝結(jié)構(gòu)在熱服役環(huán)境過程中由于熱不匹配產(chǎn)生封裝可靠性問題。由于熱膨脹系數(shù)之間的差異,在服役過程中,各材質(zhì)在熱或冷或冷熱交替的環(huán)境中產(chǎn)生不同程度的變形,因而在接觸界面之間產(chǎn)生應力集中現(xiàn)象。

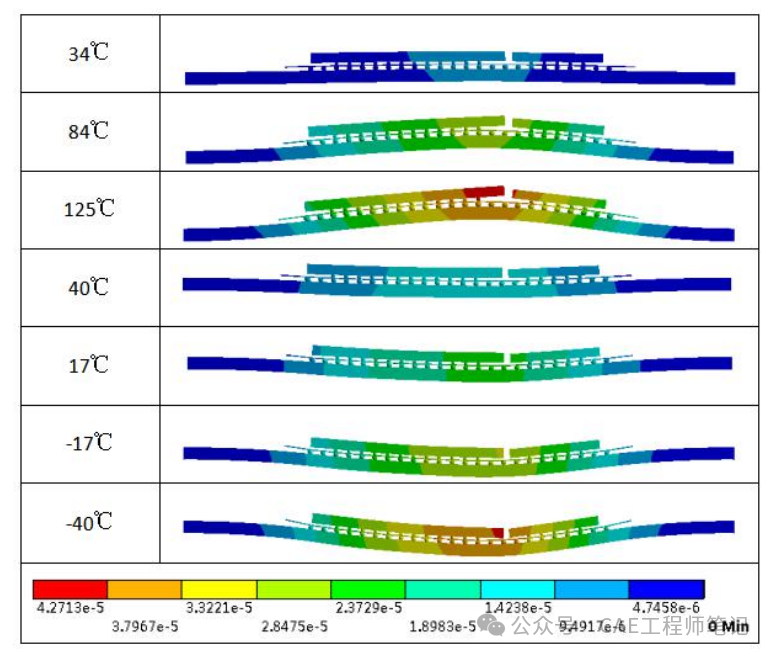

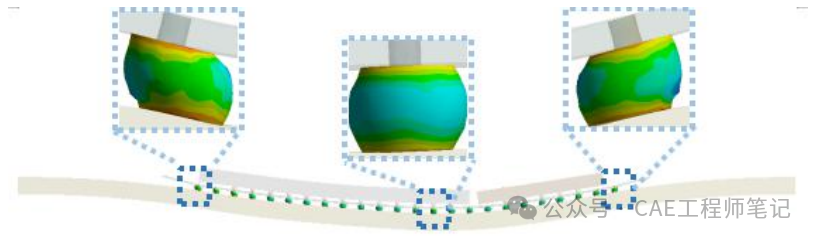

下圖案例為在一個溫度循環(huán)過程中不同溫度下 2.5D 封裝結(jié)構(gòu)模型的翹曲變形情況。從圖中可以看出,在升溫階段從室溫升至最高溫度125℃ 過程中,結(jié)構(gòu)模型產(chǎn)生向 Z 向正方向的翹曲變形,在 125℃ 時翹曲變形達到正向最大值。而在降溫階段從室溫降至最低溫度 -40℃ 過程中,結(jié)果模型產(chǎn)生向 Z 向負方向的翹曲變形,在 -40℃ 時翹曲變形達到負方向最大值。

在溫度循環(huán)中由于封裝結(jié)構(gòu)材質(zhì)熱膨脹系數(shù)差異,焊點熱膨脹系數(shù)最大,硅材質(zhì)的芯片和硅轉(zhuǎn)接板熱膨脹系數(shù)最小,結(jié)構(gòu)受熱在 Z 向正方向發(fā)生翹曲變形。隨著溫度升高,焊點熱膨脹系數(shù)增大,與芯片和硅轉(zhuǎn)接板差異增大,結(jié)構(gòu)在 Z 向翹曲變形越來越大。

總得來說,2.5D 封裝的核心在于芯片與基板之間的嵌入式硅轉(zhuǎn)接板,通過轉(zhuǎn)接板上的 TSV 通孔、再布線層、微凸點等,達成芯片與芯片、芯片與封裝基板間更高密度的互連。再結(jié)合異構(gòu)集成技術將不同的芯片集成到一個封裝體中,在縮短研發(fā)上市周期、提升性能、降低功耗和成本等方面具有傳統(tǒng) SoC 無法比擬的優(yōu)勢。

然而由于 2.5D 異構(gòu)集成封裝結(jié)構(gòu)中包含 TSV-Cu/Ta/SiO2/Si 多層界面、硅轉(zhuǎn)接板/微凸點的 Cu/Sn 界面等多級互連界面,熱膨脹系數(shù)及結(jié)構(gòu)尺寸均存在較大差異,極易在熱應力作用下因熱失配產(chǎn)生熱疲勞失效。如何降低封裝結(jié)構(gòu)的局部應力和減小封裝翹曲,從而提高封裝可靠性,就顯得尤為重要了。

-

半導體

+關注

關注

335文章

28499瀏覽量

231572 -

系統(tǒng)級封裝

+關注

關注

0文章

39瀏覽量

9224 -

先進封裝

+關注

關注

2文章

457瀏覽量

491 -

2.5D封裝

+關注

關注

0文章

24瀏覽量

315

原文標題:先進封裝技術(Semiconductor Advanced Packaging) - 10 2.5D封裝與異構(gòu)集成技術

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

傳聞不攻自破?華為和Altera合力實現(xiàn)2.5D異構(gòu)封裝技術!

新型2.5D和3D封裝技術的挑戰(zhàn)

異構(gòu)集成基礎:基于工業(yè)的2.5D/3D尋徑和協(xié)同設計方法

日本計劃量產(chǎn)2nm芯片,著眼于2.5D、3D封裝異構(gòu)技術

2.5D與3D封裝技術:未來電子系統(tǒng)的新篇章

探秘2.5D與3D封裝技術:未來電子系統(tǒng)的新篇章

深入剖析2.5D封裝技術優(yōu)勢及應用

2.5D封裝與異構(gòu)集成技術解析

2.5D封裝與異構(gòu)集成技術解析

評論