Hi,我是小杜。PCIe作為高速傳輸總線,使用差分信號線傳輸數據,支持多通道鏈路。但由于設計需求和布局限制,可能需要在設備之間或主板上調整PCIe通道走向,因此可能會產生信號極性和通道順序的問題,如處理不當會造成數據解析錯誤、損害信號質量等后果。PCIe規范考慮到這一點,提出了通道極性翻轉和通道順序翻轉的解決方案,小杜來講一下此過程。小杜經驗尚淺,如有錯誤,還請批評指正。

信號極性翻轉

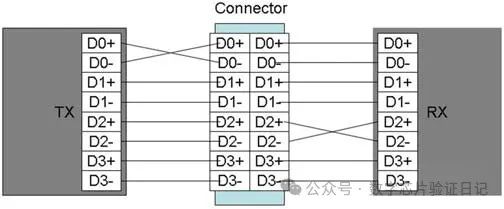

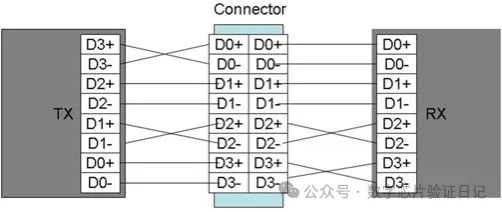

PCIe使用差分信號對來傳輸數據,即通過兩根電氣線傳輸,每根線攜帶相同的信號,但電壓極性相反,稱為正極(D+)和負極(D-)。通常發射端的D+直接連接到接收器的D+,D-同理。如下圖所示,發射端Tx,中間連接器Connector和接收端Rx的D+、D-一一對應。

但由于布局布線等原因,Tx的D+可能和接受端的D-連接。對于Rx來說,它們并不知道和對端的電氣線具體是如何連接的,正負極接反會導致Rx解析出相反的數據,比如1010解析為0101(所有bit都相反)。

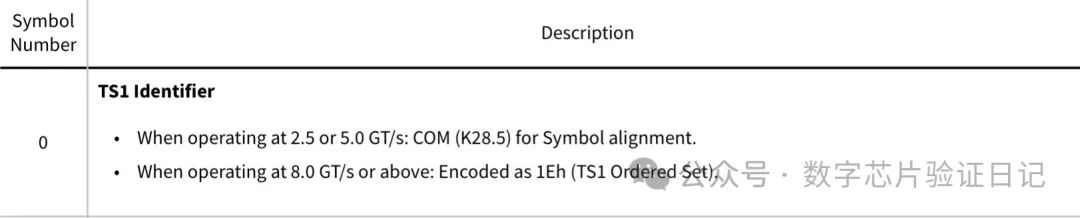

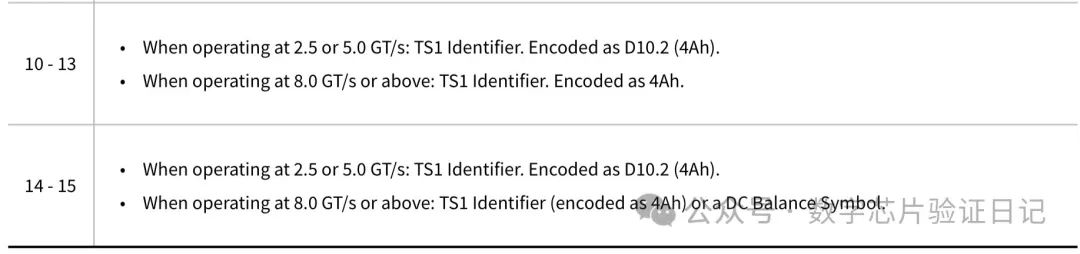

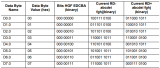

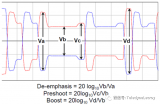

PCIe協議考慮到了這一點,提供了在訓練階段各通道Rx自動識別并調整其極性的方法。當鏈路訓練進入到Polling階段時,Rx可以通過識別TS1 OS的TS1 OS Identifier Symbol(TS1 OS識別符)來判斷通道當前極性,以Symbol 10到15為例,當識別到4Ah(0100_1010)時表示通道極性正常,當識別到B5h(1011_0101)時則表明D+接到了D-上,此時Rx需要自動按相反極性解析收到的數據。只有當鏈路所有的通道都正確地受到4Ah后才會進一步解析訓練序列中攜帶的信息。

通道位置翻轉

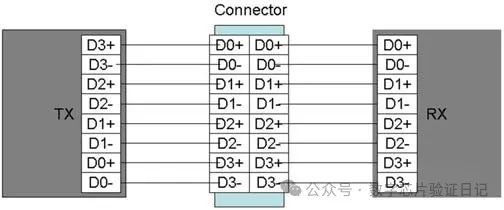

考慮另一種情況,如果Tx端從上到下是Lane3 ~ Lane0,而Rx端是Lane0~Lane3,這種情況稱為通道位置反轉,此時#Lane0的引腳會接到#Lane3的引腳上。由于TLP和DLLP的傳輸對通道順序有要求,比如STP和SDP必須放置在Lane0,因此鏈路訓練時一側需要根據各Lane受到的訓練序列來翻轉其通道順序,以實現Tx和Rx的通道順序匹配,當通道順序翻轉時需要翻轉所有通道。

一些PCIe金手指有防呆口設計,可以避免通道順序翻轉的情況,但對于焊在主板上的PCIe芯片,可能會出現兩端通道順序相反的情況。如果不進行通道位置翻轉,就需要使用PCB導孔換層來解決,這會降低高速信號質量,所以推薦PCIe設備支持通道位置翻轉功能。

當然,信號極性翻轉和通道順序翻轉可能會同時出現,如下圖所示,Tx/Connector/Rx之間通道順序相反,4條Lane的極性也相反。????????????????????????????????????????????????????

通過上述說明可以看出即使出現了通道極性和順序的問題,PCIe鏈路訓練也可以自動完成通道間的匹配,這通常對用戶來說是無感的。只有確保各通道連接正確,才能正常解析數據,繼續后續的鏈路訓練步驟。感謝你耐心地看到這里。

-

信號

+關注

關注

11文章

2841瀏覽量

77865 -

總線

+關注

關注

10文章

2945瀏覽量

89309 -

PCIe

+關注

關注

16文章

1317瀏覽量

84623 -

負極

+關注

關注

0文章

68瀏覽量

9643

原文標題:【PCIe】鏈路訓練 - 通道極性和順序翻轉

文章出處:【微信號:小杜的芯片驗證日記,微信公眾號:小杜的芯片驗證日記】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

nvme IP開發之PCIe上

用于 PCIe Gen-3 卡的高速前端參考設計

基于 PCIE 總線的 4 路 10G 雙緩沖光纖通道適配器

可提高信號完整性和系統穩健性PCIe Gen-3高速前端卡設計包括BOM,PCB文件及光繪文件

AC701能否通過Artix 7的PCIe鏈路與PC通信?

PCIe 3.0/4.0的鏈路均衡的工作原理

PCIe Gen-3高速前端卡參考設計

體驗紫光PCIE之使用WinDriver驅動紫光PCIE

[PCIe] [電源管理] 面向硬件的ASPM鏈路狀態和L1子狀態

![[<b class='flag-5'>PCIe</b>] [電源管理] 面向硬件的ASPM<b class='flag-5'>鏈</b><b class='flag-5'>路</b>狀態和L1子狀態](https://file.elecfans.com/web1/M00/D9/4E/pIYBAF_1ac2Ac0EEAABDkS1IP1s689.png)

[PCIe] [電源管理] 面向硬件的ASPM鏈路狀態和L1子狀態

![[<b class='flag-5'>PCIe</b>] [電源管理] 面向硬件的ASPM<b class='flag-5'>鏈</b><b class='flag-5'>路</b>狀態和L1子狀態](https://file.elecfans.com/web1/M00/D9/4E/pIYBAF_1ac2Ac0EEAABDkS1IP1s689.png)

PCIe鏈路訓練之通道極性和順序翻轉

PCIe鏈路訓練之通道極性和順序翻轉

評論