1. 引言

在現代電子系統中,信號的精確放大和處理是至關重要的。差分放大電路因其獨特的優勢,如高共模抑制比(CMRR)、高輸入阻抗和低輸出阻抗,而在各種電子設備中得到了廣泛的應用。

2. 差分放大電路的基本原理

差分放大電路的核心原理是利用兩個輸入端之間的電壓差來產生輸出信號。這種電路設計可以有效地抑制共模信號,即兩個輸入端同時出現的信號,而只放大差模信號,即兩個輸入端之間的電壓差。

2.1 差分放大電路的組成

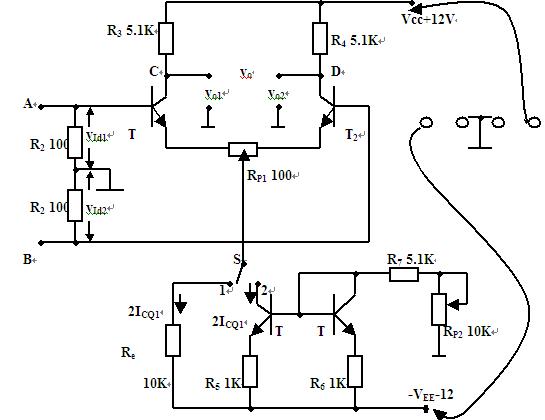

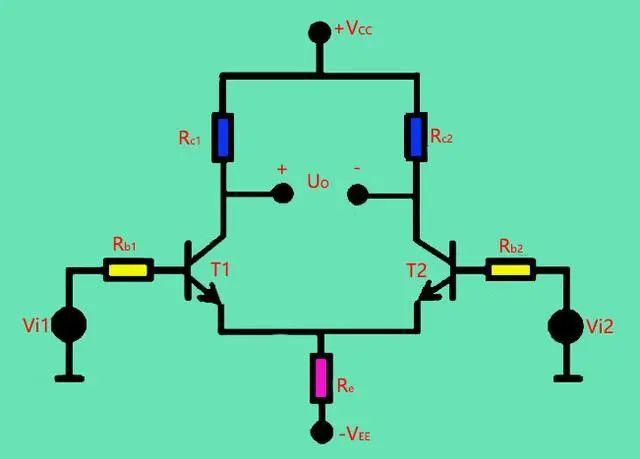

差分放大電路通常由兩個晶體管、兩個電阻和電源組成。這兩個晶體管通常為雙極型晶體管(BJT)或金屬氧化物半導體場效應晶體管(MOSFET),它們共享一個公共的發射極或源極,分別連接到兩個輸入端。

2.2 差分放大電路的工作原理

當兩個輸入端的電壓相等時,兩個晶體管的基極-發射極電壓(或柵極-源極電壓)也相等,導致兩個晶體管的集電極電流(或漏極電流)相等。在這種情況下,輸出端沒有電流流過,因此輸出電壓為零。

當兩個輸入端的電壓不相等時,兩個晶體管的基極-發射極電壓(或柵極-源極電壓)也不同,導致兩個晶體管的集電極電流(或漏極電流)不同。這種電流差異會在輸出端產生一個電壓差,從而產生輸出信號。

2.3 差分放大電路的共模抑制比(CMRR)

共模抑制比(CMRR)是衡量差分放大電路抑制共模信號能力的一個重要參數。CMRR定義為差分放大電路放大差模信號的能力與放大共模信號能力的比值。高CMRR意味著電路對共模信號的抑制能力強,從而提高了信號的信噪比。

3. 差分放大電路的設計

設計一個高性能的差分放大電路需要考慮多個因素,包括晶體管的選擇、電阻的匹配、電源的設計以及電路的布局。

3.1 晶體管的選擇

晶體管的選擇對差分放大電路的性能有重要影響。通常,選擇具有高跨導(g_m)和低輸入偏置電流的晶體管可以提高電路的增益和穩定性。

3.2 電阻的匹配

電阻的匹配對差分放大電路的共模抑制比(CMRR)有重要影響。為了獲得高的CMRR,需要選擇具有高精度和低溫度系數的電阻。

3.3 電源的設計

電源的設計需要考慮電源紋波、電源電壓和電源電流等因素。為了獲得穩定的輸出信號,需要設計一個低紋波和高穩定性的電源。

3.4 電路的布局

電路的布局對差分放大電路的性能也有重要影響。為了減少噪聲和干擾,需要合理布局電路,避免信號線和電源線的交叉,同時使用屏蔽和接地技術來減少電磁干擾。

4. 差分放大電路的配置

差分放大電路有多種配置方式,包括單端輸入差分放大電路、雙端輸入差分放大電路和差分放大電路的級聯配置。

4.1 單端輸入差分放大電路

單端輸入差分放大電路只有一個輸入端,另一個輸入端接地。這種配置適用于需要單端輸入信號的應用。

4.2 雙端輸入差分放大電路

雙端輸入差分放大電路有兩個輸入端,分別連接到兩個晶體管的基極(或柵極)。這種配置適用于需要雙端輸入信號的應用。

4.3 差分放大電路的級聯配置

差分放大電路的級聯配置可以提高電路的增益和穩定性。通過將多個差分放大電路級聯,可以實現高增益和高穩定性的信號放大。

-

電路

+關注

關注

173文章

6022瀏覽量

174323 -

電子系統

+關注

關注

0文章

455瀏覽量

31515 -

差分放大電路

+關注

關注

18文章

161瀏覽量

50453 -

輸出信號

+關注

關注

0文章

302瀏覽量

12125

發布評論請先 登錄

差分放大電路的設計原理、組件選擇及電路配置

差分放大電路的設計原理、組件選擇及電路配置

評論