1. 去耦電容的選擇

電容類型總結表格

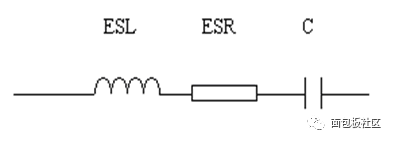

實際的電容并不是理想,表現為:

a.電容具有引腳電感,當頻率高到一定的值后會使得電容的阻抗增加;

b.電容具有ESR,這也會降低電容的性能;

c.電容有溫度特性,隨著溫度的改變,電容的介質屬性會變化并引起容值的變化;

d.電容的容值會由于介質老化而慢慢變化;

e.電容過壓會爆炸。

當選擇去耦電容時,充分理解上述非理想性是很重要的,串聯電感和ESR的影響可以計算得到,關于溫度特性、老化特性和電壓范圍只能由生產廠家提供詳細資料。

用等效交流阻抗來評估一個去耦電容的優劣,等效交流阻抗用電阻、電感和電容阻抗的均方根值來近似:ohms

其中:RESR:電容的串聯電阻;Xac:電容的等效交流阻抗;L:電容管腳、封裝、接插件電感的和。

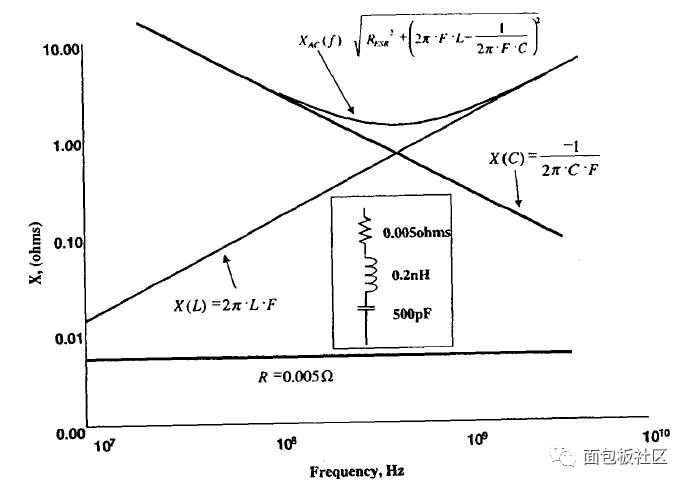

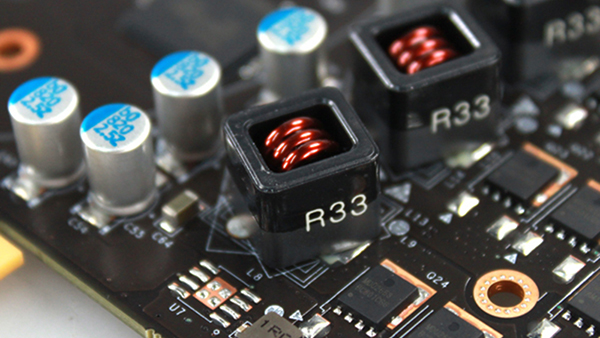

下圖所示的為一個電容的頻響曲線。圖中可以看出電容的帶通特性(bandpass characteristics),低頻段,電容表現為電容,當頻率增加,電感成分占了上風,阻抗隨頻率增加而增加。

電容的阻抗很大程度上依賴于數字信號的頻譜成分。因此,應該正確選擇這一頻率,可是在數字系統中因為信號包含很多頻率成分,所以這一頻率不是可以直接得到的。有一些方法可以得到旁路電容必須通過的最大頻率。

一些工程師簡單的選擇最大頻率為基頻的五次諧波,例如,如果總線的頻率為500MHz,它的五次諧波為2500MHz。如果電容的引腳電感或ESR很高,那么可以另外選擇電容或并聯放置電容以降低等效電感和電阻。

2. 去耦電容的去耦時間的計算

本文從另外一個更直觀的角度來說明去耦電容的這種特性,即電容的去耦時間。穩壓電源以及去耦電容是構成電源系統的兩個重要部分。對于,現在芯片的速度越來越快,尤其對于高速處理芯片,負載芯片的電流需求變化也是非常快。內部晶體管開關速度極快。

例如,處理芯片內部有2000個晶體管同時發生狀態翻轉,轉換時間是1ns,總電流需求為600mA。

這就意味著,電源系統必須再1ns時間內補足600mA瞬態電流。但是,對于目前的穩壓源系統來說,在這么短的時間內并不能反應過來,相對于快速變化的電流,穩壓源明顯滯后了。根據一般經驗來說,穩壓源的頻率響應為幾百K左右,因為在時域系統里,1/100KHz=10us,也就是說,穩壓源最快的響應時間為10us,無法在1ns時間里得到響應。這樣的后果是,負載還在嗷嗷待哺等待電流,穩壓源卻無法及時提供電流,總功率一定,電流增大了,于是電壓就會被拉下來,造成了軌道塌陷,因此噪聲就產生了。

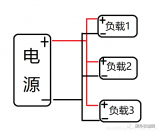

如何解決呢?方法是并聯不同容值的電容器。因為,穩壓源需要10us才能反應過來,所以在0-10us的時間里也不能干等著,需要用恰當的電容來補充。

比如按照50mohm的目標阻抗,可以計算出電容:

C=1/(2*PI*f*Z)=31.831uf

而電容的最高頻率同時可以計算出來,假設ESL為5nH,所以有f=Z/(2*PI*ESL)=1.6MHz。

也就是說加入31.831uf的電容,可以提供100KHz到1.6MHz頻段的去耦。另外,1/1.6MHz=0.625us,這樣一來,0.625us到10us這段時間電容能夠提供所需要的電流。10us之后,穩壓源能夠提高需要的穩定電流。

另外,加上一個大電容并不能滿足要求,通常還會放一些小電容,例如15個0.22uf的電容,可以提供高至100MHz的去耦,這些小電容的最快反應時間是1/100MHz=1ns,因此,這些電流能夠保證1us之后的電流需求。

此外,這個反應時間可能還不太夠,一般需要將退耦頻率提高到500MHz,也就是反應時間快到200ps,應該就安全了。計算方法,同上,不再贅述。感興趣的可以了解一些,目標阻抗de的計算,很有意思。

-

去耦電容

+關注

關注

11文章

319瀏覽量

22807 -

等效交流電阻

+關注

關注

0文章

1瀏覽量

1555

原文標題:從信號完整性角度看電容應用與計算

文章出處:【微信號:gh_bee81f890fc1,微信公眾號:面包板社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

什么是去耦電容?這些選擇技巧你得知道

什么是去耦電容?這些選擇技巧你得知道

評論