2. 高速柵極驅動電路

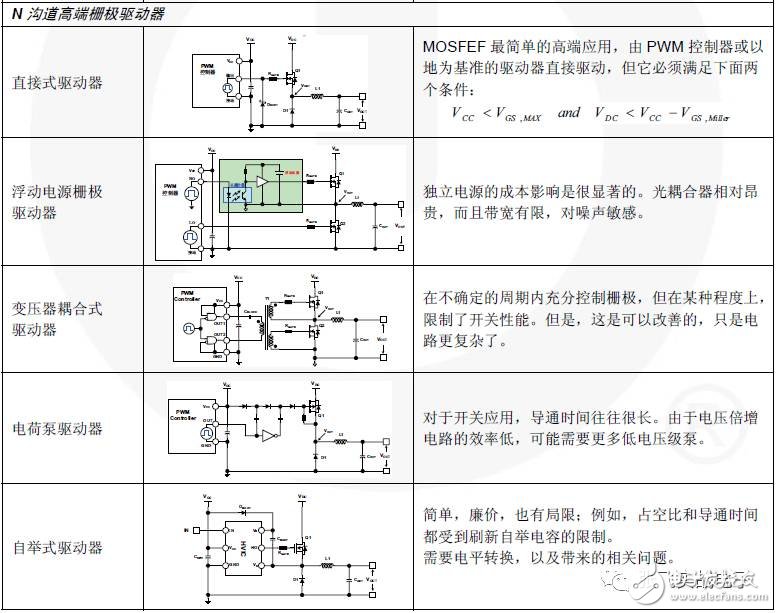

1自舉柵極驅動技術

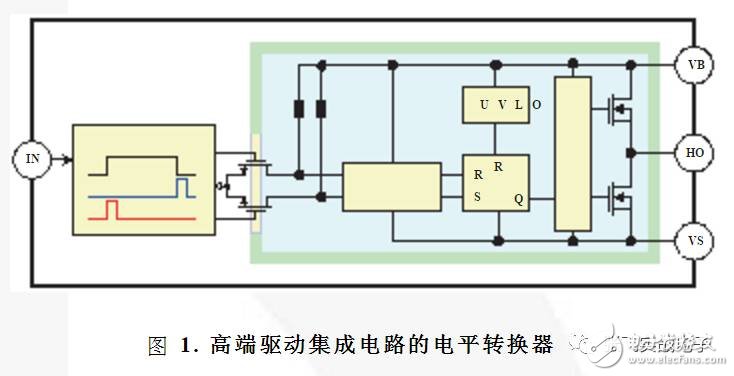

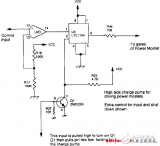

本節重點講在不同開關模式的功率轉換應用中,功率型MOSFET 和 IGBT 對自舉式柵極驅動電路的要求。當輸入電平不允許高端N 溝道功率型 MOSFET 或 IGBT 使用直接式柵極驅動電路時,我們就可以考慮自舉式柵極驅動技術。這種方法被用作柵極驅動和伴發偏置電路,兩者都以主開關器件的源極作為基準。驅動電路和偏置電路都在相對于器件源極的兩個輸入電壓之間擺動。但是,驅動電路和它的浮動偏置可以通過低壓電路實現,因為輸入電壓不會作用到這些電路上。驅動電路和接地控制信號通過一個電平轉換電路相連。該電平轉換電路必須允許浮動高端和接地低端電路之間存在高電壓差和一定的電容性開關電流。高電壓柵極驅動IC 通過獨特的電平轉換設計差分開。為了保持高效率和可管理的功耗,電平轉換電路在主開關導通期間,不能吸收任何電流。對于這種情況,我們經常使用脈沖式鎖存電平轉換器,如圖1 所示。

2自舉式驅動電路工作原理

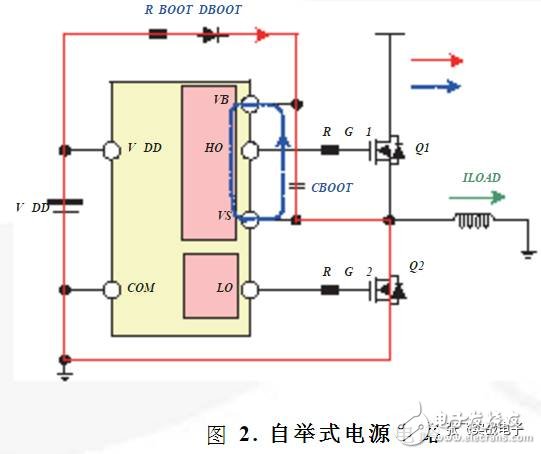

自舉式電路在高電壓柵極驅動電路中是很有用的,其工作原理如下。當VS降低到 IC 電源電壓 VDD或下拉至地時 (低端開關導通,高端開關關斷),電源VDD通過自舉電阻,RBOOT,和自舉二極管, DBOOT,對自舉電容CBOOT,進行充電,如圖 2 所示。當 VS被高端開關上拉到一個較高電壓時,由VBS對該自舉電容充電,此時,VBS電源浮動,自舉二極管處于反向偏置,軌電壓 (低端開關關斷,高端開關導通)和IC 電源電壓 VDD,被隔離開。

3自舉式電路的缺點

自舉式電路具有簡單和低成本的優點,但是,它也有一些局限。

占空比和導通時間受限于自舉電容CBOOT,刷新電荷所需時間的限制。

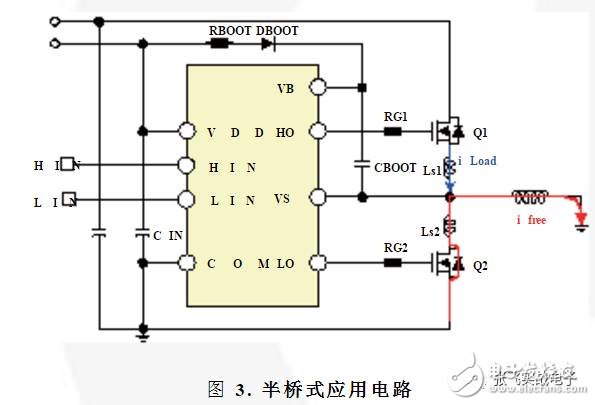

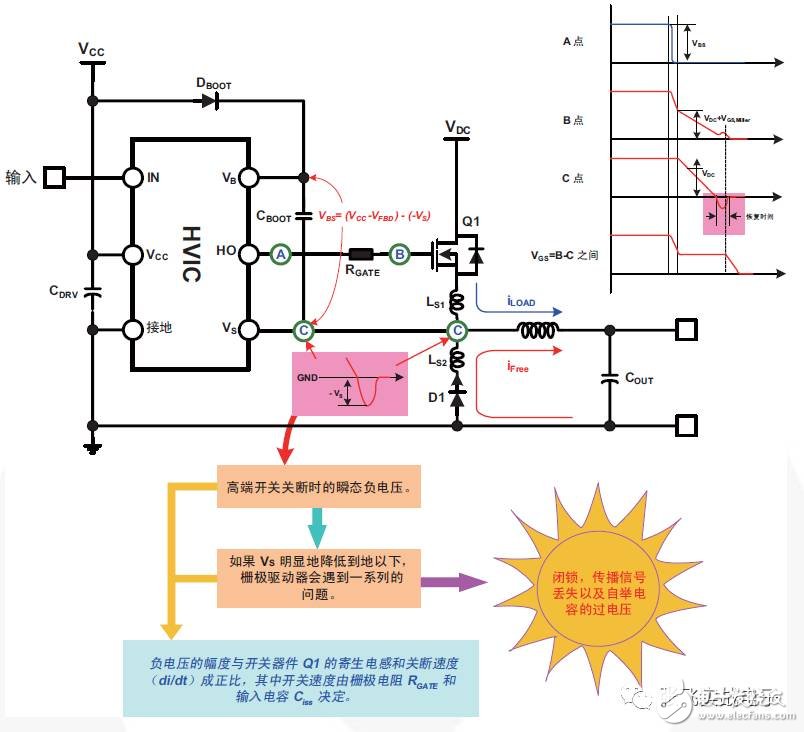

這個電路最大的難點在于:當開關器件關斷時,其源極的負電壓會使負載電流突然流過續流二極管,如圖3 所示。

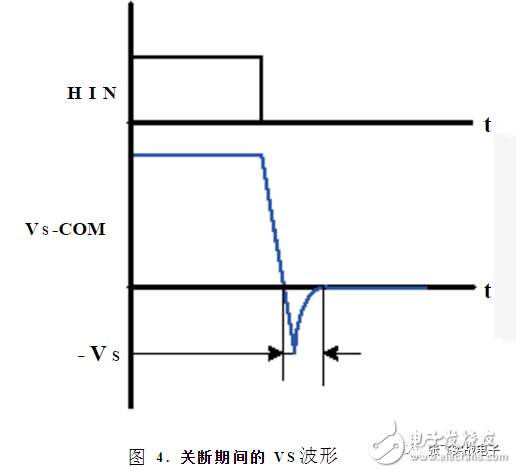

該負電壓會給柵極驅動電路的輸出端造成麻煩,因為它直接影響驅動電路或PWM 控制集成電路的源極VS引腳,可能會明顯地將某些內部電路下拉到地以下,如圖4 所示。另外一個問題是,該負電壓的轉換可能會使自舉電容處于過壓狀態。

自舉電容CBOOT,通過自舉二極管DBOOT,被電源 VDD瞬間充電。

由于VDD電源以地作為基準,自舉電容產生的最大電壓等于VDD加上源極上的負電壓振幅。

4VS引腳產生負電壓的原因

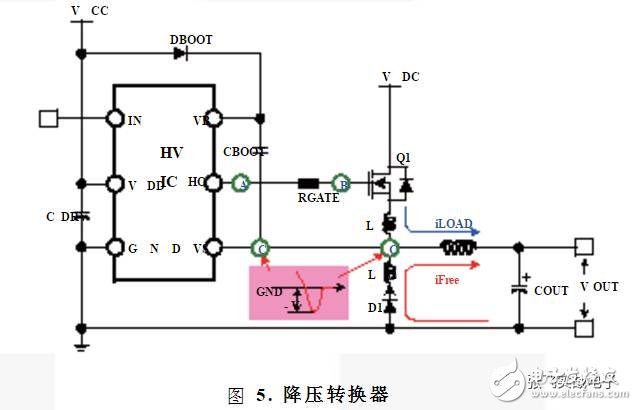

如圖5 所示,低端續流二極管的前向偏置是已知的將VS下低到COM (地)以下的原因之一。

主要問題出現在整流換向期間,僅僅在續流二極管開始箝壓之前。

在這種情況下,電感LS1 和 LS2 會將 VS壓低到 COM 以下,甚至超過如上所述的位置或正常穩態。

該負電壓的放大倍數正比于寄生電感和開關器件的關斷速度,di/dt ;它由柵極驅動電阻,RGATE和開關器件的輸入電容,Ciss決定。

Cgs 和 Cgd 的和,稱為密勒電容。

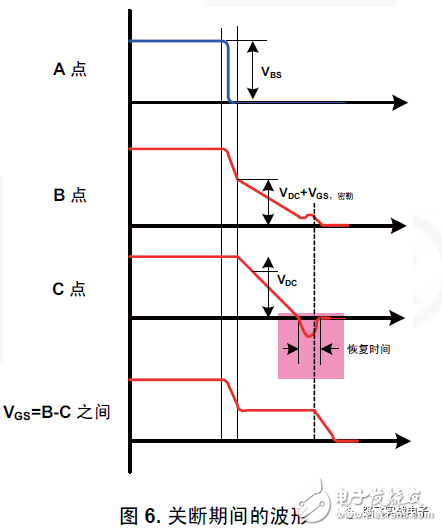

圖6 描述了高端 N 溝道 MOSFET 關斷期間的電壓波形。

5VS 引腳電壓下沖的影響

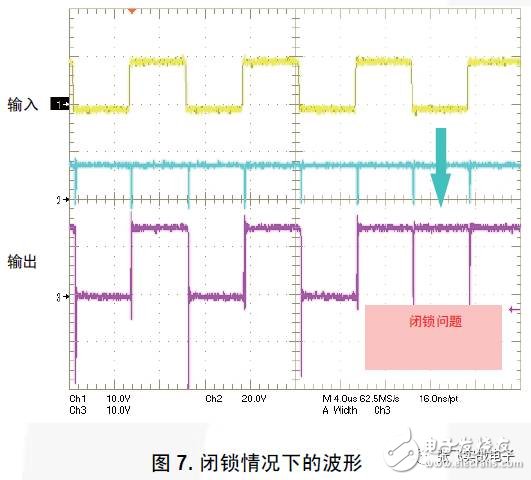

如果電壓下沖幅度超過規定的絕對最大額定值,柵極驅動集成電路受到損害,或者柵極驅動集成電路暫時鎖存現態。

圖7 顯示高端輸出信號沒有隨輸入信號而改變但發生閉鎖現象,此時,半橋電路中的外部主高端和低端開關處于短路狀態。

如果VS 電壓下沖沒有超過規定的絕對最大額定值,柵極驅動IC 不會受到損害。然而,當 VS 處于如圖 8 所示的下沖狀態時,高端輸出不會對輸入轉換作出響應。在這種情況下,高端柵極驅動電路的電平轉換器不會受到工作電壓余量不足的影響。需要注意的是,大多數事實證明高端通常不需要在一個開關動作之后立即改變狀態。

6考慮閉鎖效應

最完整的高電壓柵極驅動集成電路都含有寄生二極管,它被前向或反向擊穿,就可能導致寄生SCR 閉鎖。閉鎖效應的最終結果往往是無法預測的,破壞范圍從器件工作時常不穩定到完全失效。柵極驅動集成電路也可能被初次過壓之后的一系列動作間接損壞。例如,閉鎖導致兩輸出驅動同時置于高態,造成交叉傳導,從而導致開關故障,并最終使柵極驅動器集成電路遭受災難性破壞。如果功率轉換電路和/ 或柵極驅動集成電路受到破壞,這種失效模式應被考慮成一個可能的根本原因。下面的理論極限可用來幫助解釋VS電壓嚴重不足和由此產生閉鎖效應之間的關系。

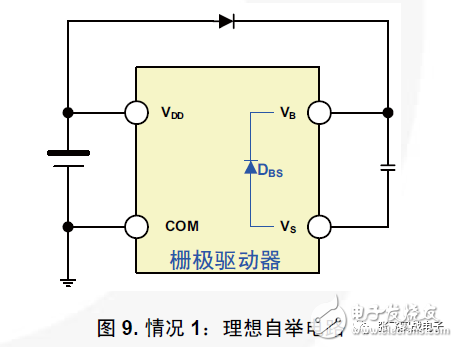

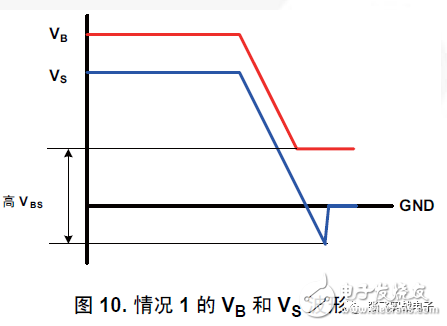

在第一種情況中,使用了一個 “理想自舉電路”,該電路的VDD由一個零歐姆電源驅動,通過一個理想二極管連接到VB,如圖 9 所示。當大電流流過續流二極管時,由于di/dt 很大,VS電壓將低于地電壓。這時,閉鎖危險發生了,因為柵極驅動器內部的寄生二極管DBS,最終沿VS到 VB方向導通,造成下沖電壓與 VDD疊加,使得自舉電容被過度充電,如圖10 所示。

例如:如果VDD=15V, VS下沖超過 10V,迫使浮動電源電壓在25V 以上,二極管DBS有被擊穿的危險,進而產生閉鎖。

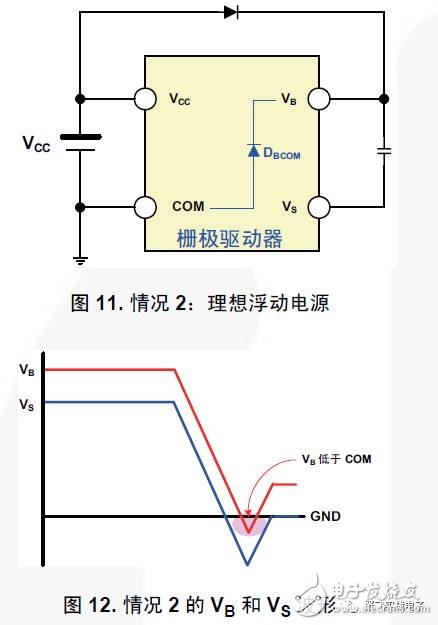

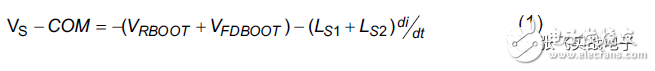

假想自舉電源被理想浮動電源替代,如圖11 所示,這時,VBS在任何情況下都是恒定的。注意利用一個低電阻輔助電源替代自舉電路,就能實現這種情況。這時,如果VS過沖超過數據表 (datasheet) 規定的最大 VBS電壓,閉鎖危險就會發生,因為寄生二極管DBCM最終沿COM 端到VB方向導通,如圖 12 所示。

一種實用的電路可能處在以上兩種極限之間,結果是VBS電壓稍微增大,和 VB稍低于VDD,如圖 13 所示。

準確地說,任何一種極限情況都是流行的,檢驗如下。如果VS過沖持續時間超過 10 個納秒,自舉電容CBOOT被過充電,那么高端柵極驅動器電路被過電壓應力破壞,因為VBS 電壓超過了數據表指定的絕對最大電壓(VBSMAX) 。設計一個自舉電路時,其輸出電壓不能超過高端柵極驅動器的絕對最大額定電壓。

7寄生電感效應

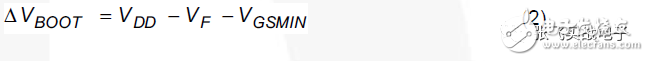

負電壓的振幅是:

為了減小流過寄生電感的電流隨時間變化曲線的斜度,要使等式1 中的導數項最小。

例如:一個10 安培, 25V 的柵極驅動器,它的寄生電感是100nH,如果在 50ns 內開關,那么 VS與地之間的負電壓尖峰是20V。

3. 自舉部件的設計流程1選擇自舉電容

自舉電容(CBOOT) 在低端驅動器導通,輸出電壓低于柵極驅動器的電源電壓(VDD) 時每次都被充電。自舉電容僅當高端開關導通的時候放電。自舉電容給高端電路提供電源(VBS)。首先要考慮的參數是高端開關處于導通時,自舉電容的最大電壓降。允許的最大電壓降(VBOOT) 取決于要保持的最小柵極驅動電壓 (對于高端開關) 。如果VGSMIN是最小的柵 - 源極電壓,電容的電壓降必須是:

其中:

VDD = 柵極驅動器的電源電壓;

VF = 自舉二極管正向電壓降 [V]

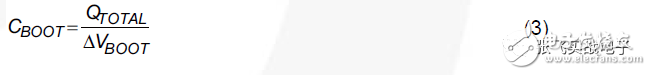

計算自舉電容為:

其中QTOTAL是電容器的電荷總量。自舉電容的電荷總量通過等式4 計算:

其中:

QGATE= 柵極電荷的總量

ILKGS= 開關柵 - 源級漏電流;

ILKCAP= 自舉電容的漏電流;

IQBS= 自舉電路的靜態電流;

ILK= 自舉電路的漏電流;

QLS= 內部電平轉換器所需要的電荷,對于所有的高壓柵

極驅動電路,該值為3nC ;

tON= 高端導通時間;和

ILKDIODED= 自舉二極管的漏電流;

電容器的漏電流,只有在使用電解電容器時,才需要考慮,否則,可以忽略不計。

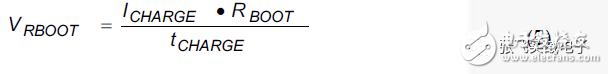

2選擇自舉電阻

當使用外部自舉電阻時,電阻 RBOOT帶來一個額外的電 壓降:

其中:

ICHARGE= 自舉電容的充電電流;

RBOOT= 自舉電阻;和

tCHARGE= 自舉電容的充電時間 ( 低端導通時間 )

該電阻值 (一般5~10Ω)不能太大,否則會增加 VBS時間常數。當計算最大允許的電壓降(VBOOT) 時,必須考慮自舉二極管的電壓降。如果該電壓降太大或電路不能提供足夠的充電時間,我們可以使用一個快速恢復或超快恢復二極管。

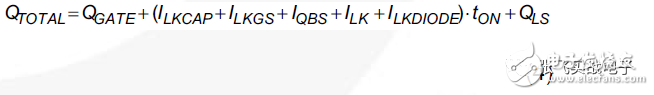

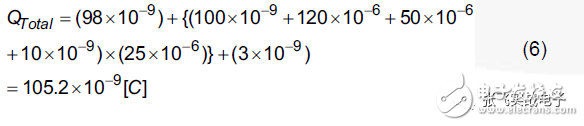

例如 :當使用外部自舉二極管時,估算自舉電容的大小。

柵極驅動

IC=FAN7382

開關器件

=FCP20N60

自舉二極管

=UF4007

VDD=15V

QGATE= 98nC (最大值)

ILKGS= 100nA (最大值)

ILKCAP= 0 (陶瓷電容)

IQBS= 120A (最大值)

ILK= 50A (最大值)

QLS= 3nC

TON=25s (fs=20KHz,占空比 =50%)

ILKDIODE= 10nA

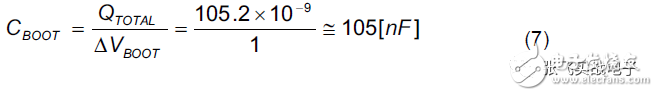

如果自舉電容器在高端開關處于開啟狀態時,最大允許的電壓降是1.0V,最小電容值通過等式 3 計算。

自舉電容計算如下:

外部二極管導致的電壓降大約為0.7V。假設電容充電時間等于高端導通時間 (占空比50%)。根據不同的自舉電容值,使用以下的等式:

推薦的電容值是100nF ~ 570nF,但是實際的電容值必須根據使用的器件來選擇。如果電容值過大,自舉電容的充電時間減少,低端導通時間可能不足以使電容達到自舉電壓。

4. 考慮自舉應用電路1自舉啟動電路

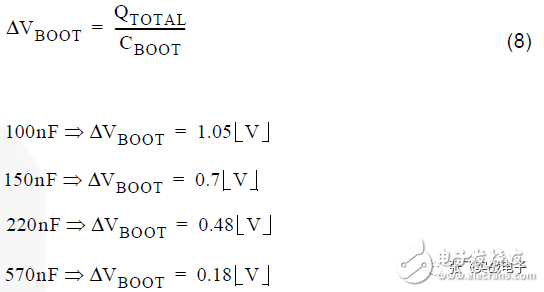

如圖 1 所示,自舉電路對于高電壓柵極驅動器是很有用 的。但 是,當 主 要 MOSFET (Q1) 的源極和自舉電容 (CBOOT) 的負偏置節點位于輸出電壓時,它有對自舉電 容進行初始化啟動和充電受限的問題。啟動時,自舉二 極管 (DBOOT) 可能處于反偏,主要 MOSFET (Q1) 的導 通時間不足,自舉電容不能保持所需要的電荷,如圖 1 所示。

在某些應用中,如電池充電器,輸出電壓在輸入電源加載到轉換器之前可能已經存在了。給自舉電容(CBOOT)提供初始電 荷也許是不可能 的,這 取 決于電源電壓(VDD) 和輸出電壓 (VOUT) 之間的電壓差。假設輸入電壓(VDC) 和輸出電壓 (VOUT) 之間有足夠的電壓差,由啟動電阻(RSTART),啟動二極管 (DSTART) 和齊納二極管(DSTART) 組成的電路,可以解決這個問題,如圖 14 所示。在此啟動電路中,啟動二極管DSTART充當次自舉二極管,在上電時對自舉電容(CBOOT) 充電。自舉電容(CBOOT) 充電后,連接到齊納二極管DZ,在正常工作時,這個電壓應該大于驅動器的電源電壓(VDD) 。啟動電阻限制了自舉電容的充電電流和齊納電流。為了獲得最大的效率,應該選擇合適的啟動電阻值使電流極低,因為電路中通過啟動二極管的自舉路徑是不變的。

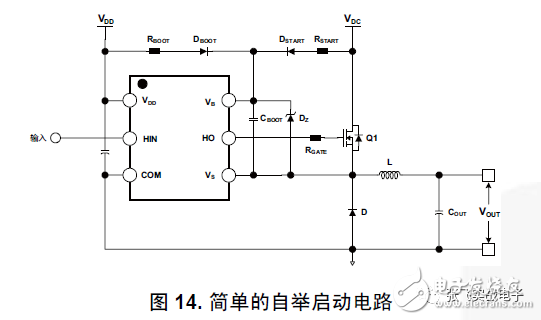

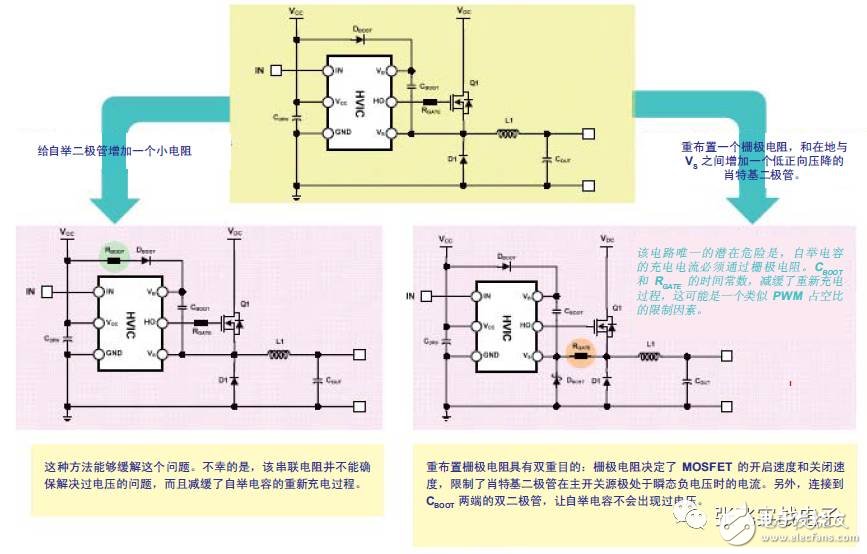

2自舉二極管串聯電阻

在第一個選項中,自舉電路包括一個小電阻, RBOOT,它 串聯了一個自舉二極管,如圖 15所示。自舉電阻RBOOT, 僅在自舉充電周期用來限流。自舉充電周期表示 VS降到 集成電路電源電壓 VDD以下,或者 VS被拉低到地 (低 端開關導通,高端開關關閉)。電源 VDD,通過自舉電 阻 RBOOT和二極管 DBOOT,對自舉電容 CBOOT充電。自 舉二極管的擊穿電壓 (BV) 必須大于 VDC,恢復時間足夠 快,以減少自舉電容反饋給電源 VCC的電荷。

這是一種簡單的,限制自舉電容初次充電電流的方法,但是它也有一些缺點。占空比受限于自舉電容CBOOT刷新電荷所需要的時間,還有啟動問題。該電阻值 (一般5~10Ω)不能太大,否則會增加 VBS時間常數。最低導通時間,即給自舉電容充電或刷新電荷的時間,必須匹配這個時間常數。該時間常數取決于自舉電阻,自舉電容和開關器件的占空比,用下面的等式計算:

其中RBOOT是自舉電阻; CBOOT是自舉電容; D 是占空比。

例如,RBOOT=10,CBOOT=1F 和 D=10% ;時間常數計算如下:

即使連接一個合理的大自舉電容和電阻,該時間常數可能增大。這種方法能夠緩解這個問題。不幸的是,該串聯電阻不能解決過電壓的問題,并且減緩了自舉電容的重新充電過程。

3VS 與 VOUT 之間的電阻

在第二個選項中,自舉電路的VS和 VOUT之間,添加上一個小電阻RVS,如圖 16 所示。RVS的建議值在幾個歐姆左右。

RVS不僅用作自舉電阻,還用作導通電阻和關斷電阻,如圖17。自舉電阻,導通電阻和關斷電阻通過下面的等式計算:

4VS箝壓二極管和重布置柵極電阻

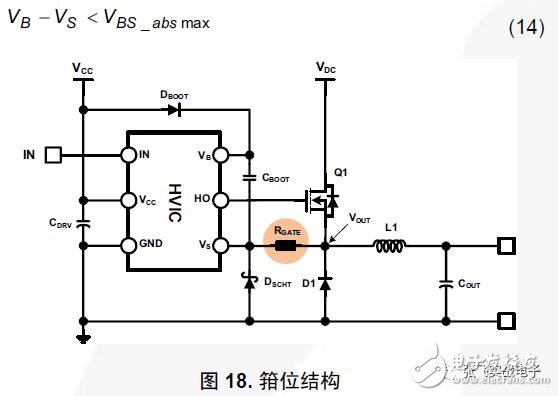

在第三個選項中,自舉電路把柵極電阻重新布置到VS和VOUT之間,并且在 VS和地之間增加一個低正向壓降的肖特基二極管,如圖18 所示。VB和 VS之間的電壓差,應保持在數據表規定的絕對最大額定值范圍內,并且必須符合下列等式:

5重布置柵極電阻;雙重目的

柵極電阻設置了 MOSFET 的導通速度和關斷速度,限制 了在主開關源極的電壓負向瞬變時,肖特基二極管的電 流。另外,連接到 CBOOT兩端的雙二極管,確保自舉電 容不會出現過電壓。該電路唯一的潛在危險是,自舉電 容的充電電流必須流過柵極電阻。 CBOOT和 RGATE的時 間常數,減緩了電容重新充電過程,這可能是一個類似 PWM 占空比的限制因素。

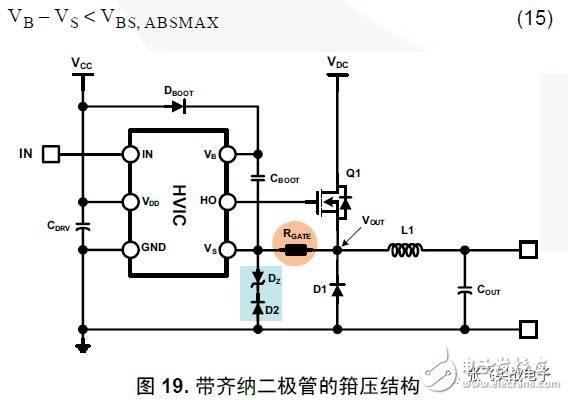

第四個選擇,包括在VS和 VOUT之間,重新布置一個柵極電阻,以及在VS和地之間放置一個箝壓器件,如圖 19所示,布置了一個齊納二極管和600V 二極管。根據下列規則,量化齊納電壓:

對于每一種額定驅動電流,計算指定時間內所能切換的最大柵極電荷QG,如表 1 所示。

說明:

1. 一個單通道 4A 的 HVIC,等同一個雙通道 2A 的HVIC!

例如,100ns 的開關時間是:

100KHz 時,轉換電路開關周期的 1% ;

300KHz 時,轉換電路開關周期的 3% ;

1. 所需的額定柵極驅動電流取決于在開關時間 tSW_ON/OFF內,必須移動的柵極電荷數 QG(因為開關期間的平均柵極電流是IG) :

2. 最大柵極電荷 QG,從 MOSFET 數據表得到。

如果實際的柵極驅動電壓VGS與規格表中的測試條件不同,我們可以用VGS與 QG關系曲線的值代替。數據表中的值乘上并聯的MOSFET 數量就是所需的值。

3. tSW_ON/OFF表示所需的 MOSFET 開關速度。如果該值未知,取開關周期tSW的 2%:

如果通道(V-I) 開關損耗主要受開關轉換(導通或關斷)支配,需要根據轉換調整驅動器。對于受箝制的電感性開關(通常情況),每次轉換的通道開關損耗估算如下:

其中

VDS和 ID是每個開關間期的最大值。

4. 柵極驅動器的近似電流驅動能力計算如下

(1) 拉電流能力 (導通)

(2) 灌電流能力 (關斷)

其中:

QG=VGS= VDD時, MOSFET 的柵極電荷;

tSW_ON/OFF=MOSFET 開關導通 / 關斷時間;和

1.5= 經驗因子 (受通過驅動器輸入級的延遲和寄生效應的影響)

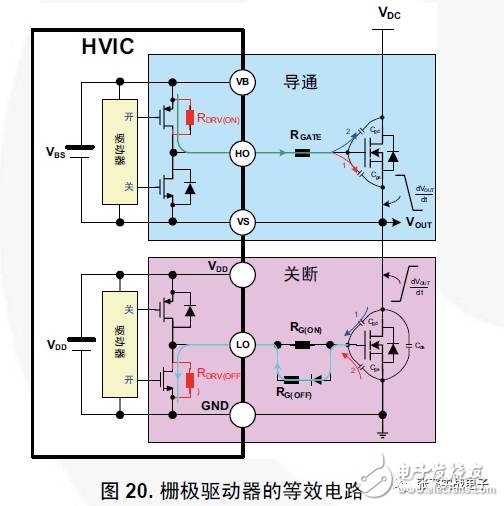

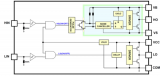

6. 柵極電阻設計流程輸出晶體管的開關速度受導通和關斷柵極電阻的控制,這些電阻控制了柵極驅動器的導通和關斷電流。本節描述了有關柵極電阻的基本規則,通過引入柵極驅動器的等效輸出電阻來獲取所需的開關時間和速度。圖20 描述了柵極驅動器的等效電路和在導通和關斷期間的電流流動路徑,其中包括柵極驅動器和開關器件。

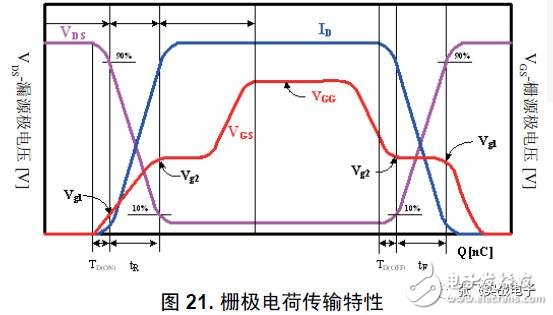

圖21 顯示了開關器件在導通和關斷期間的柵極 - 電荷傳輸特性。

1量化導通柵極電阻

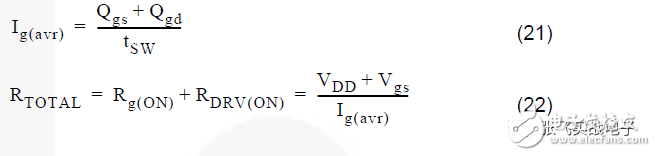

根據開關時間tsw,選擇導通閘極電阻 Rg(ON),以獲得所需的開關時間。根據開關時間確定電阻值時,我們需要知道電源電壓VDD(或 VBS),柵極驅動器的等效導通電阻(RDRV(ON)),和開關器件的參數 (Qgs, Qgd, and Vgs(th))。

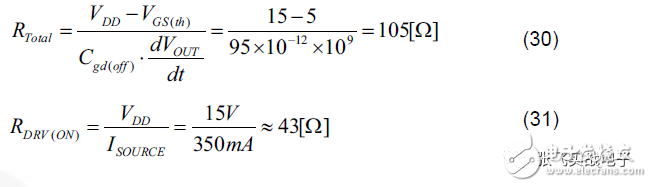

開關時間定義為到達平臺電壓(給MOSFET 提供了總共Qgd+ Qgd的電荷)末端所花費的時間,如圖 21 所示。導通柵極電阻計算如下:

其中Rg(ON)是柵極導通電阻,RDRV(ON)是驅動器的等效導通電阻。

2輸出電壓斜率

導通柵極電阻Rg(ON)通過控制輸出電壓斜率 (dVOUT/dt)來決定。當輸出電壓是非線性時,最大輸出電壓斜率可以近似為:

插入變形表達式Ig(avr),并整理得到:

其中Cgd(off)是密勒效應電容,在數據表中定義為 Crss。

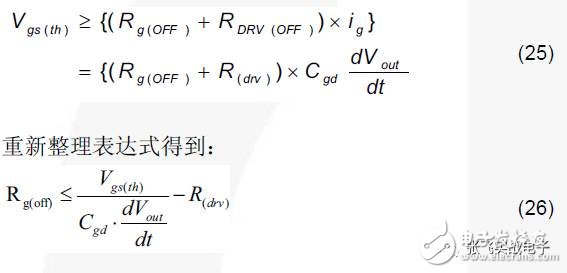

3量化關斷柵極電阻

在量化關斷電阻時,最壞的情況是當MOSFET 漏極處于關斷時,外部動作迫使電阻整流。

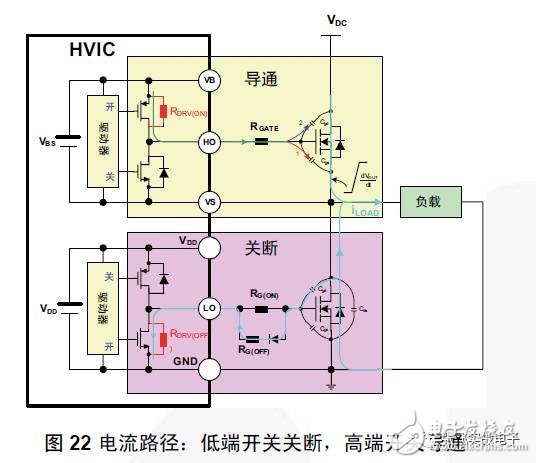

在這種情況下,輸出節點的dv/dt,誘導一股寄生電流穿過Cgd,流向 RG(OFF)和 RDRV(OFF),如圖 22 所示。

下面闡述了,當輸出dv/dt 是由伴隨 MSOFET 的導通造成時,如何量化關斷電阻,如圖22 示。

因為這個原因,關斷阻抗必須根據最壞的應用情況來量化。下面的等式將MOSFET 柵極閾值電壓和漏極 dv/dt關聯起來:

4設計實例

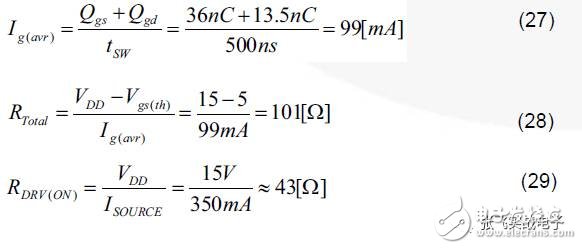

使用飛兆的MOSFET FCP20N60 和柵極驅動器 FAN7382, 確定導通和關斷柵極電阻。 FCP20N60 功率 MOSFET 的 參數如下:

Qgs=13.5nC, Qgd=36nC, Cgd=95pF, VGS(th)=5V,VGS(th)MIN=3V

4.1 導通柵極電阻

1) 如果 VDD=15V 時,所需的開關時間是 500ns,計算平均柵極充電電流:

導通電阻值大約是58Ω。

2)如果VDD=15V時,dVout/dt=1V/ns,總柵極電阻計算為:

導通電阻值大約是62Ω。

4.2 關斷柵極電阻

如果dVout/dt=1V/ns,關斷柵極電阻可計算為:

1柵極驅動器的功耗

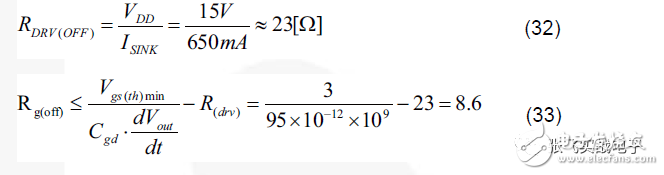

總的功耗包括柵極驅動器功耗和自舉二極管功耗。柵極驅動器功耗由靜態功耗和動態功耗兩部分組成。它與開關頻率,高端和低端驅動器的輸出負載電容,以及電源VDD有關。

靜態功耗是因為低端驅動器的電源VDD到地的靜態電流,以及高端驅動器的電平轉換階段的漏電流造成的。前者取決于VS端的電壓,后者僅在高端功率器件導通時與占空比成正比。

動態功耗定義如下:對于低端驅動器,動態功耗有兩個不同的來源。一是當負載電容通過柵極電阻充電或放電時,進入電容的電能有一半耗散在電阻上。柵極驅動電阻的 功耗,柵 極 驅動器內 部的和外部 的,以及內 部CMOS 電路的開關功耗。同時,高端驅動器的動態功耗也包括兩個不同的來源。一個是因為電平轉換電路,一個是因為高端電容的充電和放電。這里,可以忽略靜態功耗,因為集成電路的總功耗主要是柵極驅動IC 的動態功耗,可估算為:

圖23 顯示了當 VDD=15V 時,根據不同頻率和負載電容,估算的柵極驅動器功耗。這個曲線可以用來近似柵極驅動器的功耗。

自舉電路的功耗是自舉二極管功耗和自舉電阻功耗的總和,如果它們存在的話。自舉二極管的功耗是對自舉電容充電時產生的正向偏置功耗與二極管反向恢復時產生的反向偏置功耗的總和。因為每個事件每個周期發生一次,所以二極管的功耗與開關頻率成正比。大電容負載需要更多的電流,對自舉電容器重新充電,從而導致更多的功耗。

半橋輸入電壓 (VDC)越高,反向恢復功耗越大。集成電路的總功耗可以估算為:柵極驅動器的功耗與自舉二極管的功耗的總和,減去自舉電阻的功耗。

如果自舉二極管在柵極驅動器內部的話,添加一個與內部自舉二極管并聯的外部二極管,因為二極管功耗很大。外部二極管必須放置在靠近柵極驅動器的地方,以減少串聯寄生電感,并顯著降低正向電壓降。

2封裝熱阻

電路設計者必須提供:

估算柵極驅動器封裝后的功耗

最高工作結溫度 TJ,MAX,OPR,比如對于驅動器是120°C,如果取 TJ,MAX=150°C 的 80%。

最高工作引腳焊錫溫度 TL,MAX,OPR,大約等于驅動器下最大PCB 溫度,比如 100°C。

最大允許結到引腳的熱阻計算為:

1印刷電路板版圖

具有最小寄生電感的版圖如下:

開關之間的走線沒有回路或偏差。

避免互連鏈路。它會顯著增加電感。

降低封裝體距離 PCB 板的高度,以減少引腳電感效應。

考慮所有功率開關的配合放置,以減少走線長度。

去耦電容和柵極電阻的布局和布線,應盡可能靠近柵極驅動集成電路。

自舉二極管應盡可能靠近自舉電容。

2自舉部件

在量化自舉阻抗和初次自舉充電時的電流時,必須考慮自舉電阻(RBOOT)。如果需要電阻和自舉二極管串聯時,首先確認VB不會低于 COM (地),尤其是在啟動期間和極限頻率和占空比下。

自舉電容(CBOOT) 使用一個低 ESR 電容,比如陶瓷電容。VDD和 COM 之間的電容,同時支持低端驅動器和自舉電容的再充電。建議該電容值至少是自舉電容的十倍以上。

自舉二極管必須使用較低的正向壓降,為了快速恢復,開關時間必須盡可能快,如超高速。

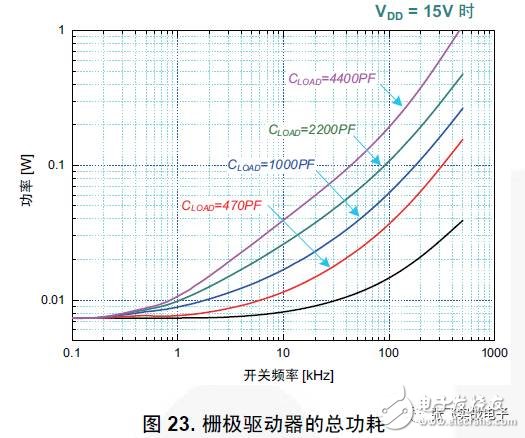

9.附錄高速柵極驅動電路總結

自舉電路問題的思考

自舉電路問題的補救措施

原文標題:非常好:高壓柵極驅動器自舉電路設計!

文章出處:【微信號:fcsde-sh,微信公眾號:fcsde-sh】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

豪威集團 天津 招聘模擬電路設計工程師

AN-6076供高電壓柵極驅動器IC使用的自舉電路的設計和使

高壓柵極驅動 IC 自舉電路的設計與應用指南

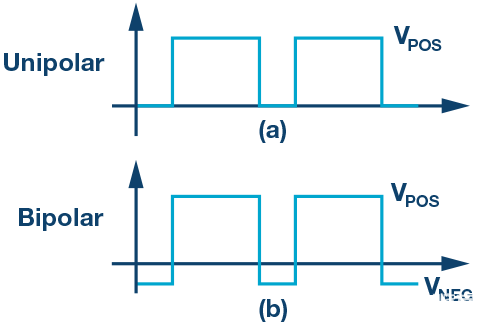

以雙極性方式驅動單極柵極驅動器

MOSFET和IGBT柵極驅動器電路之高側非隔離柵極驅動

工程師經驗之高壓柵極驅動器自舉電路設計

工程師經驗之高壓柵極驅動器自舉電路設計

評論