集成隔離電源isoPower?的iCoupler?數字隔離器采用隔離式DC-DC轉換器,能夠在125 MHz至200 MHz的頻率范圍內切換相對較大的電流。在這些高頻率下工作可能會增加對電磁輻射和傳導噪聲的擔心。

雖然,咱們官網上的應用筆記《isoPower器件的輻射控制建議》提供了最大限度降低輻射的電路和布局指南。實踐證明,通過電路優化(降低負載電流和電源電壓)和使用跨隔離柵拼接電容(通過PCB內層電容實現),可把峰值輻射降低25 dB以上。(ps.欲查看《isoPower器件的輻射控制建議》,點擊“閱讀原文”即可)

但是,倘若設計中具有多個isoPower器件并且布局非常密集,情況又將如何? 是否仍然能夠明顯降低輻射?這里,我們將針對此類情況提供一些一般指導原則。

由于內層拼接電容能夠構建低電感結構,因此最具優勢。在整體PCB區域受限的情況下,采用多層PCB就是很好的方式。采用盡可能多的層數切實可行,同時盡可能多的交疊電源層和接地層(參考層)。圖1為一個堆疊示例。

圖1.PCB層堆疊示例

埋層(原邊3、4層,副邊2至5層)可承載電力和接地電流。跨越隔離柵的交疊(例如原邊上的第4層GND和副邊上的第3層 V Iso)可形成理想的拼接電容。通過多層PCB堆疊可形成多個交疊,從而提高整體電容。為使電容最大,還必須減小參考層之間PCB電介質材料的厚度。

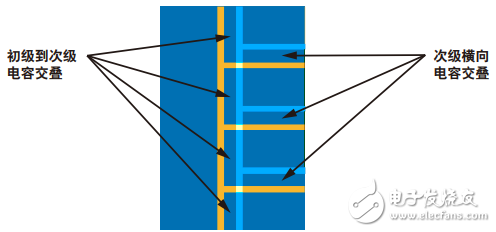

另一個布局技巧就是交疊相鄰的isoPower通道的各層。圖2顯示了一個具有四條相鄰通道的示例。

圖2.具有交疊拼接電容的四個相鄰通道

本示例中,每個輸出域與其他域隔離,但是我們仍能利用一些交疊電容。圖3顯示了這種堆疊,可看到每個isoPower器件可增加電容以及相鄰隔離區連接的情況。

圖3.具有交疊拼接電容的四個相鄰通道

必須確保內部和外部間隙要求符合最終應用。還可使用鐵氧體磁珠在任意電纜連接上提供過濾,從而減少可能產生輻射的天線效應。

總結如何在密集PCB布局中,最大限度降低多個isoPower器件的輻射?請參考以下幾個要點↓

-

最大程度降低每個通道的電源要求

-

在多個PCB層上構建拼接

-

采用盡可能多的PCB層切實可行

-

在各參考層間使用最薄的電介質

-

在相鄰域之間進行連接

-

確保內部和外部爬電距離仍然符合要求

-

電纜連接上提供過濾

-

pcb

+關注

關注

4351文章

23405瀏覽量

406533 -

isoPower

+關注

關注

0文章

8瀏覽量

8532

原文標題:如何在密集PCB布局中,最大限度降低多個isoPower器件的輻射

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如何做好非隔離式開關電源的PCB布局

AN101-最大限度地減少線性穩壓器輸出中的開關穩壓器殘留

TAS5630如何才能最大限度地減少電壓失調,或者調節為0?

最大限度地減少TRF7964A和TRF7970A省電模式下的電流消耗

最大限度地減少TPS53355和TPS53353系列器件的開關振鈴

最大限度地提高GSPS ADC中的SFDR性能:雜散源和Mitigat方法

利用TI GaN中的集成電流檢測功能更大限度提高系統效率

在密集PCB布局中,最大限度降低多個isoPower器件輻射的要點

在密集PCB布局中,最大限度降低多個isoPower器件輻射的要點

評論