SR鎖存器是一種基本的數字邏輯電路,用于存儲一位二進制信息。它由兩個觸發器(Set和Reset)組成,分別控制輸出Q和Q非。在這篇文章中,我們將探討SR鎖存器的Q非和Q*之間的關系,以及它們在數字電路設計中的應用。

- SR鎖存器的基本概念

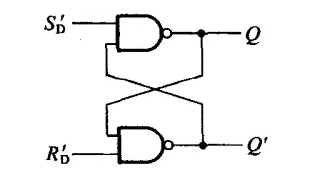

SR鎖存器是一種具有兩個輸入(Set和Reset)和兩個輸出(Q和Q非)的存儲單元。其中,Set輸入用于將Q置為高電平,Reset輸入用于將Q置為低電平。Q非是Q的反相輸出,即當Q為高電平時,Q非為低電平;當Q為低電平時,Q非為高電平。

- SR鎖存器的工作原理

SR鎖存器的工作原理可以通過以下步驟來理解:

2.1. 當Set輸入為高電平時,觸發器將Q置為高電平,Q非置為低電平。此時,SR鎖存器存儲了一位二進制信息“1”。

2.2. 當Reset輸入為高電平時,觸發器將Q置為低電平,Q非置為高電平。此時,SR鎖存器存儲了一位二進制信息“0”。

2.3. 當Set和Reset輸入都為低電平時,觸發器保持當前的Q和Q非狀態不變。這意味著SR鎖存器可以保持其存儲的信息。

- Q非和Q*的關系

Q非是Q的反相輸出,而Q是Q的互補輸出。在SR鎖存器中,Q非和Q具有以下關系:

3.1. 當Q為高電平時,Q非為低電平,Q*也為低電平。

3.2. 當Q為低電平時,Q非為高電平,Q*也為高電平。

3.3. 當Q保持不變時,Q非和Q*的狀態也保持不變。

- SR鎖存器的應用

SR鎖存器在數字電路設計中有廣泛的應用,以下是一些常見的應用場景:

4.1. 數據存儲:SR鎖存器可以用于存儲一位二進制數據,例如在寄存器、計數器等電路中。

4.2. 信號同步:在數字系統中,信號可能在不同的時鐘域中傳輸。使用SR鎖存器可以實現信號的同步,確保數據在正確的時鐘周期內被讀取。

4.3. 狀態機設計:在有限狀態機(FSM)設計中,SR鎖存器可以用于實現狀態的存儲和轉換。

4.4. 寄存器設計:在寄存器設計中,SR鎖存器可以用于實現寄存器的讀寫控制。

- SR鎖存器的優缺點

5.1. 優點:

5.1.1. 結構簡單:SR鎖存器由兩個觸發器組成,結構簡單,易于實現。

5.1.2. 存儲能力強:SR鎖存器可以存儲一位二進制信息,對于簡單的存儲需求足夠使用。

5.1.3. 應用廣泛:SR鎖存器在數字電路設計中有廣泛的應用,如數據存儲、信號同步等。

5.2. 缺點:

5.2.1. 存儲容量有限:SR鎖存器只能存儲一位二進制信息,對于需要存儲大量數據的應用場景,可能不夠使用。

5.2.2. 易受干擾:由于SR鎖存器的Set和Reset輸入是獨立的,當它們同時為高電平時,可能導致鎖存器進入不確定狀態,從而影響數據的穩定性。

5.2.3. 功耗較高:由于SR鎖存器需要兩個觸發器,其功耗相對于其他存儲單元(如D觸發器)可能較高。

- 結論

SR鎖存器是一種基本的數字邏輯電路,具有結構簡單、應用廣泛的特點。Q非和Q*是SR鎖存器的兩個重要輸出,它們之間的關系是互補的。雖然SR鎖存器在存儲容量和抗干擾能力方面存在一定的局限性,但在許多應用場景中,它仍然是一種有效的解決方案。

-

二進制

+關注

關注

2文章

803瀏覽量

42132 -

觸發器

+關注

關注

14文章

2032瀏覽量

61853 -

數字邏輯電路

+關注

關注

0文章

106瀏覽量

16036

發布評論請先 登錄

SR鎖存器的Q非和Q*是什么關系

SR鎖存器的Q非和Q*是什么關系

評論