在數字電路中,"clk"通常指的是時鐘信號(clock signal),它是一種周期性的信號,用于同步數字電路中的各種操作。時鐘信號的高低電平有效性取決于具體的電路設計和應用場景。

1. 時鐘信號的基本概念

時鐘信號是一種周期性變化的電壓信號,通常由一個時鐘發生器(clock generator)產生。在數字電路中,時鐘信號的主要作用是同步電路中的各種操作,確保數據在正確的時間被處理和傳輸。時鐘信號的頻率決定了數字電路的運行速度,頻率越高,電路的運行速度越快。

2. 時鐘信號的高低電平有效性

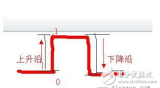

在數字電路中,時鐘信號的高低電平有效性是一個重要的設計參數。它決定了在時鐘信號的上升沿(從低電平到高電平的轉換)還是下降沿(從高電平到低電平的轉換)進行數據的采樣和傳輸。以下是兩種常見的時鐘信號有效性類型:

- 高電平有效(High-Level Active) :在這種設計中,時鐘信號的高電平表示有效狀態,數據在高電平期間被采樣和傳輸。這種設計通常用于簡單的同步電路和低速應用。

- 低電平有效(Low-Level Active) :在這種設計中,時鐘信號的低電平表示有效狀態,數據在低電平期間被采樣和傳輸。這種設計通常用于復雜的同步電路和高速應用。

3. 時鐘信號的同步與異步

在數字電路中,時鐘信號的同步與異步是兩種不同的設計方法:

- 同步(Synchronous) :在同步設計中,所有的操作都由單一的時鐘信號控制。這種設計可以簡化電路的邏輯,提高電路的穩定性和可靠性。然而,同步設計也可能導致電路的功耗增加,因為時鐘信號需要不斷地驅動電路中的所有部分。

- 異步(Asynchronous) :在異步設計中,不同的操作由不同的時鐘信號控制。這種設計可以提高電路的靈活性和可擴展性,但同時也增加了電路的復雜性和設計難度。異步設計通常用于需要高度靈活性和可擴展性的系統,如處理器和通信系統。

4. 時鐘信號在不同應用中的作用

時鐘信號在數字電路中的應用非常廣泛,以下是一些典型的應用場景:

- 微處理器(Microprocessors) :在微處理器中,時鐘信號用于控制指令的執行和數據的傳輸。微處理器的時鐘頻率通常非常高,以確保處理器能夠快速地執行復雜的計算任務。

- 存儲器(Memory) :在存儲器中,時鐘信號用于控制數據的讀寫操作。存儲器的時鐘頻率通常較低,以確保數據的穩定性和可靠性。

- 通信系統(Communication Systems) :在通信系統中,時鐘信號用于同步數據的傳輸和接收。通信系統的時鐘頻率通常非常高,以確保數據的傳輸速率和通信質量。

- 音頻和視頻處理(Audio and Video Processing) :在音頻和視頻處理中,時鐘信號用于控制信號的采樣和處理。音頻和視頻處理的時鐘頻率通常較低,以確保信號的質量和同步性。

5. 時鐘信號的穩定性和可靠性

時鐘信號的穩定性和可靠性對于數字電路的性能至關重要。以下是一些影響時鐘信號穩定性和可靠性的因素:

-

低電平

+關注

關注

1文章

175瀏覽量

13588 -

時鐘信號

+關注

關注

4文章

465瀏覽量

29059 -

高電平

+關注

關注

6文章

198瀏覽量

21888 -

CLK

+關注

關注

0文章

127瀏覽量

17516

發布評論請先 登錄

數字電路為什么是低電平有效的多

PWM的輸入是高電平有效還是低電平有效的?

低電平和高電平的區別

解密:數字電路為什么是低電平有效的多?

邏輯芯片輸入的低電平有效和高電平有效

電子設計(4)高電平、低電平復位電路

為什么單片機管腳設計成低電平才有效

高電平、低電平復位電路

clk是高電平有效還是低電平有效

clk是高電平有效還是低電平有效

評論