與同級內核相比,CodasipL110每瓦性能提高50%,代碼規模縮小20%

德國慕尼黑,2024年6月4日— RISC-V定制計算領域的領導者Codasip推出了新的低功耗嵌入式處理器核和新一代處理器設計自動化工具集CodasipStudio。Codasip L110為功耗敏感應用提供了同類最佳的性能。此外,客戶還可以輕松添加其獨特的定制功能,以實現前所未有的特定于應用程序的PPA(功率、性能和面積)改進。Codasip Studio Fusion中的一個新的定制級別,即Bounded customization,使客戶能夠將高質量、經過充分驗證的定制RISC-V核快速推向市場。因為其基準內核的功能完全得到了保證,在用新指令進行擴展時無須擔心風險,全新的驗證框架大大簡化了自定義指令的驗證流程。

Codasip首席商務官BrettCline表示:“RISC-V核的定制技術使芯片設計人員能夠引入針對其特定軟件工作負載的新指令,并顯著改善PPA。”。“我們的L110新核為小面積和低功耗應用程序提供了一流的性能,同時還提供便利快捷定制技術,該定制對既有核心功能沒有風險影響。我們以靈活的商業模式提供以上技術,避免客戶為定制計算付出高昂的代價。”

新CodasipL110 RISC-V CPU核帶來新游戲方式

與市場上的同級內核相比,Codasip L110每瓦性能提高了50%,代碼規模縮小了20%。L110提供了廣泛的配置選項,允許采取不同的面積/性能取舍策略,并支持標準RISC-V代碼規模擴展。此外,L110是完全可定制的,允許芯片設計人員根據需求改進處理器以實現有針對性的顯著PPA提升,使其設計的產品與眾不同。L110由Codasip團隊使用Codasip Studio Fusion設計,非常適合小面積、低功耗的應用,如狀態機替代、傳感器控制器和物聯網邊緣設備等。

Codasip StudioFusion引入了獨特的處理器設計和驗證功能,具有無與倫比的生產力

多年來,Codasip Studio一直是從同一處理器模型生成RTL和軟件開發工具的工具集。新版本Codasip Studio Fusion在此基礎上進一步發展,并添加了一個新劃分層。客戶可以從集合選項配置CPU核,在集合范圍內創建自定義指令,或者自由設計。這些工具自動生成包括編譯器、仿真模型、調試器和分析器的SDK(軟件開發工具包),以及包括RTL、驗證框架等的HDK(硬件開發工具包)。

最新版本還引入了更多的設計自動化,使處理器設計更加簡單快捷。新的設計結構允許融合處理器的架構和微體系結構描述。該工具集還可以自動將通用處理器方面的陳述性描述轉換為基本邏輯單元。

Codasip Studio Fusion工具集的優勢都體現在新的L110核中,它可以作為預先驗證的起點來實現正確的定制級別。對于需要更高性能起點的客戶,Codasip提供了其他選項,如64位的RISC-V應用處理器核A730。

審核編輯:彭菁

-

自動化

+關注

關注

29文章

5738瀏覽量

81572 -

嵌入式處理器

+關注

關注

0文章

256瀏覽量

31120 -

codasip

+關注

關注

0文章

37瀏覽量

6431

原文標題:Codasip為高能效應用帶來最新RISC-V核

文章出處:【微信號:Codasip 科達希普,微信公眾號:Codasip 科達希普】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

AMD EPYC嵌入式9005系列處理器發布

飛騰D2000 8核處理器嵌入式工控機G104-F:賦能工業自動化的強勁引擎

國產海光 3330E/4 核賦能工業智能化無風扇嵌入式工控機G500

低功耗處理器的優勢分析

ARM嵌入式通信協議及應用

基于全志T113-i多核異構處理器的全國產嵌入式核心板簡介

AMD推出EPYC Embedded霄龍嵌入式8004系列處理器

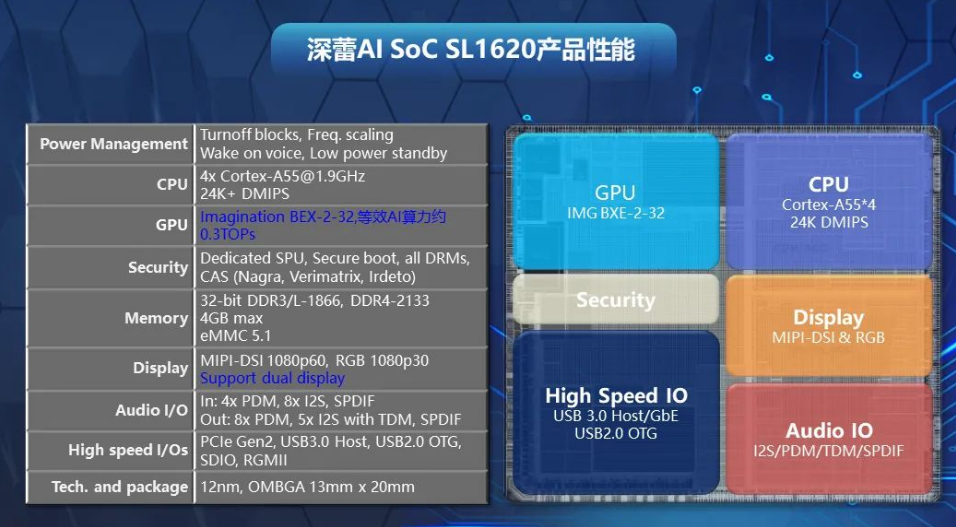

深蕾半導體Astra? SL1620嵌入式物聯網處理器詳細介紹

EsDA,一站式嵌入式軟件

Codasip推出低功耗嵌入式處理器核和設計自動化工具集CodasipStudio

Codasip推出低功耗嵌入式處理器核和設計自動化工具集CodasipStudio

評論