今日正文

(1)怎么看ADC

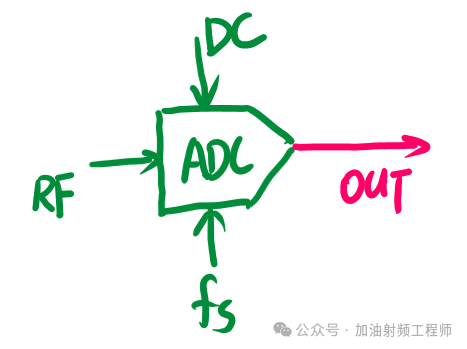

一個ADC,可以把它簡單的看成這樣一個器件,三個輸入,一個輸出。

一個輸出為數字采樣信號輸出。

(2)ADC的電源選型

市面上有很多型號的LDO和DC-DC,到底應該選擇哪種呢。按理說,指標最高的一般都沒問題,但是關鍵指標高的那不是貴么?所以要是能選個指標沒那么好,但是和所用ADC搭配剛剛好的器件,那不是又便宜又性能OK么?

與ADC的電源選型相關的,就是ADC的PSSR和PSMR。

當噪聲從ADC的電源端引入的時候,噪聲可能會直接出現在ADC的輸出端,也有可能是噪聲與模擬輸入信號產生的調制信號出現在ADC的輸出端。

舉個例子,假設疊加在DC上的噪聲信號的頻率為1MHz,模擬輸入信號為100MHz,而PSSR關注的是ADC輸出端的1MHz頻率處的幅度,而PSMR則關注的是ADC輸出端在101MHz和99MHz頻率處的幅度。

ADC廠家的手冊上,很多都沒有PSSR和PSMR的詳細指標。

如果我們對LDO和DCDC的成本敏感的話,比如說出貨量很大,單個器件省點就能省下一大筆錢的話,可能就需要自己做些預研工作,測試一下ADC的PSSR和PSMR隨頻率變化的曲線,以此來選擇合適的電源器件。

如果不敏感的話,可能就不費那個事了,直接高指標的電源器件+高抑制的電源濾波,完事。

(3)ADC的時鐘電路

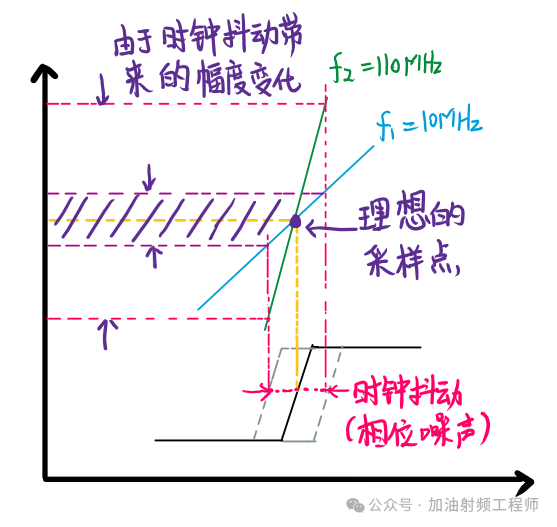

如上圖所示,當時鐘邊沿有抖動的時候,采樣的時刻也會有抖動,這樣對應的采樣數據也會有抖動,而且輸入頻率越高,由于時鐘抖動帶來的幅度變化越大。

所以,在評估ADC的時鐘是否符合要求的時候,需要綜合考慮時鐘的抖動帶來的影響。

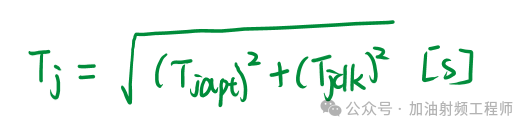

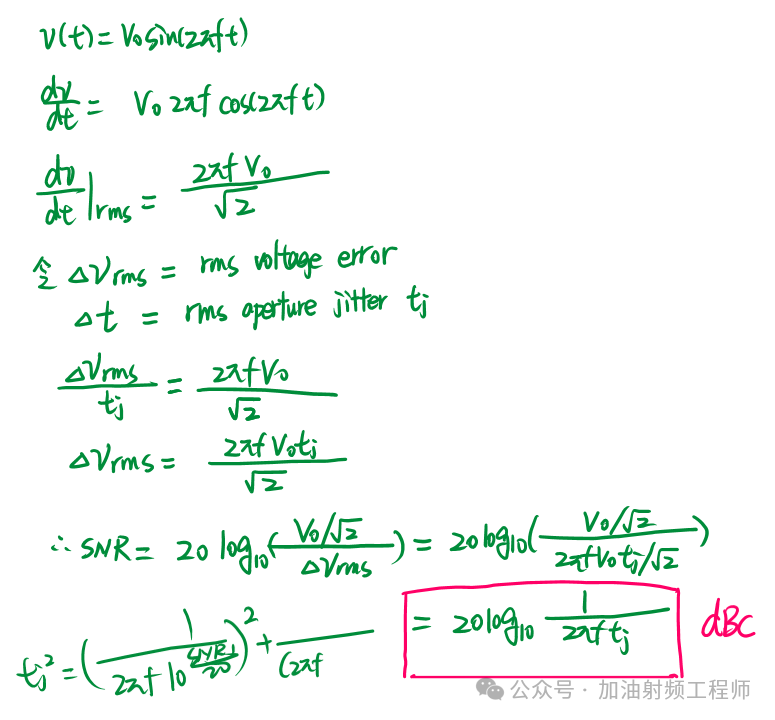

采樣時鐘抖動Tj是由時鐘源(Tjclk)和內部ADC孔徑抖動(Tjapt)產生的抖動的組合,即:

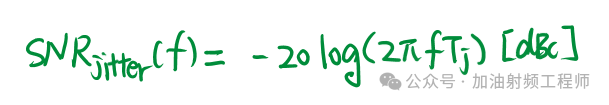

由總抖動導致的ADC的SNR下降,可按以下公式進行計算:

具體推導如下:

這個公式,是假定影響ADC的SNR的只有抖動本身,而ADC的SNR為無窮大。

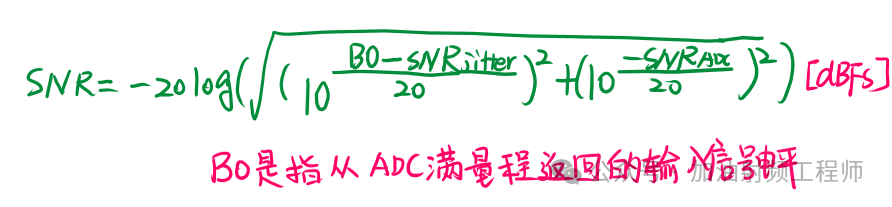

但是,ADC本身受量化噪聲和熱噪聲的影響,所以自身有一個SNR,假設為SNRADC,則:

這邊的單位會有點繞,本質上就是由抖動計算出來的SNR的單位是dBc,也就是說以信號的大小為基準的;但是加上ADC本身的SNR之后,由于手冊上計算SNR時,都是基于-1dBFS來得到的,所以兩者結合起來的時候,劃歸到統一的單位,即dBFS,所以會有BO這一項。

(4)ADC的輸入電路

對ADC的輸入電路進行設計的時候,需要根據具體要求,來設計電路。

同時還要考慮抗混疊濾波器。

設計完的電路,拿不準的時候,可以用仿真來驗證。

-

時鐘抖動

+關注

關注

1文章

63瀏覽量

16130 -

SNR

+關注

關注

3文章

197瀏覽量

24838 -

ADC采樣

+關注

關注

0文章

134瀏覽量

13120 -

抗混疊濾波器

+關注

關注

1文章

10瀏覽量

10955

原文標題:用ADC之前,選它外圍電路的時候,需要考慮些什么

文章出處:【微信號:加油射頻工程師,微信公眾號:加油射頻工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

電源外圍保外圍應用電路

開發經驗!嵌入式硬件設計需要考慮的一些問題總結

【開發經驗】嵌入式硬件設計需要考慮的一些問題總結

請問設計穩壓電路的時候要考慮哪些因素?

一文教你如何進行ADC的外圍電路設計!

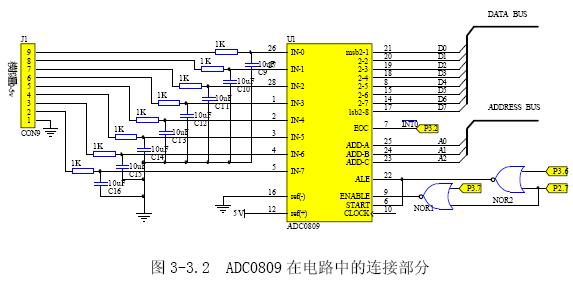

adc0809外圍電路

選ADC做外圍電路的時候,需要考慮些什么?

選ADC做外圍電路的時候,需要考慮些什么?

評論