引言:上一篇介紹了BGA封裝PCB層數估計、BGA焊盤設計、過孔設計、信號走線等內容,本文我們介紹下FPGA BGA封裝電源管腳布線。

1. 概述

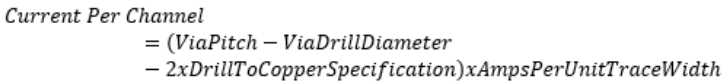

工程師必須在設計階段早期評估功率需求,以確保有足夠的層和面積為需要功率的BGA焊盤提供足夠的功率。因為大多數BGA電源引腳位于BGA區域的中心,所以電流行進的路徑穿過BGA區域中的無數過孔。過孔之間的空間可以保守地承載約0.05A/mil的走線寬度(對于0.5盎司的銅)。過孔之間的跡線寬度由過孔的節距(通常與BGA的節距相同)、過孔鉆頭直徑和制造廠定義的鉆銅規格來定義。下圖顯示了如何計算可以通過每個通路的電流量。確保電源平面足夠寬,足夠包容,以便為BGA電源球提供所需的安培數。以下方程可用于計算每個通道的電流:

圖1:BGA區域內的電力輸送(0.5盎司銅)

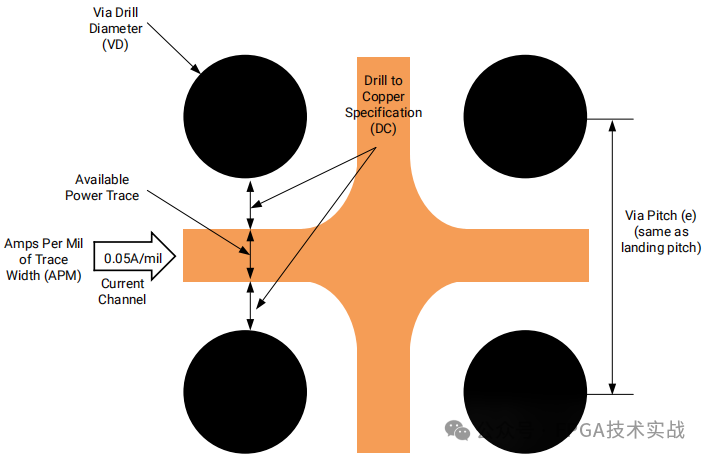

下表顯示了0.8 mm和1.0 mm間距器件的每個通道的電流值。由于0.5mm器件的間距非常細,因此不可能在標準過孔之間布線。為了到達電源平面,對于0.5mm焊盤器件建議通過BGA焊盤下的微過孔實現與電源層互聯。

表1:0.8 mm、0.92 mm和1.0 mm器件的每通道電流計算

2. 用于遠距離電壓感測線(Sense Lines)的PCB布線

為了正確補償由于高電流負載引起的PCB上的IR電壓降,電壓調節器模塊(VRM)感測線的正確布線對于在ACAP管芯處保持適當的電壓電平至關重要。

注意:由于調節器的設計、引腳和要求各不相同,請務必始終遵循VRM供應商的感應線建議。

2.1 感應線的用途

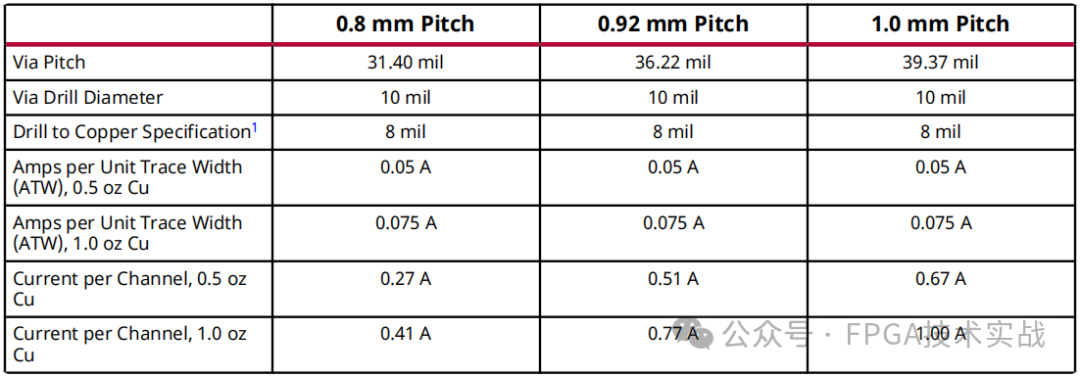

由于電壓調節器通常與它們供電的設備相距很遠,因此在調節器和負載的主要點之間的電壓通常存在DC電壓IR下降,特別是在存在高電流負載的情況下。如果調節器沒有考慮到這種下降,負載點的電壓可能比調節器看到的要低很多。由此產生的較低電壓可能超出正確器件操作所需的極限。下圖說明了電流的方向和由此產生的電壓降。

圖2:VRM和負載點之間的直流電壓降

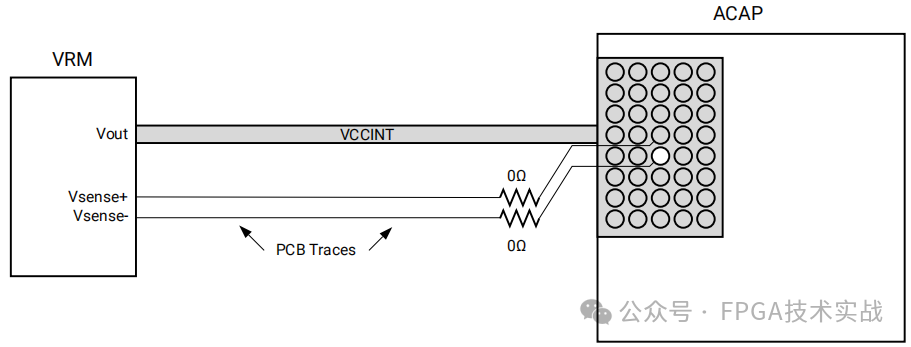

為了克服這種電壓降,調節器實現了從調節器直接連接到負載點的感測線。這些感測線是調節器和負載點之間的直接跡線,不攜帶任何電流。因為它們不攜帶任何電流,所以調節器感測引腳處的電壓與負載點處的電壓完全相同。因此,調節器可以根據需要適當地調節其輸出電壓,使得負載點處的電壓在所需的規格內。下圖說明了從VRM到負載點的感測線的放置和布線。

圖3:感應線示例

2.2 感應線的局限性

1)電壓差

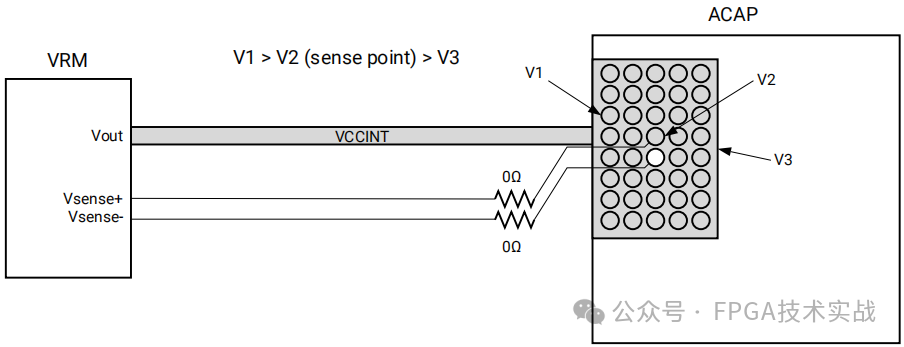

因為感測線只能放置在負載點的一個位置,所以感測點前面的其他區域可能顯示出更高的電壓,而負載點之外的點可能顯示出更低的電壓。下圖說明了這種電壓差異。當電流從VRM流到負載點時,點V1處的電壓高于V2處的感測點。同樣地,點V3處的電壓低于感測點V2處的電壓。

圖4:BGA引腳中不同點的電壓 2)只有一個感測引腳的VRM

某些VRM不包括用于接地的感測引腳。這種布置的主要限制是VRM不考慮負載點處接地電壓的波動,導致電壓調節不太精確。

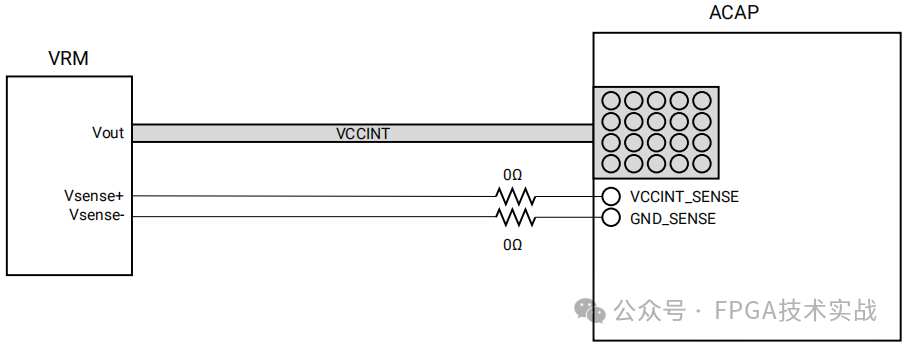

2.3 帶專用檢測引腳的ACAP

Select Versal ACAP包含用于VCCINT及其相關接地回路的專用遠程電壓感測引腳。它們提供了對模具最接近的觀察。下圖顯示了具有專用感測引腳的ACAP的推薦感測線路布線。

?在ACAP附近放置內聯0Ω電阻器:

○ 需要電阻器來確保感測線被布線為跡線,并且不會掉到平面上。

?將感應線路布線為50Ω松耦合差動傳輸線路:

○ 需要接地才能感應到電源和接地之間的真正差異。

圖5:專用感測引腳布線

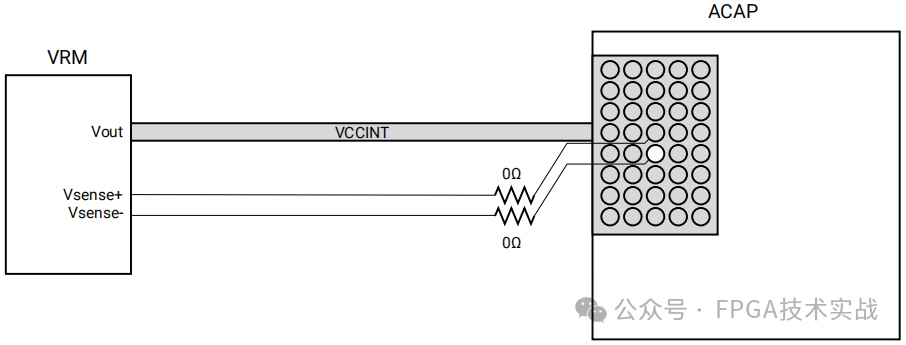

2.4 無專用檢測引腳的ACAPS

對于沒有專用感測引腳的ACAP,感測線連接應連接到盡可能靠近ACAP上最重要負載點的BGA球。這可以通過直流模擬或Vivado工具中的設備視圖進行最佳估計。如果無法估計負載點,建議將感測連接朝向BGA引腳場的中心。將球放置在離調節器最遠的位置也是一種選擇,但不太可取。

?在ACAP附近放置內聯0Ω電阻器:

○ 需要電阻器來確保感測線被布線為跡線,并且不會掉到平面上。

?將感應線路布線為50Ω松耦合差動傳輸線路:

○ 需要接地才能感應到電源和接地之間的真正差異。

為了實現最佳的功率傳輸,確保連接到感測線的球完全連接到它們各自的平面,即,不要將它們作為“間諜孔”未連接(見下圖)。

圖6:沒有專用感測引腳的布線

圖6:沒有專用感測引腳的布線

2.5 路由隧道和感測線的使用

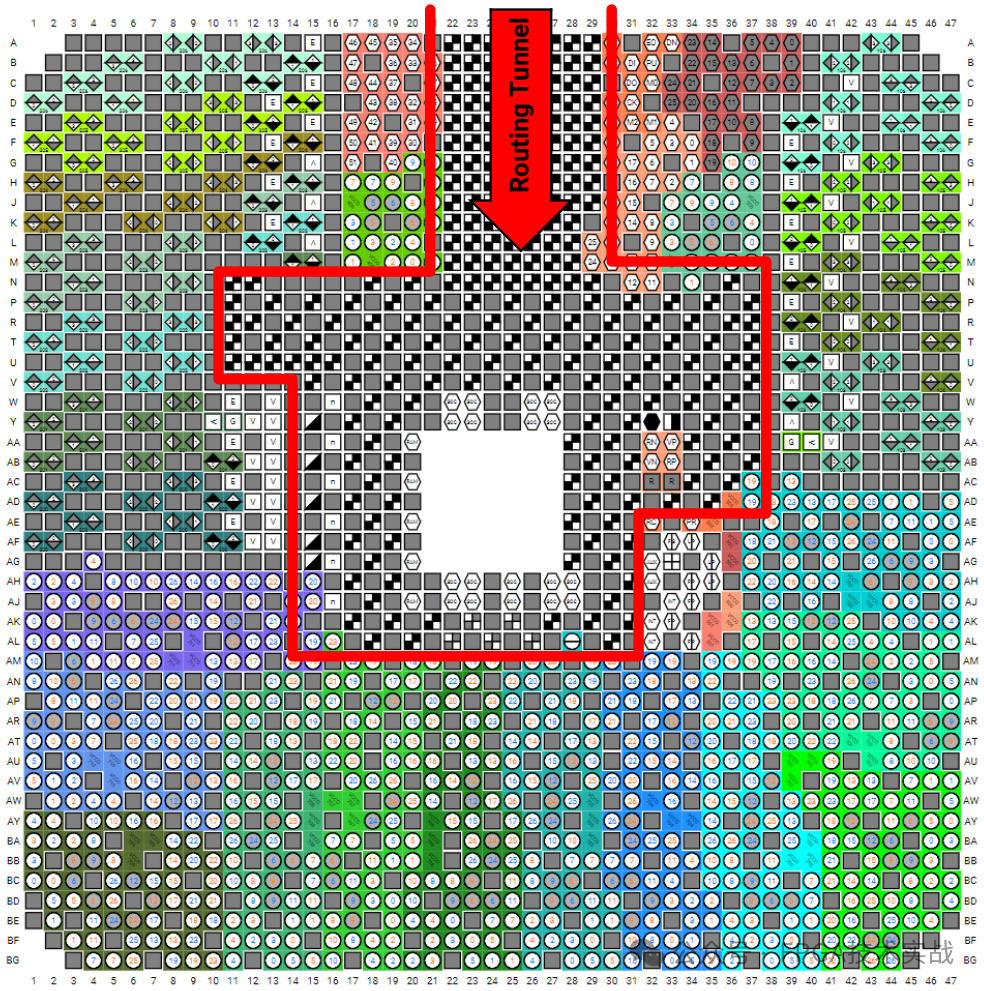

一些Versal ACAP具有專門放置的BGA引腳的專用“隧道”(Tunnel),以便以最小的IR壓降提供最大的功率傳輸。這種所謂的路由隧道消除了導致電源平面出現孔洞的過孔阻擋區域。布線通道中的引腳不會直接連接到ACAP上的管芯。這些引腳的存在只是為了使VCCINT的PCB布線平面不需要來自其他信號或電源軌的過孔。

下圖顯示了帶有VCCINT引腳字段的VC1902-A2197器件的BGA引腳區域。布線隧道區域中的引腳不需要到下面的VCCINT平面的過孔,因此在向VCCINT供電的金屬平面中沒有孔。最佳感測線放置在VCCINT引腳場上路由隧道外部的任何點上。

圖7:帶VCCINT路由隧道的VC1902-A2197

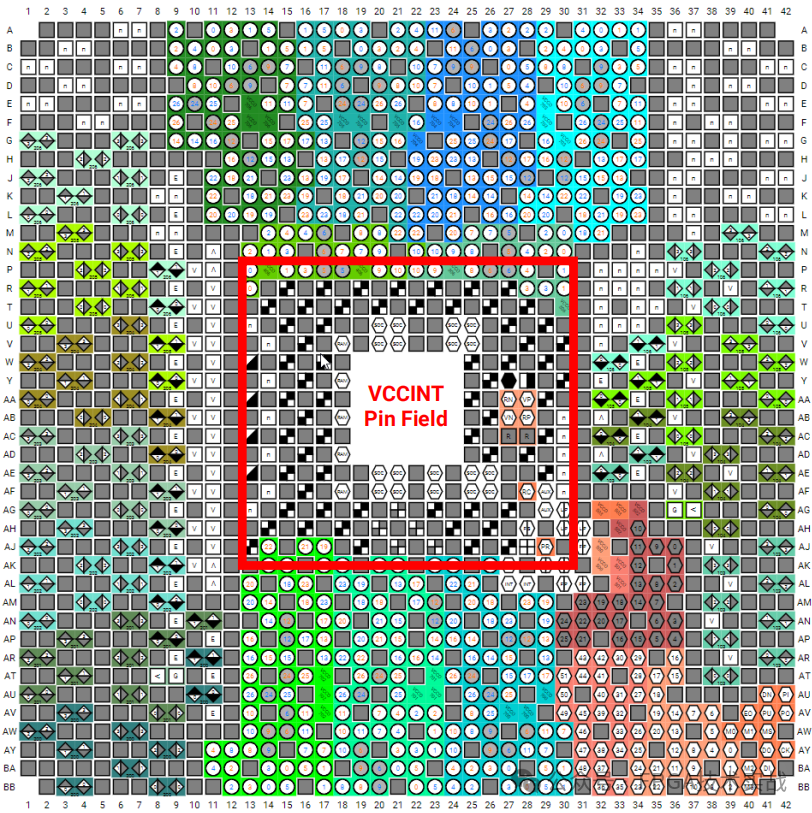

下圖顯示了帶有VCCINT引腳字段的VM1802-C1760器件的BGA引腳字段。該設備上沒有路由隧道,因此BGA上的功率平面具有過孔擋板,從而降低了功率傳輸效率。建議在該引腳場中心附近的任何位置放置感測線。

圖8:VM1802-C1760 VCCINT引腳區域

-

FPGA

+關注

關注

1643文章

21954瀏覽量

613943 -

BGA

+關注

關注

5文章

565瀏覽量

48134 -

VRM

+關注

關注

0文章

31瀏覽量

12857 -

電壓調節器

+關注

關注

3文章

154瀏覽量

18258 -

負載電壓

+關注

關注

0文章

50瀏覽量

2961

原文標題:Xilinx FPGA BGA推薦設計規則和策略(二)

文章出處:【微信號:FPGA技術實戰,微信公眾號:FPGA技術實戰】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

Xilinx BGA設備的推薦設計規則和策略的用戶指南免費下載

Xilinx 7系列FPGA介紹

Xilinx FPGA BGA設計:NSMD和SMD焊盤的區別

Xilinx FPGA BGA推薦設計規則和策略(二)

Xilinx FPGA BGA推薦設計規則和策略(二)

評論