芯片是科技發(fā)展的核心關鍵和技術底座。當下RISC-V、Chiplet、AI、汽車電子等成為該行業(yè)的高頻詞。這兩年的半導體行業(yè),皆圍繞著這幾個技術應用快速發(fā)展,也間接地加劇了對EDA(電子設計自動化)工具的需求。面對這些技術進步和市場需求變化,在芯片新戰(zhàn)場上,堪稱“芯片之母”的EDA又該如何擁抱這些新挑戰(zhàn)?

芯片新戰(zhàn)場,挑戰(zhàn)重重

說起來RISC-V和Chiplet早已存在一段時間了,只是最近幾年才變得火熱。

RISC-V架構確實具備眾多優(yōu)勢,如免費開源、簡潔的指令集(基礎指令集只有40多條),高度模塊化的設計能力,以及允許針對不同類型的芯片進行指令集的組合……但也正因為如此,一定程度上也阻礙了其發(fā)展。由于所有廠商都可以自由使用、修改或增加指令集,因此每家廠商設計的芯片可能都不相同。這不僅增加了設計的復雜性,也使得驗證變得更加困難。為應對這些挑戰(zhàn),EDA工具需要提供更高級的建模、模擬和驗證功能,特別是在確保定制化的RISC-V核心滿足設計規(guī)范、性能要求以及處理器性能、功耗和安全性方面的嚴格驗證。

Chiplet技術,作為當前芯片設計領域的新風口,同樣給EDA行業(yè)帶來了一系列挑戰(zhàn)。這種技術是使用小型模塊化的“Chiplet”來組成更大、更復雜的系統(tǒng)級芯片(SoC)。同時也代表著異構集成的芯片技術。在摩爾定律放緩的背景下,許多業(yè)界專家視其為中國半導體企業(yè)的新機遇。然而,清華大學教授魏少軍指出,Chiplet技術更多是作為先進制造工藝的補充,而非替代品,其核心在于實現(xiàn)成本可控的異質集成。這項技術主要應用于計算邏輯與DRAM集成、手機領域以節(jié)省空間,以及汽車、工業(yè)控制和物聯(lián)網等領域。

魏少軍還提到,Chiplet技術的出現(xiàn)可能促成一種新的商業(yè)模式:利用標準化的芯粒構建專用芯片。這是為什么一些國際大公司正在努力制定Chiplet標準的原因,通過這些標準,他們可以將自己的芯片作為標準產品,集成到各種終端應用中,從而擴大市場份額。

這種技術所帶來的新挑戰(zhàn),如異構集成系統(tǒng)中接口和標準的統(tǒng)一性,要求工程師在異質芯片的性能和靈活性之間尋找平衡。同時,這也意味著需要新的EDA工具鏈、上下游生態(tài)系統(tǒng)的整合,以及適應新的商業(yè)模式。

此外,隨著Sora的發(fā)布,AI的熱潮再度掀起。而算力,是AI時代最確定的賽道。Open AI的創(chuàng)始人奧特曼在達沃斯論壇上表示:“對大規(guī)模AI準備的算力基礎設施還不夠。”大算力芯片需要處理大量的數(shù)據(jù)和復雜的運算,這要求EDA必須支持高級的設計和仿真功能。工具必須能夠有效處理高性能計算需求,同時保證設計的準確性和可靠性。

RISC-V是架構,Chiplet、AI是技術,這些都不是獨立發(fā)展的,最終需要落地到產品上。就比如汽車是以上這些最重要的一個應用終端,落地靠的是各種汽車電子。其中,RISC-V 可以為 AI 應用提供定制化的處理器平臺,也允許汽車制造商和供應商設計滿足特定需求的處理器,例如優(yōu)化能效或計算性能。同時,通過組合不同的 Chiplet來達到所需的性能和功能。而AI 算法可以在這些專門設計的處理器上運行,以處理汽車傳感器數(shù)據(jù)、做出決策和提供先進的駕駛輔助功能。這就很考驗如今的EDA,不僅僅支持單一芯片的設計,還要能夠支持更廣泛的系統(tǒng)級設計。這意味著需要能夠處理來自不同來源和技術的芯片和組件的集成。

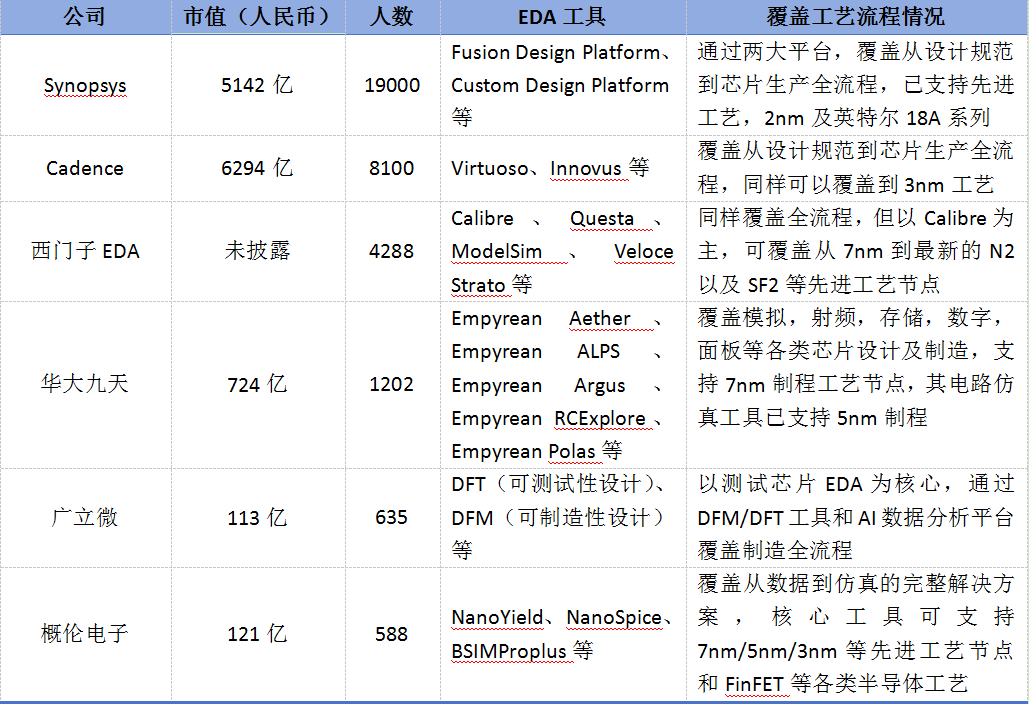

在這個充滿新技術和應用挑戰(zhàn)的時代,我們面對包括系統(tǒng)級設計支持、高級建模/模擬和驗證功能、系統(tǒng)規(guī)范性測試、統(tǒng)一開發(fā)環(huán)境,以及處理大量數(shù)據(jù)和復雜運算的能力等等在內的眾多技術挑戰(zhàn)。鑒于這些技術日新月異,EDA如何通過創(chuàng)新理念、工具、設計方法和策略來適應這些變化?又如何確保芯片設計正確,以及確保設計正確芯片?這里的“正確”不僅在于芯片功能方面,更在于設計出真正需要的、有市場價值的芯片。EDA公司的精準芯策略

目前,針對上述挑戰(zhàn)很多頭部EDA公司正處在探索、嘗試和發(fā)展的階段。以國內的思爾芯為例,該公司正積極在新應用和新技術領域進行布局,如RISC-V、Chiplet、AI、GPU、高性能計算(HPC)和汽車電子等,并給出了針對性的解決方案。

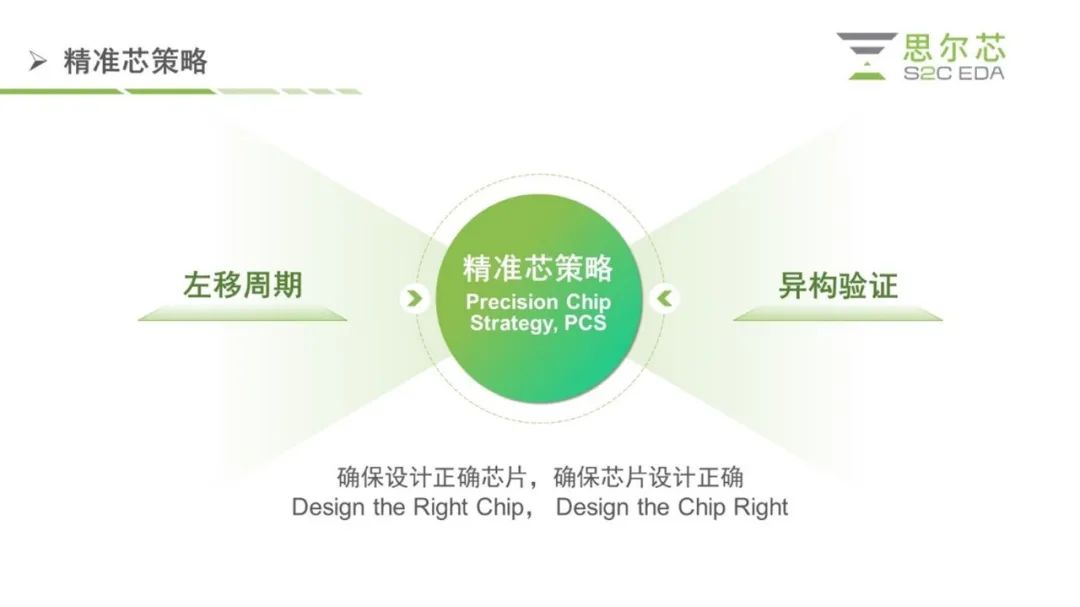

思爾芯的創(chuàng)始人、董事長兼CEO林俊雄指出:“面對芯片設計的新挑戰(zhàn),我們圍繞‘精準芯策略’(Precision Chip Strategy, PCS),采用異構驗證方法,以及并行驅動和左移周期方法,旨在確保芯片設計正確(Design the Chip Right),也確保設計正確芯片(Design the Right Chip)。”

林俊雄所提到的“確保芯片設計正確”和“確保設計正確芯片”這兩個概念,雖然聽起來相似,但實際上涵蓋了芯片設計過程中的兩個非常重要且不同的方面。

確保芯片設計正確-關注的是在實現(xiàn)設計中,如何以最高效、最準確的方式來驗證這個設計。這包括通過合適的設計方法學,在不同的設計階段選用高效的工具,進行徹底的仿真和驗證。這一過程強調的是“正確地做事”,即在技術和操作層面上精確無誤地實現(xiàn)設計目標。

確保設計正確芯片-關注的是確保設計團隊設計出符合市場需求和應用場景需求的芯片。這涉及對市場趨勢的理解、對未來技術發(fā)展的預測以及對客戶需求的深刻洞察。面對多變的市場,要有新的設計方法與工具去高效且精準地實現(xiàn)。這一過程強調的是“做正確的事”,即設計出真正需要的、有市場價值的芯片。 芯片設計一直以來都在強調設計的準確性,一旦芯片流片失敗,不僅導致高額的成本損失,還可能使企業(yè)錯過重要的市場窗口。這一點無論是過去還是技術日新月異的現(xiàn)在,都依然如此。這就是為什么EDA廠商始終推進和改進設計方法,以確保芯片設計的正確。觀察整個芯片開發(fā)流程中,每個階段的設計和驗證需求是各不相同的。為了確保每一步都設計準確,就需要充分的仿真。但是傳統(tǒng)的軟件仿真方法一旦遇到設計規(guī)模變大,性能就會大大降低。為此,思爾芯通過異構驗證方法,融合了多種先進仿真與驗證技術,針對不同階段采用相應的設計與驗證策略。

芯片設計一直以來都在強調設計的準確性,一旦芯片流片失敗,不僅導致高額的成本損失,還可能使企業(yè)錯過重要的市場窗口。這一點無論是過去還是技術日新月異的現(xiàn)在,都依然如此。這就是為什么EDA廠商始終推進和改進設計方法,以確保芯片設計的正確。觀察整個芯片開發(fā)流程中,每個階段的設計和驗證需求是各不相同的。為了確保每一步都設計準確,就需要充分的仿真。但是傳統(tǒng)的軟件仿真方法一旦遇到設計規(guī)模變大,性能就會大大降低。為此,思爾芯通過異構驗證方法,融合了多種先進仿真與驗證技術,針對不同階段采用相應的設計與驗證策略。

思爾芯異構驗證方法包括架構設計(芯神匠)、軟件仿真(芯神馳)、硬件仿真(芯神鼎)和原型驗證(芯神瞳),覆蓋了從IP開發(fā)到系統(tǒng)驗證的全過程。此外,通過利用數(shù)字電路調試軟件(芯神覺)以及豐富的外置應用庫/降速橋/VIP,思爾芯構建了一個全面的設計、驗證和調試環(huán)境。這個環(huán)境不僅促進了跨團隊的高效協(xié)作,也確保了設計的每個環(huán)節(jié)都能達到預定的準確性,從而在短的時間內高效實現(xiàn)了“確保芯片設計正確”的目標。

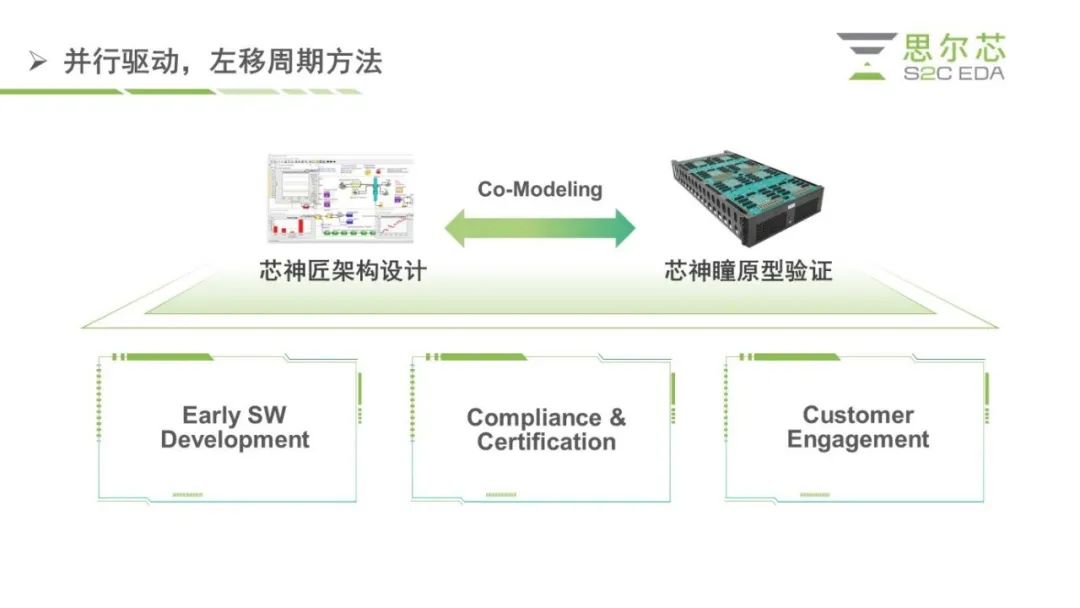

其次,在傳統(tǒng)的工作流程中,軟件開發(fā)、系統(tǒng)規(guī)范性測試、各類認證、客戶演示等都要在流片回來上板后才能進行。這是一個漫長的等待過程,由于現(xiàn)在的技術日新月異,很多設計是到樣片上板測試后才發(fā)現(xiàn)早期的規(guī)格或架構錯誤,或是并不符合市場需求。此時,如何確保設計正確芯片?現(xiàn)在思爾芯通過并行驅動,左移周期方法,在芯片設計的初始階段,就實現(xiàn)并行驅動的工作流程。這意味著在設計的一開始,并在每一個階段,利用工具高效且準確進行設計。

先是使用思爾芯的芯神匠架構設計軟件(Genesis Architect),設計團隊可以在設計的早期階段進行有效的規(guī)劃和架構設計。這不僅提高了設計的精準性,也加快了后續(xù)的開發(fā)流程。之后,工程師可以通過芯神瞳原型驗證(Prodigy)與芯神匠架構軟件(Genesis Architect)的協(xié)同建模,將RTL代碼映射進原型驗證中,使得設計模型和最終芯片相一致。透過架構設計與原型驗證的模型,它的運行速度可接近最終芯片,因此可以進行提前軟件開發(fā),客戶演示等,亦可提早進行各種認證,例如汽車電子的安全性認證等。這種方法大大縮短了開發(fā)時間,同時實現(xiàn)了設計和驗證過程的時間提前,即“左移”,從而又快又好地實現(xiàn)“確保設計正確芯片”的目標。  通過這些設計方法和工具,思爾芯不僅加速了新興趨勢下復雜芯片的設計過程,還確保設計正確芯片,確保芯片設計正確,幫助客戶在競爭激烈的芯片市場中獲得優(yōu)勢。

通過這些設計方法和工具,思爾芯不僅加速了新興趨勢下復雜芯片的設計過程,還確保設計正確芯片,確保芯片設計正確,幫助客戶在競爭激烈的芯片市場中獲得優(yōu)勢。

林俊雄還強調,思爾芯率先在產品中使用了AI技術,小到從分割(partitioning)算法的資源預估,大到架構層級優(yōu)化(architecture-level optimization)工具的設計空間探索,都有很重要的AI應用。

思爾芯是國內數(shù)字前端EDA領域的行業(yè)龍頭,也是業(yè)內最早開發(fā)原型驗證工具的企業(yè)。在思爾芯20周年的閉門論壇上,林俊雄介紹:“2004年在上海成立至今,這20年間,我們一直專注于客戶,貼近客戶并始終堅持以客戶需求為導向的原則。讓客戶能夠站在雙方幾十年的知識積累和客戶經驗上,客戶可以在很短時間內完成一個貼近自己具體應用需求的SoC重建,降低風險并加速軟件開發(fā)進程,提前實現(xiàn)系統(tǒng)的整合。”

截至目前,思爾芯的客戶數(shù)量已超過600家,包括英特爾、三星、索尼、黑芝麻、開芯院、芯動科技等。其產品已廣泛應用于物聯(lián)網、云計算、5G 通信、智慧醫(yī)療、汽車電子等終端領域。寫在最后

在當今這個以RISC-V、Chiplet、AI和汽車電子為代表的新技術時代中,如何確保設計正確芯片以及確保芯片設計正確成為了各界的核心關注點。盡管芯片設計的正確性極為關鍵,但同時幫助芯片公司符合市場需求并把握市場窗口同樣重要。這正突顯了思爾芯“精準芯策略”在該方面的重要性。

在這個充滿挑戰(zhàn)的芯片設計新戰(zhàn)場上, EDA的角色不僅僅是適應新興技術的發(fā)展,更重要的是積極地擁抱和引領這些挑戰(zhàn)。為了應對不斷變化的市場和技術需求,EDA工具必須持續(xù)進行創(chuàng)新和演進,以滿足越來越復雜的設計要求。

在這方面,思爾芯憑借其20年的技術積累和完善的數(shù)字前端EDA解決方案,已經展現(xiàn)出了其卓越的能力。通過實施“精準芯策略”、提供本地化支持和定制服務,思爾芯不僅加速了客戶產品的上市時間,還成功開辟了新的市場空間。這一切,都是思爾芯對于不斷變化的技術和市場環(huán)境的積極響應和前瞻性布局的結果。

轉載自:半導體行業(yè)觀察公眾號

-

芯片

+關注

關注

460文章

52616瀏覽量

442568 -

eda

+關注

關注

71文章

2942瀏覽量

178546 -

RISC-V

+關注

關注

46文章

2608瀏覽量

49027

發(fā)布評論請先 登錄

EDA禁令即將來襲!中國芯片產業(yè)迎背水一戰(zhàn)

華大九天物理驗證EDA工具Empyrean Argus助力芯片設計

EDA是什么,有哪些方面

用一套Linux系統(tǒng),撐起整個芯片設計平臺?CFA團隊教你如何搭好EDA智算平臺的技術底座

西門子EDA工具如何助力行業(yè)克服技術挑戰(zhàn)

EDA2俠客島難題挑戰(zhàn)·2025已正式開啟

新思科技引領EDA產業(yè)革新,展望2025年芯片與系統(tǒng)創(chuàng)新之路

芯華章持續(xù)助力EDA精英挑戰(zhàn)賽

EDA精英挑戰(zhàn)賽賽果公布!思爾芯“戰(zhàn)隊”薪火相承斬獲“麒麟杯”

AI助力國產EDA,挑戰(zhàn)與機遇并存

SOC芯片設計的挑戰(zhàn)與解決方案

AI如何助力EDA應對挑戰(zhàn)

西門子EDA全面賦能芯片創(chuàng)新

新思科技探索AI+EDA的更多可能性

思爾芯賽題正式發(fā)布,邀你共戰(zhàn)EDA精英挑戰(zhàn)賽!

芯片新戰(zhàn)場,EDA如何擁抱新挑戰(zhàn)?

芯片新戰(zhàn)場,EDA如何擁抱新挑戰(zhàn)?

評論