制造過程連接著設計師和大規模生產 PCB 的公司。設計者必須了解,該過程涉及相關成本,這意味著工作時間和工程材料的表面積都需要優化。拼版是一種用于同時大規模生產多塊電路板的技術,這些電路板放置在一個陣列中,以加快裝配進度。

在整個 PCB 設計結束后,電路板需要在 SMT 貼片流水線上安裝元器件。每個 SMT 加工工廠會根據流水線的加工要求,對電路板的合適尺寸做出規定。如果電路板尺寸過小或過大,流水線上固定電路板的工裝將無法固定。那么,如果電路板本身尺寸小于工廠規定的尺寸怎么辦?這就需要對電路板進行拼板,將多個電路板拼成一整塊。拼板對于高速貼片機和波峰焊都能顯著提高效率。拼板主要是為了主要是減少材料的浪費,提高生產效率。

Cadence從SPB17.4版本開始,將Fab Panelization Tool作為PCB Editor的基本功能,讓設計師們,在完成了單板設計后,很方便地在Allegro PCB Editor環境中,快速實現單板的拼版設計,以優化制造過程。Cadence的Allegro PCB Editor中的Fab Panelization Tool是一個簡化拼版文檔處理的應用程序。

1

Fab Panelization Tool拼版功能涵蓋:

?拼版僅在布局的基礎上設置,不需要原理圖。

?實際的Board數據鏈接到拼版數據進行自動更新。

?也支持混合拼版,這意味著可以將不同的電路板數據引入到同一個拼版數據中。

?Board可以單獨放置,也可以通過指定陣列來放置。

?每塊Board都可以在拼版數據中進行單獨旋轉和/或鏡像。

?更新過程是完全自動化的。

?如果需要更新,包括自動和手動通知(Board已修改)

?使用來自PCB Editor的經過驗證的mdd技術(設計重用,Replicate放置)。

為了讓設計師盡快掌握Fab Panelization Tool工具的使用,本文將介紹如何使用AllegroPCB Editor 進行拼版設計。

01

創建brd數據

進行拼版設計,必須創建一個新的brd數據。在新的brd數據中,必須添加Design_Outline、Outline、Route_Keepin、Package_Keepin等信息,添加標記、切割標記等機械信息來準備新的brd數據。由于PCB板制造商使用不同的尺寸,建議將拼版數據定義為Mechanical Symbol形式以供重復使用。

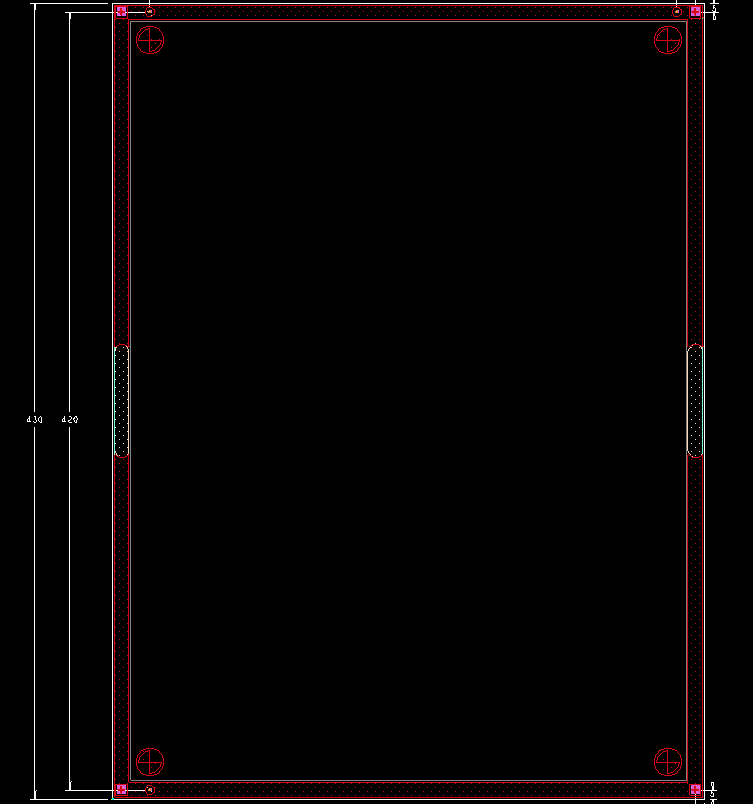

啟動PCB Editor工具,打開pcb_context目錄下的panel_start.brd文件,如圖所示:

02

Fab Panelization Tool

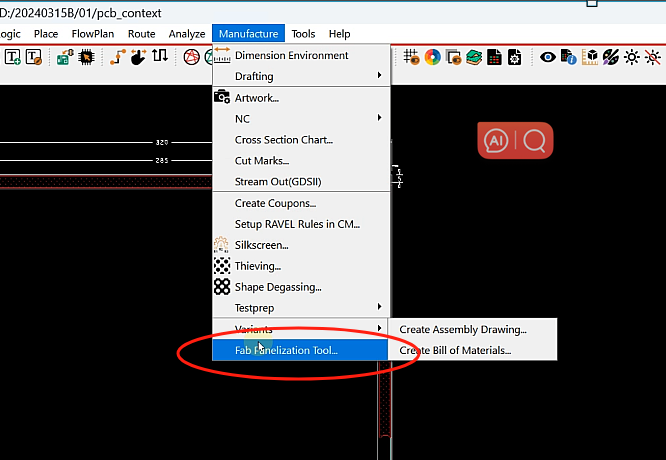

在PCB Editor中,選擇Manufacture下拉菜單選擇Fab Panelization Tool,如圖所示:

03

03

設置數據

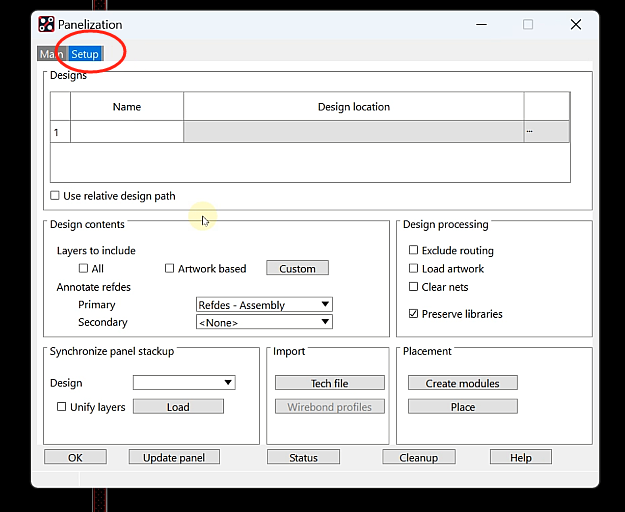

當進入Panelization界面后,選擇Setup選項卡,如圖所示:

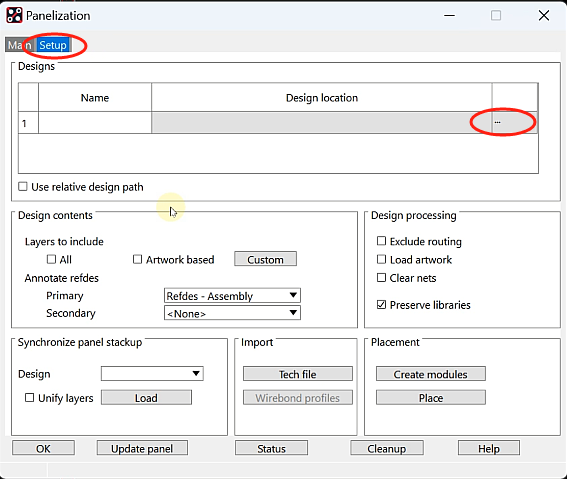

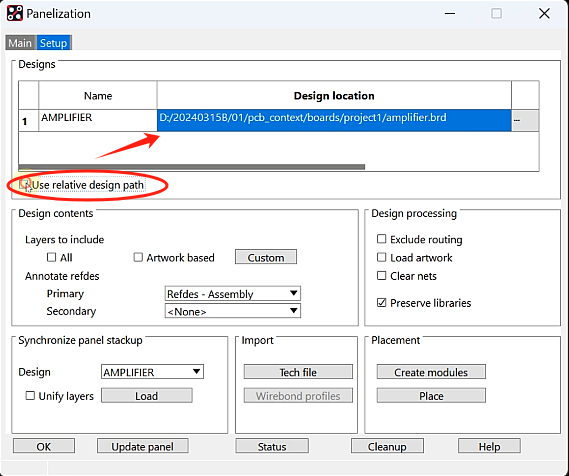

1)在Designs區域里,第一行中點擊Browse字段,會出現一個文件瀏覽器,導航到您想要定義拼版的brd數據。選擇pcb_context/boards/project1/amplifier.brd文件,如圖所示:

在這一步,如果勾選了Use relative design path,Designlocation將顯示為brd數據的相對路徑,如圖所示:

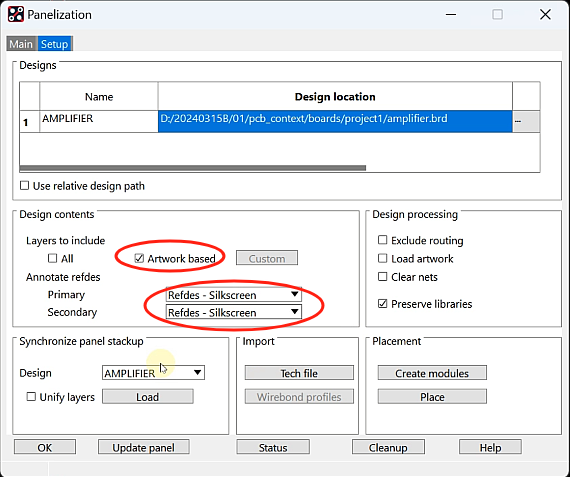

2)在拼版設計過程中,希望生成拼版的裝配圖,包括原始(非前綴)Refdes,拼版中的每一塊子板保持原始的Refdes維持不變。因此,需要在Design ontents中,勾選Artwork based,確保系統自動將原始brd中的Refdes-Silkscreen層的信息,分別復制到系統新建的Package Geometry-Pnl_Refdes層中,設置如圖所示:

04

04

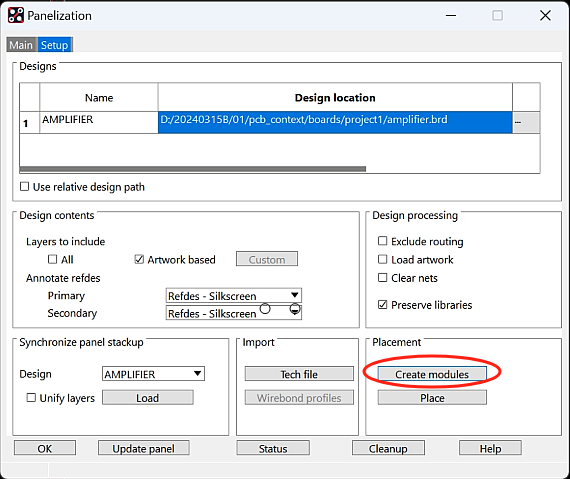

創建模塊(Module)

點擊Create Modules,按下此按鈕,PCB Editor將打開Designs欄中指定的brd板,并為其創建一個模塊。此外,將提取交互式放置所需的尺寸信息和實際輪廓數據。如圖所示:

05

放置模塊

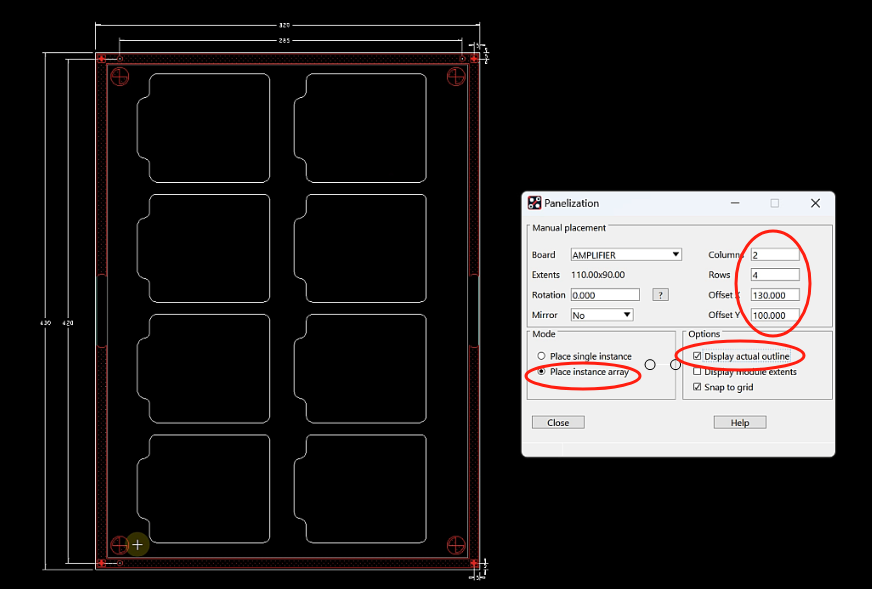

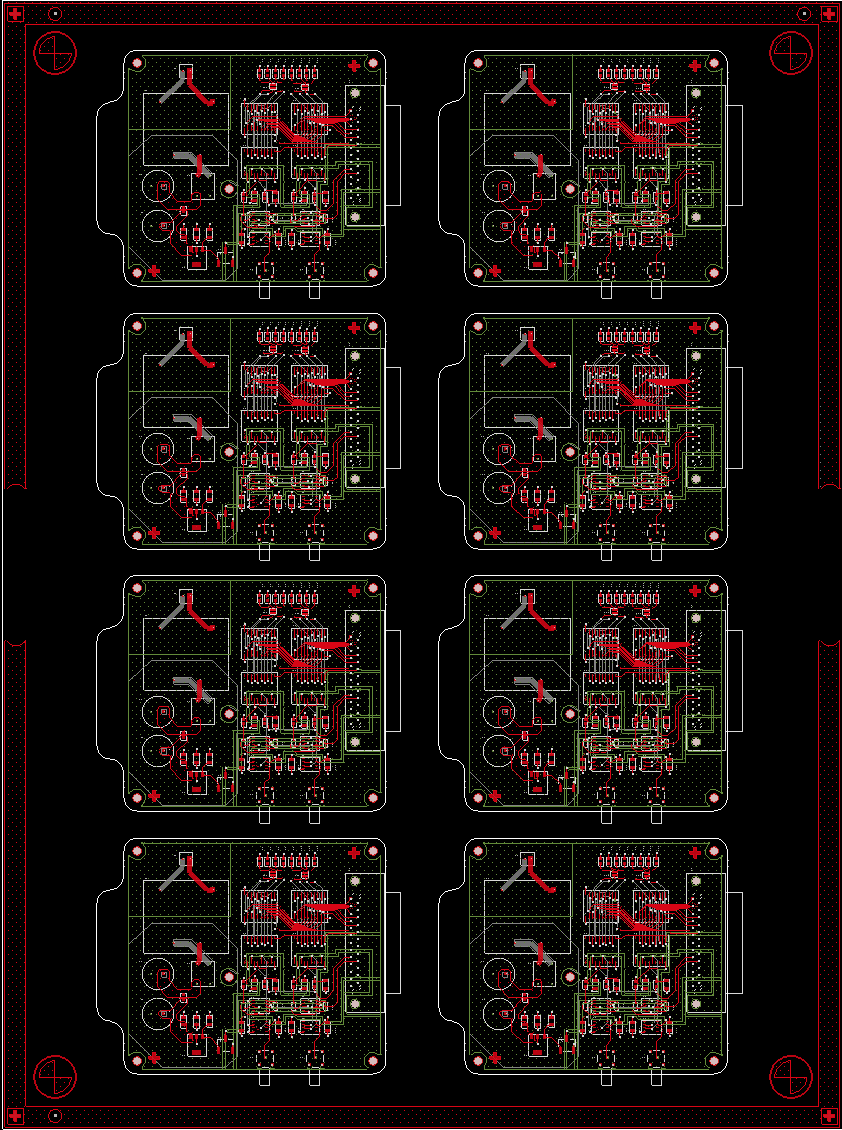

點擊Place,系統將彈出Panelization放置界面,在Manual placement區域,設置Columns為2、Rows為4、Offset X為130、Offset Y為100;在Mode區域,選擇Place instance array;Options區域,勾選Display actual outline,系統將以實際PCB板的Outline為PCB板邊框顯示輪廓,如圖所示:

一旦您在拼版數據中指定了位置,板子將顯示為模塊實體。

-

pcb

+關注

關注

4349文章

23400瀏覽量

406373 -

smt

+關注

關注

42文章

3014瀏覽量

71215 -

allegro

+關注

關注

42文章

697瀏覽量

146876

發布評論請先 登錄

Allegro Skill布局功能之快速切換格點介紹

安森美終止收購Allegro 此前安森美為什么要收購Allegro MicroSystems?

PCB拼版設計技巧

PCB拼板必備技巧:如何避免生產中的常見問題?

Allegro與TenXer Labs達成合作

建議DFM工具里的拼版在完善一下

Cadence官方出品CadencePCBViewers

技術資訊 I 如何使用 Allegro X PCB Editor 優化RF布線和阻抗

Cadence Allegro 17.4PCB阻抗分析功能操作說

原來手機SIM卡的PCB設計是這樣的!

Cadence快板PCB培訓

Allegro X 23.11 版本更新 I PCB 設計:DFA_BOUND 用于 DFA 規則設定

Allegro PCB Editor實現單板拼版設計

Allegro PCB Editor實現單板拼版設計

評論