FPGA 是一種以數(shù)字電路為主的集成芯片,于 1985 年由 Xilinx 創(chuàng)始人之一 Ross Freeman 發(fā)明,屬于可編程邏輯器件(Programmable Logic Device,PLD)的一種。

FPGA 比 CPLD 早幾年問世,與 CPLD 并稱為高密度可編程邏輯器件,但它們有著本質(zhì)的區(qū)別。FPGA 芯片的內(nèi)部架構并沒有沿用類似 PLA 的結構,而是采用了邏輯單元陣列(Logic Cell Array,LCA)這樣一個概念,改變了以往 PLD 器件大量使用與門、非門的思想,主要使用查找表和寄存器。

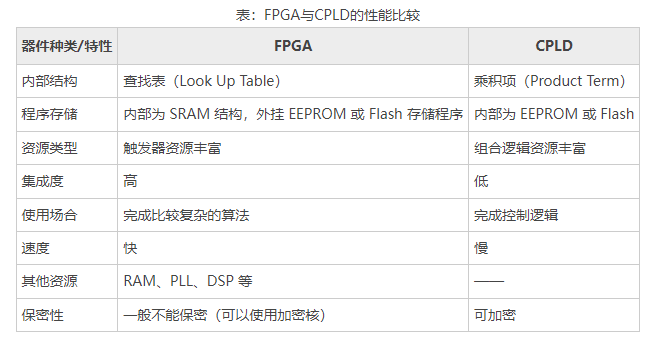

除此之外,F(xiàn)PGA 和 CPLD 在資源類型、速度等方面也存在差異,如下表所示。

FPGA 的類型從內(nèi)部實現(xiàn)機理來講,可以分為基于 SRAM 技術、基于反熔絲技術、基于 EEPROM/Flash 技術。就電路結構來講,F(xiàn)PGA 可編程是指三個方面的可編程:可編程邏輯塊、可編程 I/O、可編程布線資源。可編程邏輯塊是 FPGA 可編程的核心,我們上面提到的三種技術也是針對可編程邏輯塊的技術。

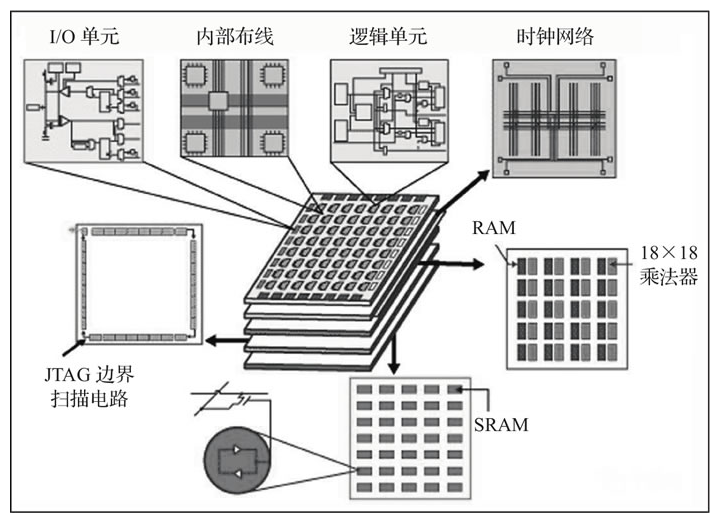

FPGA 的結構圖如圖 所示。

FPGA(Field-Programmable Gate Array,現(xiàn)場可編程門陣列)是一種可編程邏輯器件,具有靈活性和可重構性,通常用于數(shù)字電路設計和實現(xiàn)。FPGA的基本結構包括以下幾個主要部分:

1. 邏輯單元(Logic Blocks):邏輯單元是 FPGA 中的基本邏輯單元,用于實現(xiàn)各種邏輯功能。邏輯單元通常包括查找表(Look-Up Table,LUT)、寄存器、加法器等,可以根據(jù)需要配置不同的邏輯功能。

2. 可編程互聯(lián)網(wǎng)絡(Programmable Interconnect):可編程互聯(lián)網(wǎng)絡連接了邏輯單元之間的信號傳輸路徑。通過配置互聯(lián)網(wǎng)絡,可以實現(xiàn)邏輯單元之間的靈活連接,實現(xiàn)各種復雜邏輯功能。

3. 輸入/輸出模塊(IO Blocks):輸入/輸出模塊用于與外部系統(tǒng)進行通信,包括輸入輸出引腳、時鐘管理單元等。IO Blocks 提供了 FPGA 與外部系統(tǒng)進行數(shù)據(jù)交換的接口。

4. 時鐘管理單元(Clock Management):時鐘管理單元用于生成各種時鐘信號,并對時鐘信號進行分頻、延遲、對齊等操作,以確保設計的穩(wěn)定性和性能滿足要求。

5. 存儲單元(Memory Blocks):存儲單元包括片上存儲器等,用于存儲配置信息、中間結果數(shù)據(jù)和其他需要的存儲內(nèi)容,提供了額外的存儲資源。

6. 配置存儲器(Configuration Memory):配置存儲器用于存儲 FPGA 的配置位流(Configuration Bitstream),即描述 FPGA 邏輯功能和互聯(lián)的配置信息,通過加載配置位流實現(xiàn)對 FPGA 的編程和配置。

7. 全局時鐘網(wǎng)絡(Global Clock Network):全局時鐘網(wǎng)絡為 FPGA 提供整體的時鐘分配和管理功能,確保設計中的時序要求得到滿足。

fpga主要性能指標

FPGA 的性能指標主要包括以下幾個方面:

1. 邏輯容量(Logic Capacity):邏輯容量指的是 FPGA 中可用于實現(xiàn)邏輯功能的邏輯單元數(shù)量。它決定了 FPGA 可以實現(xiàn)的復雜度和規(guī)模,通常以邏輯單元數(shù)或等效門數(shù)(Equivalent Logic Cells)來衡量。

2. 時鐘頻率(Clock Frequency):時鐘頻率表示 FPGA 設備能夠支持的最高工作時鐘頻率,決定了 FPGA 設備在工作時能夠達到的最高速度。時鐘頻率通常以赫茲(Hz)為單位。

3. 資源利用率(Resource Utilization):資源利用率表示 FPGA 中邏輯單元、存儲單元等資源的使用情況,包括邏輯單元使用率、存儲塊利用率等,用于評估設計在 FPGA 中的資源占用情況。

4. 時序性能(Timing Performance):時序性能包括各種時序相關的指標,如最長組合邏輯延遲、時序收斂等,決定了 FPGA 設備能夠滿足的時序約束和穩(wěn)定工作的能力。

5. 功耗(Power Consumption):功耗是衡量 FPGA 設備能耗的重要指標,通常分為靜態(tài)功耗和動態(tài)功耗兩部分,影響 FPGA 在實際應用場景中的能耗和熱管理需求。

6. 輸入/輸出資源(IO Resources):輸入/輸出資源包括 FPGA 設備提供的輸入輸出引腳數(shù)目、支持的通信協(xié)議和標準、不同類型的輸入輸出模式等,影響 FPGA 在與外部系統(tǒng)、芯片或器件連接時的靈活性和適用性。

7. 可編程性(Programmability):可編程性指的是 FPGA 設備在配置、重配置和部署時的靈活性和便利性,包括配置速度、配置接口、支持的配置技術(如SRAM、FLASH等)等。

8. 硬核功能(Hard IP):硬核功能是 FPGA 芯片內(nèi)置的專用功能模塊,如硬核處理器、乘法器、DSP單元等,用于特定應用場景或性能需求,對于特定領域的應用具有重要意義。

審核編輯:黃飛

-

FPGA

+關注

關注

1645文章

22046瀏覽量

618294 -

cpld

+關注

關注

32文章

1257瀏覽量

171491 -

寄存器

+關注

關注

31文章

5434瀏覽量

124442 -

可編程邏輯器件

+關注

關注

5文章

145瀏覽量

30633 -

時鐘網(wǎng)絡

+關注

關注

0文章

16瀏覽量

6648

發(fā)布評論請先 登錄

altera fpga/cpld設計

FPGA 的結構圖及優(yōu)勢分析

FPGA和CPLD差異分析(FPGA結構圖)

FPGA和CPLD差異分析(FPGA結構圖)

評論