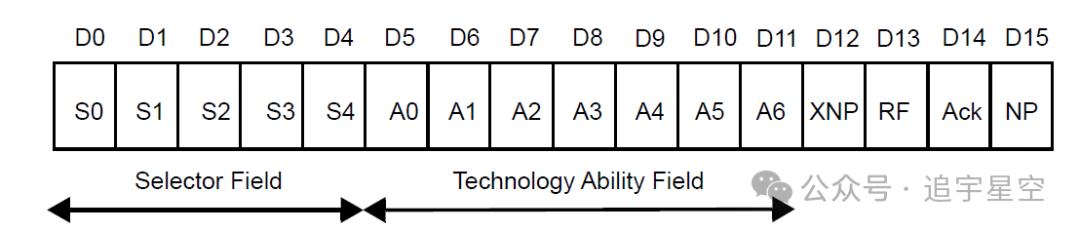

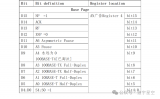

FLP Burst內容編碼—BasePage

BasePage的編碼格式如下圖:

?

?

在FLP突發中,D0應是傳輸的第一個比特。編碼釋義如下: Selector Field

[S4:S0]=2b00001(表示基于IEEE802.3以太網的自協商);

Technology Ability Field

[A0] 10BASE-T半雙工;

[A1] 10BASE-T全雙工;

[A2] 100BASE-TX半雙工;

[A3] 100BASE-TX全雙工;

[A4] 100BASE-T4半雙工;

[A5:A6]=2b00(表示無流控),

=2b01(表示指向對端的非對稱流控),

=2b10(表示對稱流控),

=2b11(表示對稱流控和指向本端的非對稱流控);

Extended Next Page

[XNP] =2b0 緊接BasePage的下一頁為NextPage,

=2b1 緊接BasePage的下一頁為ExtendedNextPage;

Remote Fault

[RF] =2b0 自協商無錯誤,

=2b1 自協商有錯誤;

[Ack] =2b0尚未收到來自遠端的BasePage,

=2b1 已收到來自遠端的BasePage;

Next Page

[NP] =2b0當前BasePage頁已是最后頁,

=2b1 當前BasePage頁不是最后頁;

BasePage的應用實踐

FLP Burst-BasePage交互應用于IEEE Clause 28雙絞線自協商的所有類型(10M/100M)、(10M/100M/1000M)和(10M/100M/1000M/2.5G/5G/ 10G/25G/40G)。而其中10M/100M自協商僅使用BasePage交互即可,10M/ 100M/1000M和10M/100M/1000M/2.G/5G/10G/25G/40G需要其他類型Page (NextPage和ExtendedNextPage)[在后續章節會陸續進行詳細介紹]。

筆者以曾經實踐過的Marvell公司的88e6097F Switch芯片中集成的百兆PHY舉例[與自協商相關的寄存器屬于IEEE802.3標準寄存器,故不同廠家不同型號的PHY該部分實現大同小異],與10M/100M自協商相關的3個寄存器內容分別如下:

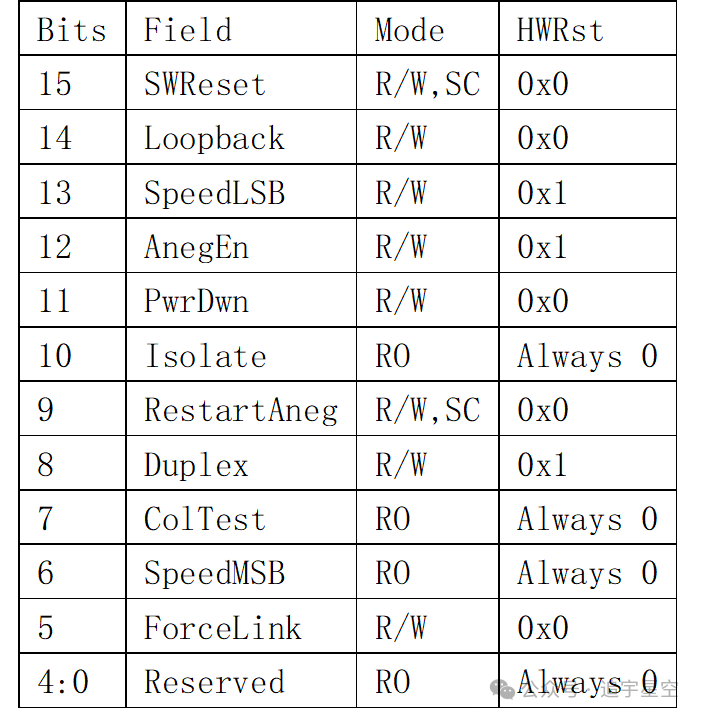

PHY Control Register Register 0

在該寄存器中與自協商相關bit分別為:

bit12 AnegEn 該bit為自協商使能位(配置工程師需要保證雙絞線兩端的自協商使能位保持一致。如果一端自協商使能另一端自協商關閉,自協商使能這端會觸發并行檢測狀態機,可能會造成鏈路雙方的雙工狀態的不一致);

bit9 RestartAneg 該bit為重新自協商使能位,當本端自協商的廣告能力位有變化或者未能協商選擇鏈路雙方彼此最高階的廣告能力(如EMC等強電磁輻射造成的FLP Busrt信號畸變)時,需要軟件操作此bit設置1以重啟自協商進程;

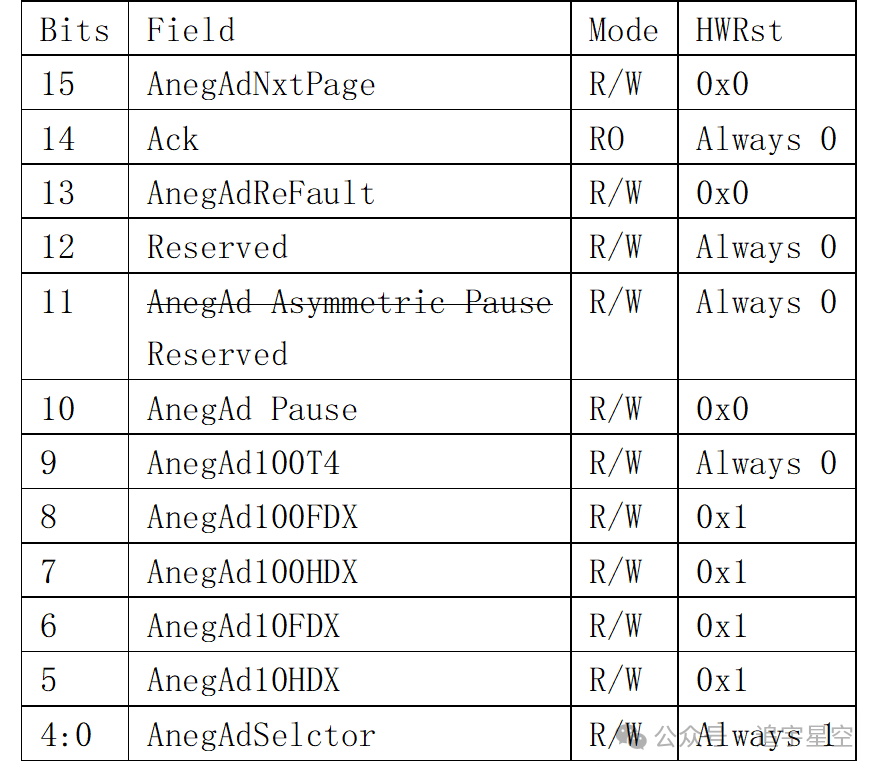

Auto-Negotiation Advertisement Register Register4

該本地廣告能力寄存器是10M/100M自協商的核心寄存器,現逐bit解釋:

bit15 AnegAdNxtPage 該bit為FLPBurst-BasePage的D15.NP,因為10M/100M自協商只使用BasePage,故此bit永遠為0;

bit14 Ack 該bit為FLPBurst-BasePage的D14.Ack,該bit由PHY芯片自協商狀態機自動維護,軟件無需設置此bit;

bit13 AnegAdReFault 該bit為FLPBurst-BasePage的D13.RF,軟件周期需要讀PHYStatus RegisterRegister 1的bit4 RemoteFault的狀態值,然后同步設置到此bit;

bit12 Reserved 該bit為FLPBurst-BasePage的D12.XNP,因為10M/100M自協商只使用BasePage,故此bit永遠為0;

bit11 AnegAd Asymmetric Pause 該bit為FLPBurst-BasePage的D11.A6,但10M/100MPHY通常不支持非對稱流控,故此bit為Reserved,永遠為0;

bit10 AnegAd Pause 該bit為FLPBurst-BasePage的D10.A5,該bit根據網絡管理員的實際應用需求靈活設置(置1有此能力,置0無此能力);

bit9 AnegAd 100T4 該bit為FLPBurst-BasePage的D9.A4,因為100Base-T4該物理層標準已經被淘汰,故該bit永遠為0;

bit8 AnegAd100FDX 該bit為FLPBurst-BasePage的D8.A3,該bit為100Base-TX全雙工能力,根據網絡管理員的實際應用需求靈活設置(置1有此能力,置0無此能力);

bit7 AnegAd100HDX 該bit為FLPBurst-BasePage的D7.A2,該bit為100Base-TX半雙工能力,根據網絡管理員的實際應用需求靈活設置(置1有此能力,置0無此能力);

bit6 AnegAd10FDX 該bit為FLPBurst-BasePage的D6.A1,該bit為10Base-T全雙工能力,根據網絡管理員的實際應用需求靈活設置(置1有此能力,置0無此能力);

bit5 AnegAd10HDX 該bit為FLPBurst-BasePage的D5.A0,該bit為10Base-T半雙工能力,根據網絡管理員的實際應用需求靈活設置(置1有此能力,置0無此能力);

bit[4:0] Selector Field 該bits為FLPBurst-BasePage的D4:D0.[S4:S0],該bits永遠為1,表示該自協商為基于IEEE802.3以太網的自協商(比如該bits為0x4表示基于IEEE1394的自協商,該bits為0x5表示為基于INCITS的T10 SCSI、T11FC、T13 SATA的自協商);

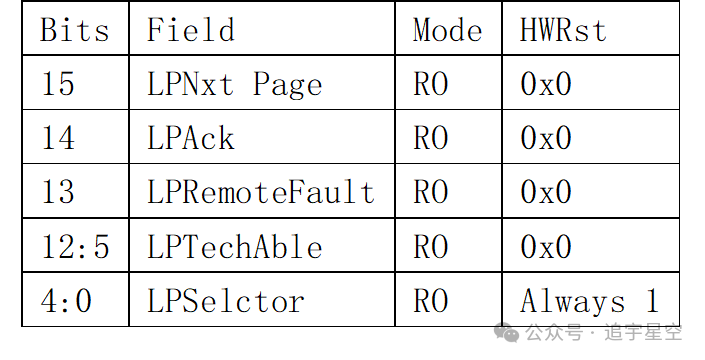

Link Partner Ability Register (Base Page)Register 5

該鄰居廣告能力狀態寄存器是將遠端發送的FLPBurst-BasePage的信息存儲在本寄存器。如果自協商協商失敗從而鏈路雙方不能正常建立鏈接,相關驅動工程師可以利用本寄存器進行故障定位和分析。本寄存器bit定義與“Auto-Negotiation AdvertisementRegister Register 4”完全相同,故這里就不再贅述了。

10M/100M自協商基理

10M/100M自協商,主要協商的內容為“速度雙工”和“流控”兩大類,下面就這兩大類內容進行闡述。

速度雙工協商

速度雙工主要靠設置“本地廣告能力寄存器Auto-Negotiation Advertisement Register Register 4”的bit9:5實現的。本端和遠端選擇彼此都有的能力(bit9:5中的置1的相關bit)中優先級高的那種能力作為本端PHY和遠端PHY的實際工作的速度雙工狀態。

PHY能力優先級由高到低排序如下:

100BASE-T2full duplex[需使用NextPage,實際是沒有芯片支持此能力]

100BASE-TX full duplex

100BASE-T2[需使用NextPage,實際是沒有芯片支持此能力]

100BASE-T4[實際是沒有芯片支持此能力]

100BASE-TX half duplex

10BASE-T full duplex

10BASE-T half duplex

例子1:本端PHY的“本地廣告能力寄存器Auto-Negotiation Advertisement Register Register 4”的bit9:5=2b01111;雙絞線另一側的遠端PHY的“本地廣告能力寄存器Auto-Negotiation Advertisement Register Register 4”的bit9:5=2b00101。此時他倆的彼此能力的交集為bit9:5=2b00101,即雙絞線鏈路雙方都支持的PHY能力為bit5=1(10BASE-T half duplex)和bit7=1(100BASE-T half duplex),并且因為優先級順序為100BASE-T half duplex>10BASE-T half duplex,故此時本端和遠端速度雙工自協商的結果為“100BASE-T half duplex”;

例子2:本端PHY的“本地廣告能力寄存器Auto-Negotiation Advertisement Register Register 4”的bit9:5=2b01110;雙絞線另一側的遠端PHY的“本地廣告能力寄存器Auto-Negotiation Advertisement Register Register 4”的bit9:5=2b00110。此時他倆的彼此能力的交集為bit9:5=2b00110,即雙絞線鏈路雙方都支持PHY能力為bit6=1(10BASE-T full duplex)和bit7=1(100BASE-T half duplex),并且因為優先級順序為100BASE-T half duplex>10BASE-T full duplex,故此時本端和遠端速度雙工自協商的結果為“100BASE-T half duplex”;

例子3:本端PHY的“本地廣告能力寄存器Auto-Negotiation Advertisement Register Register 4”的bit9:5=2b01010;雙絞線另一側的遠端PHY的“本地廣告能力寄存器Auto-Negotiation Advertisement Register Register 4”的bit9:5=2b00101。此時他倆的彼此能力的交集為bit9:5=2b00000,即雙絞線鏈路雙方沒有PHY能力交集,故此時本端和遠端永遠無法建立正確鏈接。

寫到這里,可能有小伙伴感覺到疑惑,既然88e6097F PHY默認支持bit9:5=2b01111,為什么還有將部分PHY能力主動設置為0的需求。講到這里我們必須有一個基本的認知就是:10Base-T全雙工的可靠性和鏈路冗余度是遠遠強于100Base-TX全雙工的(通常cat5e的網線在100Base-TX時支持160米左右的無損傳輸,而cat5e的網線在10Base-T時支持210米左右的無損傳輸;同樣的輻射抗擾度RS的干擾下10Base-T的丟包率也遠小于100Base-TX)。如果應用層的實際單寬需求小于10Mbps,此時遠端第三方設備bit9:5=2b01111(可能無用戶側配置接口)的場景下,本端可以主動設置bit9:5=2b00011,以保證本端遠端最終協商于10Base-T全雙工模式。

流控協商

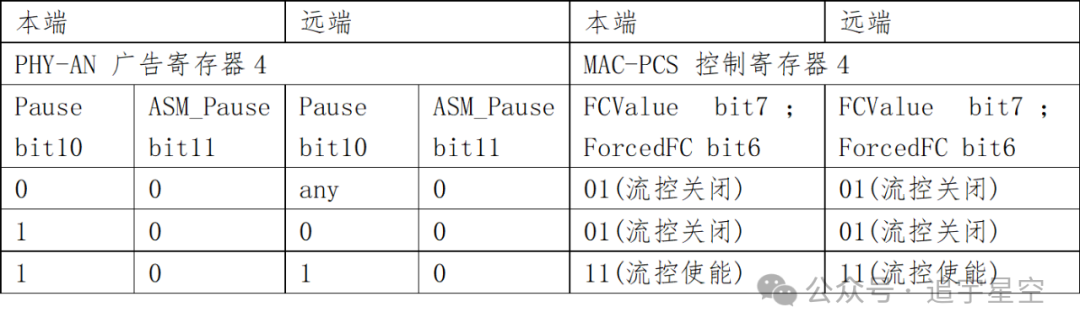

流控主要靠設置“本地廣告能力寄存器Auto-Negotiation Advertisement Register Register 4”的bit11:10實現的。軟件通過本端和遠端的bit11:10的各種組合進行對本端MAC的tx和rx方向的802.3流控進行設置,因為10/100M PHY不支持非對稱流控,故bit11永遠為0,具體規則如下表:

MAC-PCS控制寄存器需要軟件根據“PHY-AN廣告寄存器”和“PHY-AN LP廣告狀態寄存器”的內容進行動態更新配置,交換芯片硬件并不會自動聯動。

流控設置之所以有上表的規則要求,是需要保證雙絞線鏈路雙方的流控狀態一致。如果出現一端流控使能,一端流控關閉,在鏈路擁塞時不但不能享受流控的優點,反而會引起鏈路中出現大量Pause流控幀使已經擁塞的鏈路更加擁塞。

審核編輯:劉清

-

以太網

+關注

關注

40文章

5573瀏覽量

174623 -

寄存器

+關注

關注

31文章

5412瀏覽量

123181 -

雙絞線

+關注

關注

2文章

258瀏覽量

24029 -

PHY

+關注

關注

2文章

313瀏覽量

52456 -

狀態機

+關注

關注

2文章

493瀏覽量

28048

原文標題:以太網自協商機制--雙絞線自協商(二)

文章出處:【微信號:FPGA開源工坊,微信公眾號:FPGA開源工坊】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

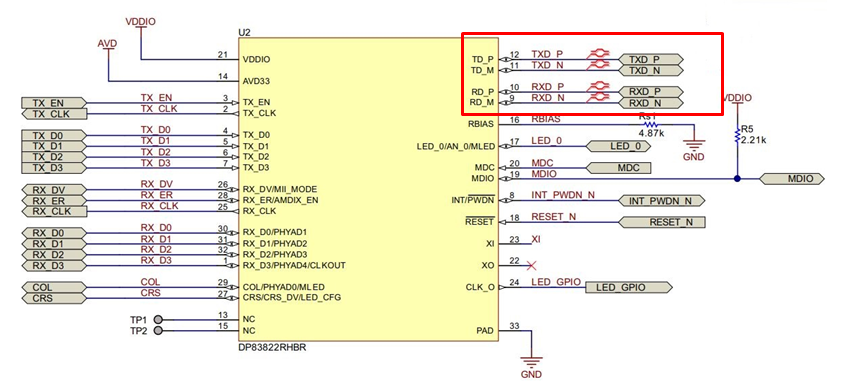

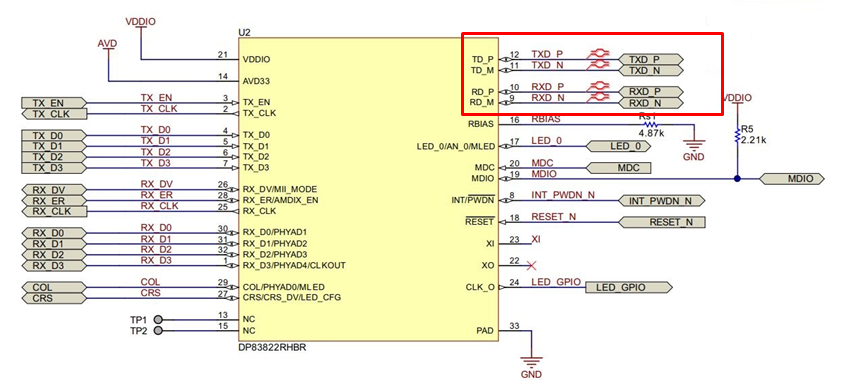

DP83822I工業以太網PHY自協商功能與其Strap電阻配置

為什么以太網+柔性板與電腦無法協商為100M?

基于DP83822I工業以太網PHY自協商功能與其Strap電阻配置

FPGA光纖以太網自協商的設計

基于語義網技術的SLA協商機制

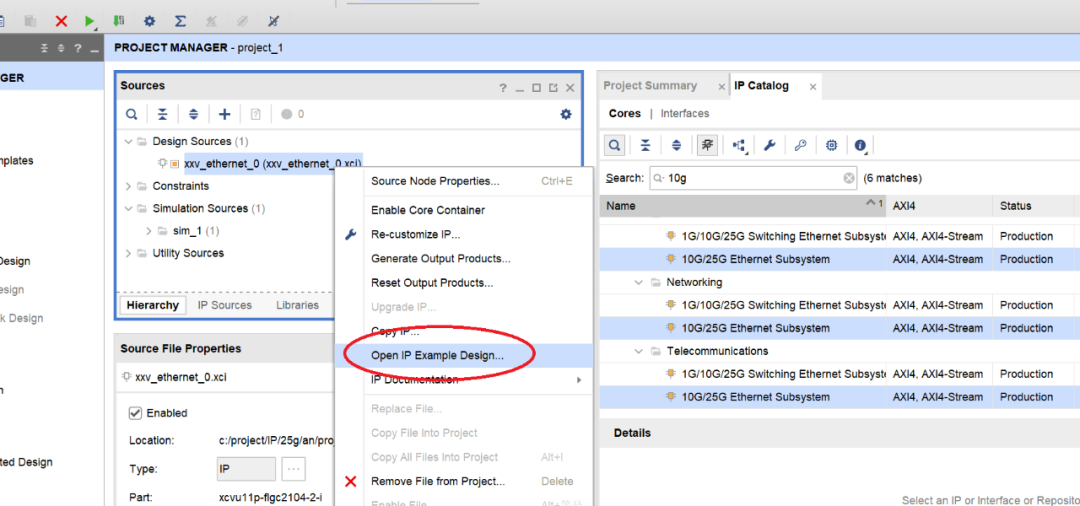

如何調試10G/25G以太網IP自協商/Link Training

10G/25G以太網IP自協商調試方案

以太網網口自協商功能現象

DP83822I工業以太網PHY自協商功能與其Strap電阻配置

一文解析以太網自動協商技術

基于IEEE Clause 28雙絞線的以太網自協商機制

基于IEEE Clause 28雙絞線的以太網自協商機制解析(一)

以太網自協商機制-雙絞線自協商案例設計(二)

以太網自協商機制-雙絞線自協商案例設計(二)

評論