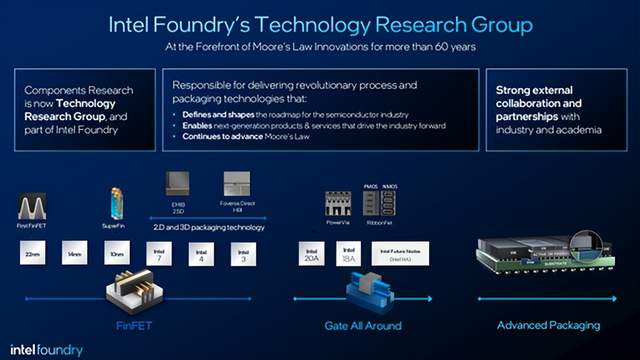

這就是英特爾的3D芯片堆疊技術(shù)。

Foveros封裝技術(shù)是英特爾推出的一種3D封裝技術(shù),它可以在處理器制造過程中以垂直方式堆疊計(jì)算模塊,而不是傳統(tǒng)的水平方式。這種技術(shù)使得芯片制造更加高效,同時(shí)也有助于優(yōu)化成本和能效。Foveros封裝技術(shù)使英特爾及其代工客戶能夠集成不同的計(jì)算芯片,在單個(gè)封裝中實(shí)現(xiàn)更為復(fù)雜的異構(gòu)芯片生產(chǎn)。它被認(rèn)為是一種非常重要的技術(shù),可以為未來的先進(jìn)封裝技術(shù)創(chuàng)新打下基礎(chǔ)。

Foveros 不是一個(gè)裸片在另一個(gè)裸片的頂部活動(dòng),而后者本質(zhì)上只是密集的導(dǎo)線,F(xiàn)overos 涉及兩個(gè)包含活動(dòng)元素的裸片。有了這個(gè),英特爾第一代 Foveros 于 2020 年 6 月在 Lakefield 混合 CPU SOC 中推出。該芯片不是特別大的容量或令人嘆為觀止的芯片,但它是英特爾的許多第一款芯片,包括 3D 封裝和他們的第一個(gè)混合 CPU 內(nèi)核具有大性能核心和小效率核心的架構(gòu)。它采用了 55 微米的凸點(diǎn)間距。

據(jù)介紹,包括第 13 代英特爾酷睿處理器等大多數(shù)英特爾客戶端產(chǎn)品都將多種功能(如 CPU、GPU、PCH) 整合到一個(gè)被稱為 SoC 的單片上,但隨著這些功能日趨多樣化并且變得越來越復(fù)雜,設(shè)計(jì)和制造這些單片式系統(tǒng)級(jí)芯片的難度越來越大,成本也越來越高。

英特爾 Foveros 先進(jìn)封裝技術(shù)一舉解決了這個(gè)挑戰(zhàn),利用高密度、高帶寬、低功耗互連,能夠把采用多種制程工藝制造的諸多模組合成大型分離式模塊架構(gòu)組成的芯片復(fù)合體。

Foveros封裝技術(shù)作為英特爾的一項(xiàng)創(chuàng)新技術(shù),確實(shí)面臨了一些技術(shù)難點(diǎn)。

首先,F(xiàn)overos技術(shù)的核心在于實(shí)現(xiàn)芯片的3D堆疊,這涉及到如何將不同芯片之間進(jìn)行精確對(duì)準(zhǔn)和連接。由于芯片之間的間距很小,對(duì)準(zhǔn)的精度要求非常高,這需要高精度的制造設(shè)備和工藝控制技術(shù)。

其次,3D堆疊技術(shù)需要解決不同芯片之間的電氣連接問題。由于不同芯片之間的厚度、材料和工藝可能存在差異,因此需要進(jìn)行特殊的設(shè)計(jì)和優(yōu)化,以確保信號(hào)的傳輸質(zhì)量和穩(wěn)定性。

Foveros技術(shù)還需要解決散熱問題。由于芯片是3D堆疊的,散熱路徑變得更加復(fù)雜和困難。如何有效地將熱量從堆疊的芯片中導(dǎo)出,并散布到散熱器或散熱系統(tǒng)中,是一個(gè)需要克服的難題。

Foveros技術(shù)的生產(chǎn)成本也是一個(gè)需要考慮的問題。雖然該技術(shù)可以提高芯片的集成密度和性能,但是其制造成本也相對(duì)較高。因此,如何平衡技術(shù)性能和生產(chǎn)成本之間的關(guān)系,是英特爾需要面臨的挑戰(zhàn)之一。

Foveros封裝技術(shù)作為一項(xiàng)創(chuàng)新的技術(shù),其技術(shù)難度和成本都是需要考慮和解決的問題。然而,隨著技術(shù)的不斷進(jìn)步和應(yīng)用需求的增加,相信Foveros技術(shù)將會(huì)得到更廣泛的應(yīng)用和發(fā)展。

審核編輯:黃飛

-

處理器

+關(guān)注

關(guān)注

68文章

19799瀏覽量

233440 -

英特爾

+關(guān)注

關(guān)注

61文章

10165瀏覽量

173875 -

3D芯片

+關(guān)注

關(guān)注

0文章

52瀏覽量

18682 -

Foveros

+關(guān)注

關(guān)注

1文章

4瀏覽量

3164

發(fā)布評(píng)論請(qǐng)先 登錄

用于LED封裝推拉力測(cè)試的設(shè)備有哪些型號(hào)?#推拉力測(cè)試#

尹志堯坦言:"光刻機(jī)的作用正在不斷減少!",芯片制造從追求更小制程到更重視先進(jìn)封裝 #芯片封裝 #華芯邦

中國(guó)芯片被美國(guó)“卡脖子”?先進(jìn)封裝Chiplet或許就是破局關(guān)鍵!#先進(jìn)封裝 #芯片封裝 #華芯邦 #

三分鐘帶你搞懂,芯片封裝的發(fā)展路徑!你知道封裝技術(shù)都有哪些嗎?#華芯邦 #芯片封裝 #封裝路徑 #芯片制造

傳統(tǒng)封裝你了解多少,小白快捷學(xué)習(xí) | 第1集 #傳統(tǒng)封裝 #先進(jìn)封裝 #芯片封裝 #華芯邦 #

中美貿(mào)易戰(zhàn),國(guó)產(chǎn)芯片發(fā)展艱難,先進(jìn)封裝助力中國(guó)芯突圍!#芯片封裝 #先進(jìn)封裝 #華芯邦 #

半導(dǎo)體未來三大支柱:先進(jìn)封裝、晶體管和互連

sop框架焊點(diǎn)推力sop封裝 二極管sot封裝推拉力測(cè)試機(jī)測(cè)試參數(shù)設(shè)置

什么是Foveros封裝?Foveros封裝的難點(diǎn)

什么是Foveros封裝?Foveros封裝的難點(diǎn)

評(píng)論