來源:XILINX開發者社區

Q1請問如何知道一個板子上所能運行的最大時鐘頻率?

如果查手冊應該是芯片手冊還是板子手冊呢?

對應手冊的關鍵字應該是什么呢?

比如我的芯片是KCU115,但是搜索出來的沒有這個芯片的資料,我應該怎么獲取它的手冊呢?

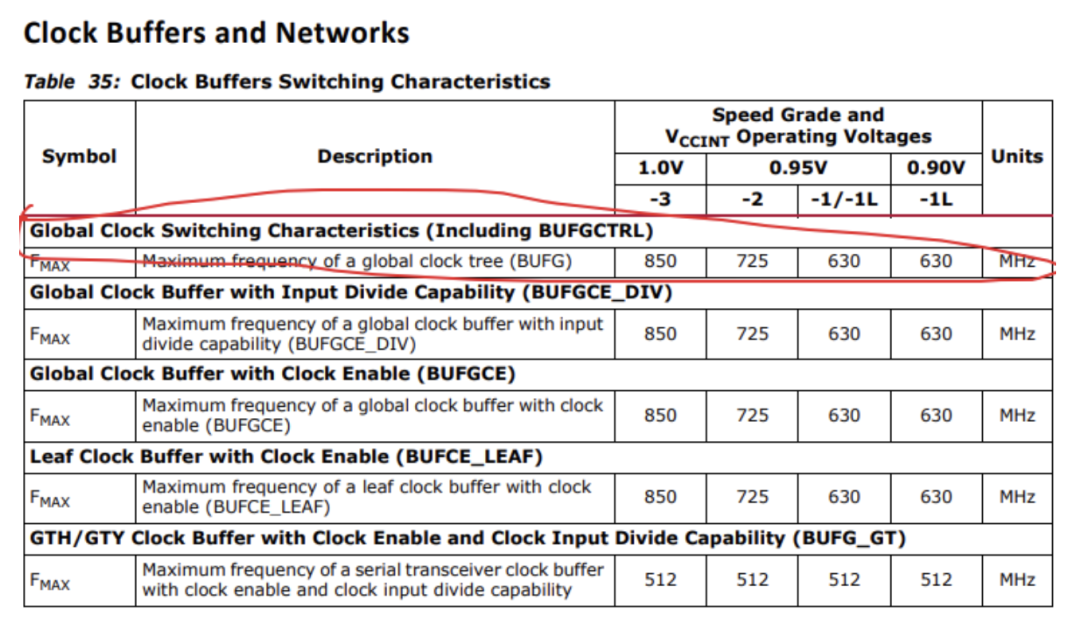

A:可以查看Kintex UltraScale FPGA Data Sheet: DC and AC Switching Characteristics (DS892)手冊中關于BUFG的部分。另外,還應結合設計的時序情況:

Q2我發現FIFO這些IP的最高頻率達到400MHz+,而在實際應用中,板子沒有跑到這么高的頻率,是不是板子資源有限制?

A:實際邏輯在board上能跑到的頻率和設計本身強相關:資源使用情況,代碼風格,fanout情況,邏輯級數,控制邏輯的數目...等等。

Q3ILA IP 的最大頻率是250M,但是一般300M給到ILA沒有出現問題,時序報告也沒有警告,這是什么原因呢?

A:ILA IP是用普通邏輯搭建的,實際能跑到的頻率和采樣數據的數量和原有邏輯資源的使用量基本成反比。

審核編輯:湯梓紅

-

芯片

+關注

關注

459文章

52145瀏覽量

435933 -

Xilinx

+關注

關注

73文章

2181瀏覽量

124323 -

時鐘頻率

+關注

關注

0文章

50瀏覽量

20614

原文標題:【Vivado那些事兒】一個板卡上所能運行的最大時鐘頻率?

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如何知道一個板卡上所能運行的最大時鐘頻率

如何知道一個板卡上所能運行的最大時鐘頻率

評論