一般來說,復(fù)位信號有效后會保持比較長一段時間,確保 register 被復(fù)位完成。但是復(fù)位信號釋放時,因為其和時鐘是異步的關(guān)系,我們不知道它會在什么時刻被釋放。

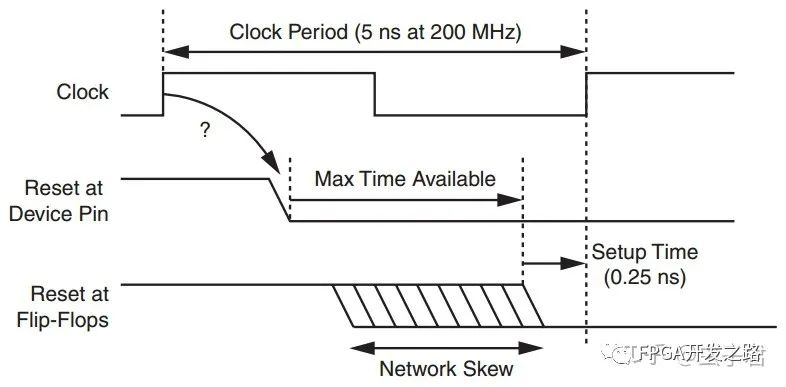

首先看圖1,考慮復(fù)位信號在兩個時鐘沿之間被釋放的情況。Reset 信號從 Device Pin 到 Flip-Flop 的延遲最大不能超過“Max Time Available”,如果延遲超過了這個限制,那么復(fù)位信號的釋放會進入 Setup Time 要求的區(qū)間,導(dǎo)致 Flip-Flop 進入亞穩(wěn)態(tài)。當時鐘頻率變高,時鐘周期變短,不難發(fā)現(xiàn),要滿足這個要求是越來越難的。

圖1 - Reset timing diagram, deasserted between clock edges

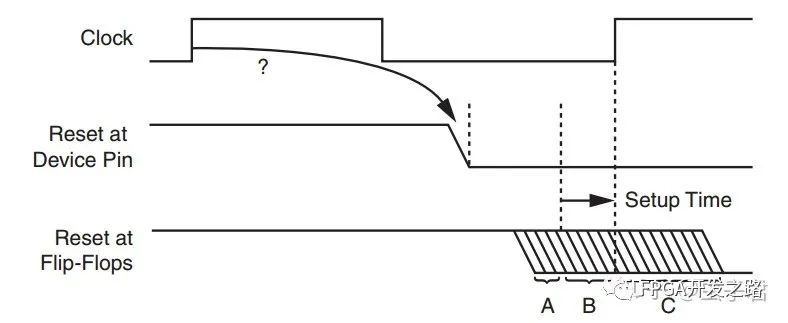

前面我們提到過,因為是異步信號,我們無法確保信號的釋放在一個確定的區(qū)間。如圖2所示,對于 Flip-Flop 來說,異步信號的釋放可能在A區(qū)間,也可能在B或者C區(qū)間。假設(shè)現(xiàn)在我們的設(shè)計中包含三個 Flip-Flop,分別為FF1,F(xiàn)F2 和 FF3。FF1 的復(fù)位釋放落在A區(qū)間,所以 FF1 會在復(fù)位信號釋放后的第一個時鐘沿有效,F(xiàn)F3 的復(fù)位釋放落在C區(qū)間,那么 FF3 會在復(fù)位信號釋放后的第二個時鐘沿有效,而 FF2 的復(fù)位釋放落在B區(qū)間,所以 FF2 可能會進入亞穩(wěn)態(tài)。

圖2 - Reset deasserted asynchronously to the clock

不同的 FF 因為復(fù)位信號釋放的位置不同而在不同的時刻有效,這會對設(shè)計造成影響嗎?

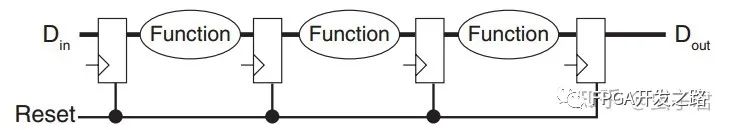

假如我們的設(shè)計是如圖3所示的情況,是不會對設(shè)計的功能造成影響的。在復(fù)位釋放之后,任何有問題的數(shù)據(jù)會被Pipeline排出去,經(jīng)過4個cycle之后,這個pipeline便會恢復(fù)到正常的工作狀態(tài)。

圖3 - Reset for a pipeline

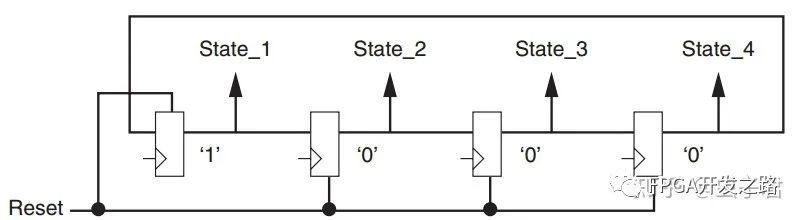

但如果我們的設(shè)計是如圖4所示。被復(fù)位的FF是狀態(tài)機的狀態(tài),那么復(fù)位釋放后很有可能狀態(tài)機會被復(fù)位到一個無效的狀態(tài),影響正常的功能。

圖4 - Reset for a one-hot state machine

什么是同步釋放 ?

從上一部分的內(nèi)容我們發(fā)現(xiàn),異步信號的異步釋放會導(dǎo)致 FF 在不同的時刻有效,甚至進入亞穩(wěn)態(tài),從而影響設(shè)計的功能運行。如何避免這個問題呢?考慮同步釋放。顧名思義,同步釋放就是讓復(fù)位信號的釋放過程與時鐘同步,從而確保所有 FF 在同一時刻有效。

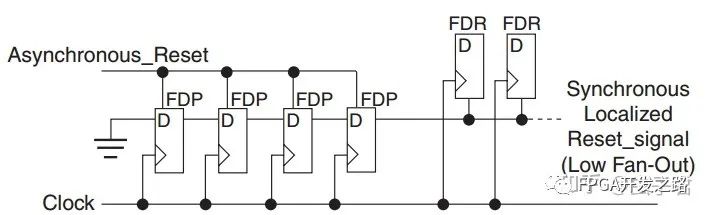

如圖5所示,是異步復(fù)位同步釋放的電路設(shè)計。FDP的個數(shù)決定復(fù)位信號保持的長度,最少要有兩個。當復(fù)位信號釋放后,F(xiàn)DP chain 會將接地的0逐級pipe到最后一個FDP輸出,因為該FDP的輸出是和Clock同步的,所以FDR的復(fù)位釋放便是和Clock 同步的。

圖5 - Async reset with sync dessertion

最后一個FDP不是仍然是異步復(fù)位異步釋放么,會不會這個FDP因為異步釋放進入亞穩(wěn)態(tài),那么其輸出的復(fù)位信號也不確定從而導(dǎo)致復(fù)位失敗?

答案是不會。FDP會進入亞穩(wěn)態(tài)的條件是什么?一是異步釋放非常貼近時鐘沿,二是 FDP 輸入D在時鐘沿附近發(fā)生跳變。根據(jù)這個電路設(shè)計,F(xiàn)DP的輸入D時不會在異步釋放時發(fā)生跳變的,所以FDP不會進入亞穩(wěn)態(tài)。

異步復(fù)位同步釋放的時序約束

異步復(fù)位同步釋放的電路我們已經(jīng)設(shè)計好了,如何進行時序約束呢?

對于 FDR,我們可以不用考慮的。因為工具會分析復(fù)位信號的 Recovery Time 和 Removal Time 來確保時序收斂。如果發(fā)現(xiàn) Recovey Time 或者 Removal Time 的違反,我們可能需要看一下 reset tree 或者 clock skew。一般都是 Recovey Time的違反,類似于 Setup Time,可能是由于 reset path的延遲太長導(dǎo)致。

對于 FDP,D端是同步電路,而CLR輸入端是異步信號,通過電路的設(shè)計我們已經(jīng)避免的異步信號帶來的問題,所以為了避免 false timing violation,我們可以對 FDP 的 CLR 端設(shè)置 false path。

審核編輯:劉清

-

FPGA設(shè)計

+關(guān)注

關(guān)注

9文章

428瀏覽量

27131 -

狀態(tài)機

+關(guān)注

關(guān)注

2文章

493瀏覽量

28062 -

FDR

+關(guān)注

關(guān)注

0文章

11瀏覽量

8777 -

異步復(fù)位

+關(guān)注

關(guān)注

0文章

47瀏覽量

13469

原文標題:FPGA復(fù)位設(shè)計中異步復(fù)位為什么要同步釋放 ?

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Xilinx FPGA異步復(fù)位同步釋放—同步后的復(fù)位該當作同步復(fù)位還是異步復(fù)位?

同步復(fù)位sync和異步復(fù)位async

verilog 異步復(fù)位同步釋放

同步復(fù)位和異步復(fù)位有什么聯(lián)系與區(qū)別,優(yōu)缺點!

關(guān)于異步復(fù)位同步釋放理解與分析

同步復(fù)位與異步復(fù)位的區(qū)別

FPGA學習-異步復(fù)位,同步釋放

異步復(fù)位異步釋放會有什么問題?FPGA異步復(fù)位為什么要同步釋放呢?

異步復(fù)位異步釋放會有什么問題?FPGA異步復(fù)位為什么要同步釋放呢?

評論