PCI Express (PCIe) 是一種高性能通用 I/O 互連協(xié)議,廣泛用于各種計(jì)算產(chǎn)品和通信產(chǎn)品。由于時(shí)延低、帶寬明顯要更高,因此業(yè)界正在融合到 PCIe,作為高速串行總線標(biāo)準(zhǔn)。PCIe在NVM Express SSD應(yīng)用中尤其流行。

PCIe 既有串行通信接口,又有存儲(chǔ)接口,這 一點(diǎn)與 SAS 和 SATA 不同,因此實(shí)現(xiàn)了額外的行業(yè)擴(kuò)充能力。PCIe 在跟復(fù)合 (系統(tǒng)/主機(jī)) 與端點(diǎn) (插件) 之間基于點(diǎn)到點(diǎn)總線拓?fù)洌С秩p工通信。這些規(guī)范是由 PCI-SIG 開發(fā)和維護(hù)的,這是一家由 900 多家公司組成的協(xié)會(huì)。

PCIe 物理層包括

差分低壓100MHz基準(zhǔn)時(shí)鐘

可以擴(kuò)充通路寬度:x1, x2, x4, x8, x12, x16, x32

可以擴(kuò)充速度:2.5GT/s(Gen1), 5GT/s(Gen2), 8GT/s(Gen3), 16GT/s (Gen4)

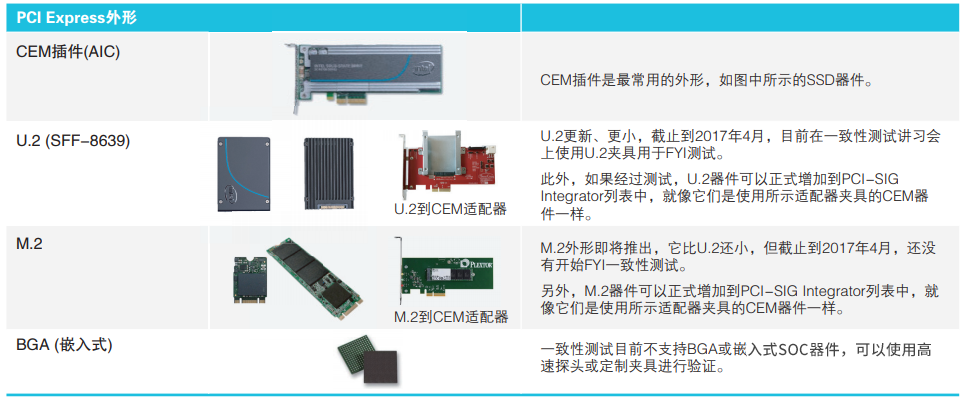

在一致性測(cè)試中使用不同的連接器,如CEM、U.2(SFF-8639)、M.2或直接焊接到PCB

ChrentPCI Express 它用在哪里?

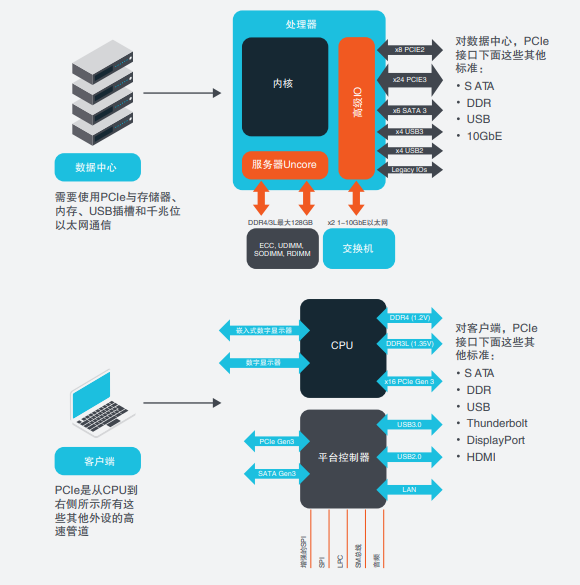

PCIe 是數(shù)據(jù)中心和客戶端應(yīng)用中使用的主要的新興高性能存儲(chǔ)和串行總線。PCIe 在外設(shè)之間實(shí)現(xiàn)了數(shù)據(jù)通信。

數(shù)據(jù)中心應(yīng)用和客戶端應(yīng)用都有一個(gè)核心處理器, 為主機(jī)系統(tǒng)上的架構(gòu)提供原始處理能力。這兩種應(yīng)用還必須接口各種外設(shè)器件,如 SATA 驅(qū)動(dòng)器、 USB 設(shè)備等。在跟復(fù)合主機(jī)與端點(diǎn)器件之間,通常有許多路長(zhǎng)損耗通道和連接器,帶來了噪聲、串?dāng)_、 定時(shí)不規(guī)則特點(diǎn)和其他損傷。因此,客戶端和數(shù)據(jù)中心側(cè)的 PCIe 器件必須能夠可靠地演示 PCI 規(guī)定的一致性,補(bǔ)償損傷,與 PCIe 器件互操作。

ChrentPCIe Gen4 最新進(jìn)展

由于業(yè)界需要提高數(shù)據(jù)吞吐量和帶寬吞吐量,因此 PCIe 數(shù)據(jù)速率必須提高,以跟上需求發(fā)展步伐。所以 Gen4 中最大的變化之一,是數(shù)據(jù)速率提高了 2 倍,從 Gen3 的 8GT/s 提高到 Gen4 的 16GT/s。

下面列明了最新Gen4標(biāo)準(zhǔn)的主要增強(qiáng)功能

16GT/s, 使用加擾 , 與 8GT/s 相同 , 編碼與Gen3相比無變化 (128b/130b)

對(duì)加壓的Rx眼圖參數(shù),RJ (隨機(jī)性抖動(dòng)) 從3ps (PCIe3)下降到~1ps (PCIe4)

Gen4連接器向下兼容Gen1/2/3

與行為Rx EQ數(shù)據(jù)速率有關(guān)

限定通道:對(duì)更長(zhǎng)的通道和/或第二個(gè)連接器,要求使用中繼器 (再驅(qū)動(dòng)器和再定時(shí)器)

測(cè)試通道大約長(zhǎng)12”,總損耗-28dB

在同一個(gè)器件上同時(shí)測(cè)試Gen3和Gen4時(shí),被測(cè)試的各個(gè)預(yù)置值數(shù)量將翻一倍, 總 計(jì)22個(gè)。Gen3 有11個(gè)預(yù)置值(P0~P10),Gen4有11個(gè)預(yù)置值 (P0~P10)

新的SRIS獨(dú)立RefClk模式-SRNS-單獨(dú)的獨(dú)立RefClk, 沒有SSC結(jié)構(gòu)-SRIS-單獨(dú)的獨(dú)立RefClk,采用SSC結(jié)構(gòu)

新的Rx通路裕量功能測(cè)量通道最后的眼高 (EH)/ 眼寬 (EW) 裕量

Gen4的最小眼高已經(jīng)下降到15mVpp

Gen4 CEM規(guī)范發(fā)布了rev 0.5

ChrentPCIe Refclk 結(jié)構(gòu)

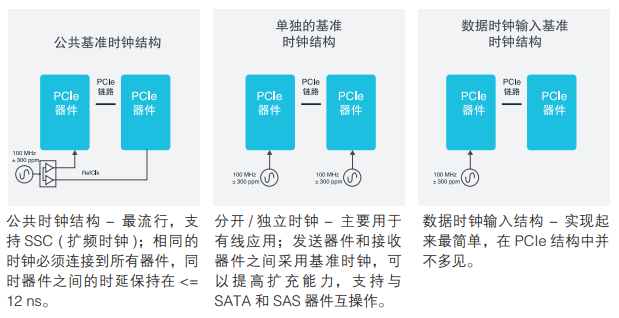

為了方便發(fā)射器件和接收器件可靠地傳輸數(shù)據(jù),PCI-SIG 對(duì)基準(zhǔn)時(shí)鐘提出了非常嚴(yán)格的要求。標(biāo)準(zhǔn)規(guī)定使用 100 MHz 時(shí)鐘 (Refclk),發(fā) 射器件和接收器件上的頻率穩(wěn)定性大于 ±300 ppm,并支持三種不同的時(shí)鐘結(jié)構(gòu),同時(shí)協(xié)調(diào)根復(fù)合芯片和端點(diǎn)芯片。

在傳統(tǒng)上,PCIe 一直采用公共時(shí)鐘結(jié)構(gòu),跟復(fù)合和芯片可以偏離相同的時(shí)鐘配置,而不是以不同的間隔運(yùn)行,后者測(cè)試起來更具有挑戰(zhàn)性。公共時(shí)鐘是 一種更加精確的結(jié)構(gòu),但整合到系統(tǒng)中的靈活性較差。通過采用 Gen4 標(biāo)準(zhǔn),系統(tǒng)可望更多地采用分開 / 獨(dú)立的時(shí)鐘結(jié)構(gòu)。時(shí)鐘穩(wěn)定性必不可少,以支持三種不同的時(shí)鐘輸入結(jié)構(gòu)。

ChrentPCI Express 外形

為了方便發(fā)射器件和接收器件可靠地傳輸數(shù)據(jù),PCI-SIG 對(duì)基準(zhǔn)時(shí)鐘提出了非常嚴(yán)格的要求。標(biāo)準(zhǔn)規(guī)定使用 100 MHz 時(shí)鐘 (Refclk),發(fā)射器件和接收器件上的頻率穩(wěn)定性大于 ±300 ppm,并支持三種不同的時(shí)鐘結(jié)構(gòu),同時(shí)協(xié)調(diào)根復(fù)合芯片和端點(diǎn)芯片。

Chrent一致性測(cè)試預(yù)置值

為通過一致性測(cè)試,實(shí)現(xiàn)互操作,每臺(tái)器件都要求進(jìn)行 PCI-SIG 認(rèn)證,它基于一個(gè)預(yù)置值或發(fā)射機(jī)均衡設(shè)置列表,從每秒 2.5 Gb/s 的低 數(shù)據(jù)速率直到最新的 16 Gb/s 的高數(shù)據(jù)速率。這些預(yù)置值用來均衡通道損耗,優(yōu)化鏈路上的信號(hào)完整性。每個(gè)預(yù)置值都是主機(jī)應(yīng)用到端 點(diǎn)的下沖和去加重的具體組合。

下表詳細(xì)列出了 Gen3 和 Gen4 的 11 種預(yù)置值。DUT 必須支持所有預(yù)置值。為降低測(cè)試時(shí)間,提高自動(dòng)化速度,建議使用 100MHz 時(shí)鐘突發(fā),作為一致性測(cè)試夾具的輸入,在這些預(yù)置值之間快速切換。如果您可以使用 100MHz 脈沖撥碼開關(guān)自動(dòng)執(zhí)行預(yù)置測(cè)試,那么您可以節(jié)約寶貴的測(cè)試時(shí)間,因?yàn)槟梢宰詣?dòng)采集和分析各個(gè)指標(biāo),如抖動(dòng)、電壓和定時(shí)。

下面預(yù)置值同時(shí)適用發(fā)射機(jī)測(cè)試和接收機(jī)測(cè)試。

Chrent發(fā)射機(jī) (Tx) 測(cè)試基礎(chǔ)知識(shí)

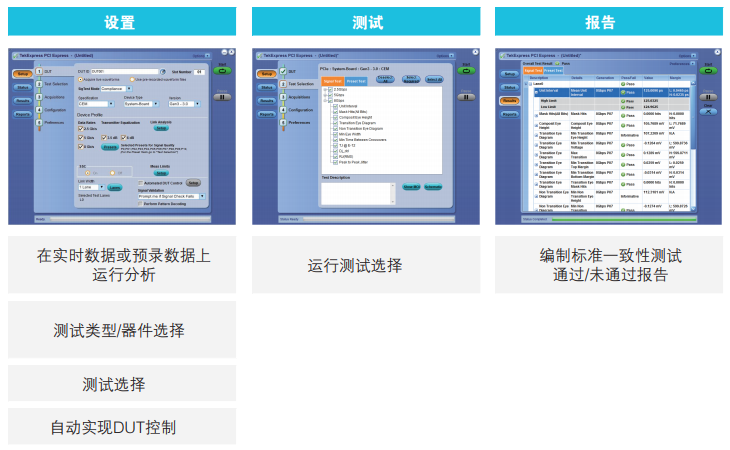

下面列明了對(duì) PCIe 發(fā)射機(jī)自動(dòng)進(jìn)行一致性測(cè)試的各個(gè)步驟。自動(dòng)軟件至關(guān)重要,因?yàn)樗梢允褂?100 MHz 基準(zhǔn)時(shí)鐘自動(dòng)切換預(yù)置測(cè)試模式,與手動(dòng)按鈕進(jìn)行撥碼切換相比,可以把測(cè)試時(shí)間縮短兩倍。

許多 PCI-SIG 測(cè)試早期實(shí)現(xiàn)者更愿意使用泰克 DPOJET 和 SDLA 軟件之類的工具,來完成早期 Gen4 表征和調(diào)試。

Chrent基本規(guī)范發(fā)射機(jī) (Tx) 測(cè)試

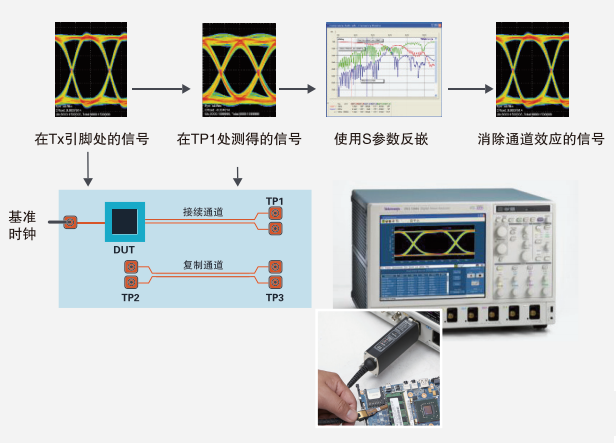

在芯片器件的基本發(fā)射機(jī)測(cè)試中,直接規(guī)定了發(fā)射機(jī)引腳上的測(cè)量項(xiàng)目。由于有時(shí)不可能接入引腳,因此應(yīng)在盡可能靠近這個(gè)基準(zhǔn)點(diǎn)的位置執(zhí)行測(cè)量。

在芯片級(jí)可通過多種方式完成這一測(cè)試

如果您深入了解類似的復(fù)制通道的S參數(shù),那么可以反嵌接續(xù)通道的損耗。您可以看到發(fā)射機(jī)引腳上的信號(hào)是什么樣的,而沒有增加通道影響。

在示波器上使用均衡或CTLE,均衡消除通道損耗。

使用高帶寬探頭,探測(cè)位置應(yīng)盡可能靠近發(fā)射機(jī)引腳 。

示波器可以使用 SDLA、Seasim 和 SigTest 之類 的軟件工具,執(zhí)行嵌入 / 反嵌、均衡和眼圖分析。這種軟件級(jí)分析允許設(shè)計(jì)人員在試產(chǎn)前優(yōu)化和調(diào)試芯片性能,節(jié)約時(shí)間、資金及全面調(diào)試。確保采用的測(cè)量系統(tǒng)足夠靈活,能夠測(cè)試和調(diào)試被測(cè)器件的特定功能。

ChrentCEM 和 U.2 規(guī)范發(fā)射機(jī) (Tx) 測(cè)試

在芯片器件的基本發(fā)射機(jī)測(cè)試中,直接規(guī)定了發(fā)射機(jī)引腳上的測(cè)量項(xiàng)目。由于有時(shí)不可能接入引腳,應(yīng)在盡可能靠近此基準(zhǔn)點(diǎn)的位置執(zhí)行測(cè)量。

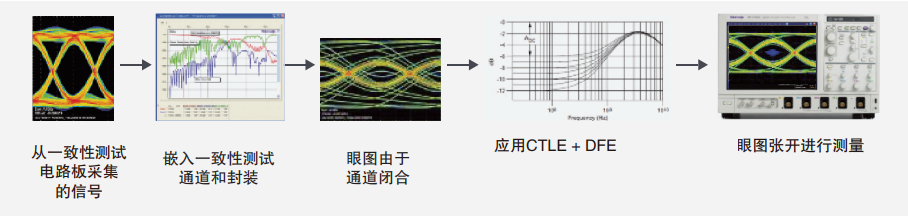

系統(tǒng)和插件在CEM級(jí)發(fā)射機(jī)測(cè)試中,會(huì)像接收機(jī)分片器看到的那樣測(cè)量發(fā)射機(jī)的信號(hào)完整性,但由于外形及測(cè)試過程中使用的夾具,不可能直接接入信號(hào)。為保證測(cè)量精度,應(yīng)實(shí)現(xiàn)下面介紹了兩個(gè)重要組件。

1. 把一致性測(cè)試通道的性能特點(diǎn)向回嵌入到正在測(cè)量的信號(hào)中。這要求深入了解通道的插入損耗和S參數(shù)。由于這個(gè)原因,PCI-SIG為CEM測(cè)試提供了一致性測(cè)試夾具及已知的S參數(shù)。

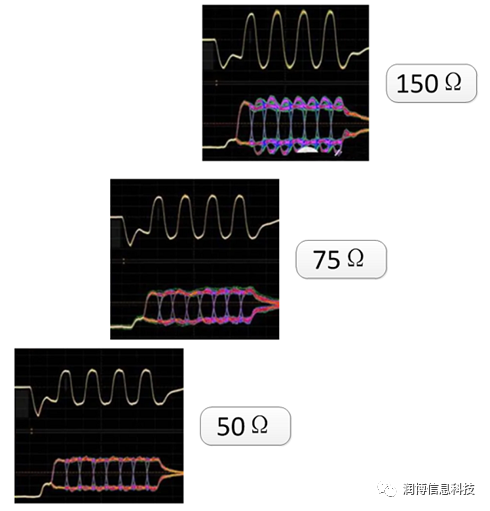

2. 使用軟件工具應(yīng)用通道均衡,測(cè)量和分析通道末端張開的眼圖。PCI-SIG提供了一個(gè)軟件工具,稱為SIG-Test,應(yīng)用與PCI-SIG特性有關(guān)的行為均衡器,提供測(cè)試通過/未通過結(jié)果。定制示波器軟件,如泰克DPOJET和SDLA,可以從閉上的眼圖到張開的眼圖,全面表征和調(diào)試均衡的信號(hào)。

Chrent接收機(jī) (Rx) 測(cè)試基礎(chǔ)知識(shí)

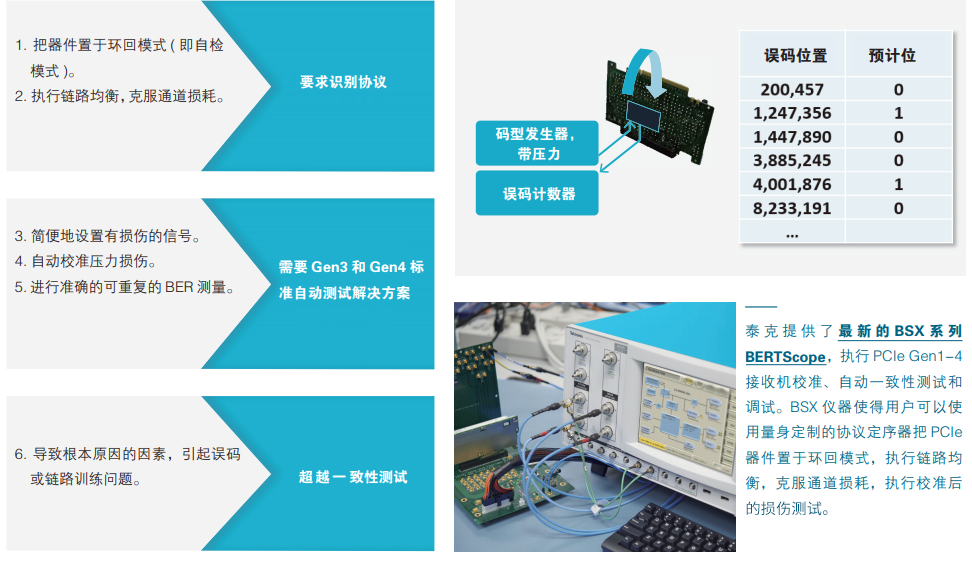

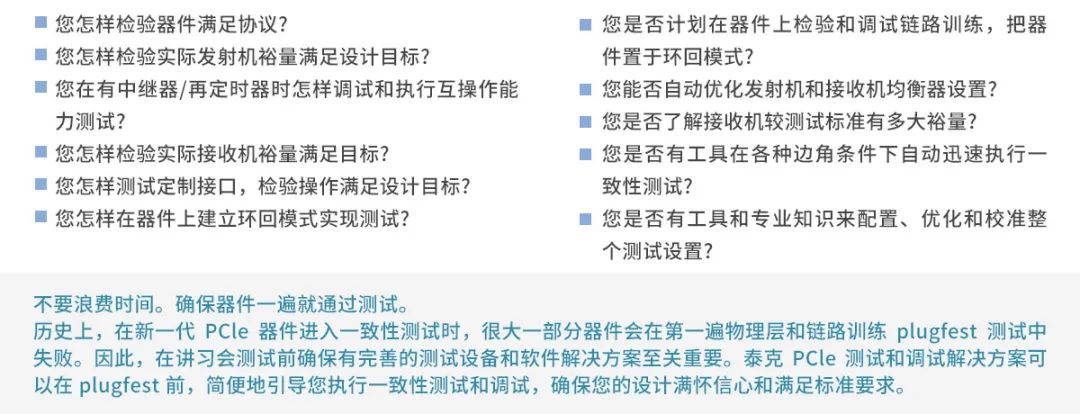

ChrentPCIe 測(cè)試和調(diào)試設(shè)置中的關(guān)鍵考慮因素

由于Gen 4標(biāo)準(zhǔn)的出現(xiàn),PCIe的速度和復(fù)雜度正不斷提高,工程師面臨著新的設(shè)計(jì)挑戰(zhàn)、更短的產(chǎn)品開發(fā)周期,同時(shí)需要了解新的標(biāo)準(zhǔn)規(guī)范及新的一致性測(cè)試要求。

在您處理Gen3或Gen4 PCIe器件測(cè)試和調(diào)試前,要問以下幾個(gè)關(guān)鍵問題:

-

測(cè)試

+關(guān)注

關(guān)注

8文章

5623瀏覽量

128281 -

PCIe

+關(guān)注

關(guān)注

16文章

1322瀏覽量

84656 -

串行通信接口

+關(guān)注

關(guān)注

0文章

17瀏覽量

9645

發(fā)布評(píng)論請(qǐng)先 登錄

信號(hào)完整性測(cè)試方法及使用儀器說明

信號(hào)完整性與電源完整性的仿真分析與設(shè)計(jì)

6678 SRIO鏈路信號(hào)完整性測(cè)試方法

如何對(duì)PCIe 3.0接收機(jī)物理層進(jìn)行測(cè)試?

詳解信號(hào)完整性與電源完整性

高速串行信號(hào)的信號(hào)完整性和物理層測(cè)量與分析

USB3.0的物理層接收端的測(cè)試方法 (完整版)

信號(hào)完整性分析

PCIe物理層的基本概念

信號(hào)完整性常用的三種測(cè)試方法

信號(hào)完整性實(shí)戰(zhàn):USB3.0

信號(hào)完整性測(cè)試概述

pcb信號(hào)完整性詳解

信號(hào)完整性設(shè)計(jì)測(cè)試入門

PCIe Tx/Rx 物理層信號(hào)完整性測(cè)試方法詳解

PCIe Tx/Rx 物理層信號(hào)完整性測(cè)試方法詳解

評(píng)論