本文翻譯轉(zhuǎn)載于:Cadence blog 作者:Sravasti Nair

基于 Cadence 30 年的行業(yè)知識和領(lǐng)先地位,全新人工智能定制設(shè)計(jì)解決方案 Virtuoso Studio 采用了多項(xiàng)創(chuàng)新功能和新的基礎(chǔ)架構(gòu),實(shí)現(xiàn)無與倫比的生產(chǎn)力,以及超越經(jīng)典設(shè)計(jì)界限的全新集成水平。在本文中,您將了解優(yōu)異的模擬設(shè)計(jì)工具如何變得更好,并助您解決挑戰(zhàn)性的設(shè)計(jì)問題。

半導(dǎo)體產(chǎn)業(yè)正在快速發(fā)展,對模擬/混合信號設(shè)計(jì)的需求也在迅速增加。然而,由于需要創(chuàng)建既符合設(shè)計(jì)規(guī)則又符合設(shè)計(jì)意圖的布局,設(shè)計(jì)流程的周轉(zhuǎn)時間很長。模擬布局創(chuàng)建基本需要依靠純?nèi)肆Γ驗(yàn)槠浜茈y針對用戶意圖實(shí)現(xiàn)自動化以滿足設(shè)計(jì)約束。此外,分組和匹配這些重要需求也非常耗時且難以實(shí)現(xiàn),對先進(jìn)工藝節(jié)點(diǎn)的追求迫使用戶需要從可制造性和可靠性的角度考慮許多復(fù)雜的要求。Virtuoso Studio 中的定制化自動布局布線(APR)解決方案能從整體上看待這些問題,為解決上述瓶頸提供了自動化的解決方案。

應(yīng)對先進(jìn)工藝技術(shù)

除了復(fù)雜情形的設(shè)計(jì)規(guī)則外,先進(jìn)節(jié)點(diǎn)還對模擬電路的傳統(tǒng)設(shè)計(jì)方法增加了額外限制。雖然模擬電路通常需要廣泛的器件尺寸以實(shí)現(xiàn)精度和性能,但由于密度和制造原因,現(xiàn)在的版圖布局需要更加均勻性。由于功能性密度的增加和器件的統(tǒng)一化,器件分組與陣列也變得更加復(fù)雜,滿足用戶對布局布線的預(yù)期也更具挑戰(zhàn)。

因此,我們需要新的工具和方法,來自動實(shí)現(xiàn)這些節(jié)點(diǎn)上模擬版圖的布局:處理工藝的復(fù)雜性和 LDE 效應(yīng),確保一致性,保留設(shè)計(jì)意圖,并允許用戶輕松和重復(fù)創(chuàng)建同類布局,且無需冗長的學(xué)習(xí)時間。

簡介:Virtuoso Studio Device-Level 自動布局布線(APR)解決方案

識別基于網(wǎng)格基礎(chǔ)架構(gòu)的結(jié)構(gòu)化布局方法,是處理工藝復(fù)雜性的關(guān)鍵。利用 Virtuoso Studio 可以將先進(jìn)工藝節(jié)點(diǎn)的挑戰(zhàn)轉(zhuǎn)化為機(jī)會,反過來有助于從自動化的角度彌合定制和數(shù)字設(shè)計(jì)解決方案之間的間隙。通過一個基于器件尺寸和工藝規(guī)則且支持不同寬度和間距網(wǎng)格的系統(tǒng),為自動布局、填充和布線引擎生成復(fù)雜的 DRCs 規(guī)則,同時遵守拓?fù)浼s束以及設(shè)計(jì)和電氣意圖。

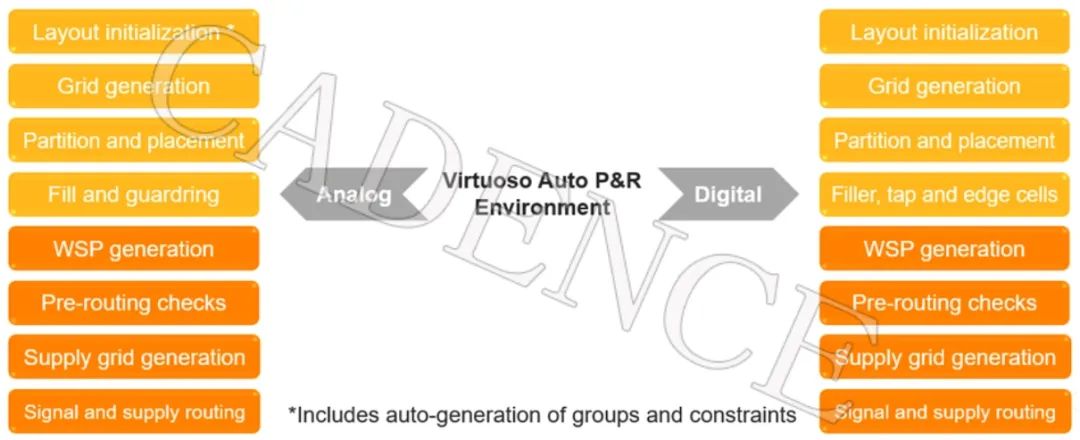

Virtuoso Studio 中的 Device APR 解決方案與全新的 Stdcell APR 解決方案互補(bǔ),該解決方案將數(shù)字引擎無縫集成到 Virtuoso Studio 中。在這些節(jié)點(diǎn)中,自動化模擬解決方案與數(shù)字解決方案沒有太大區(qū)別,用戶可以在 Virtuoso Studio 各項(xiàng)功能間無縫切換。

Virtuoso Studio Device APR 從功能性維度提供了這一領(lǐng)域最全面的解決方案,涵蓋了布局設(shè)計(jì)流程的各個方面,并實(shí)現(xiàn)了增強(qiáng)和自動化。具體包括:

1自動化節(jié)點(diǎn)和設(shè)計(jì)相關(guān)設(shè)置開箱即用的解決方案

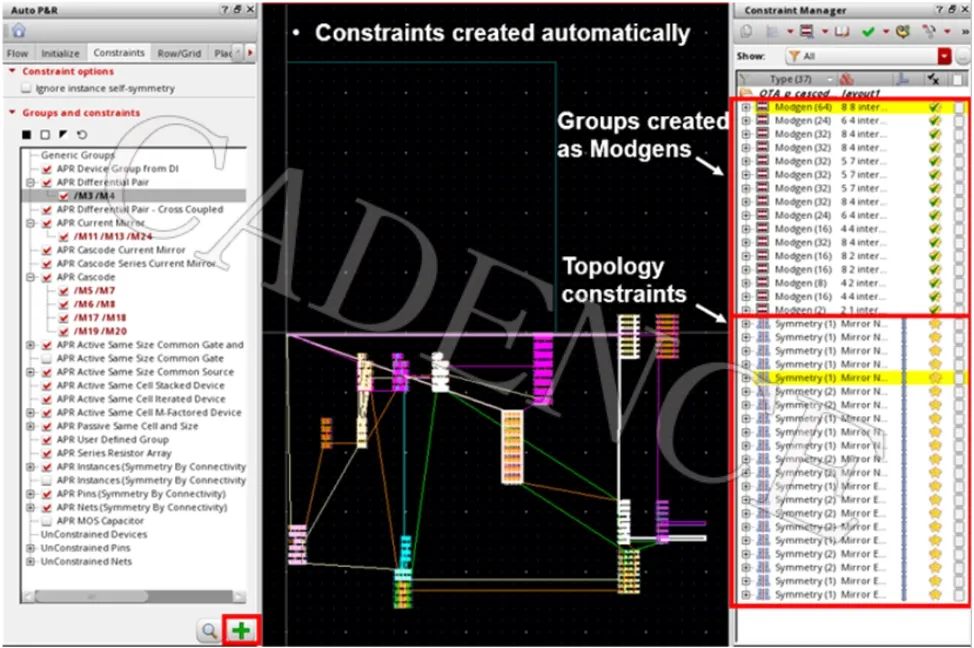

2根據(jù)模擬設(shè)計(jì)要求和用戶意圖自動分組和創(chuàng)建約束

3布局圖驅(qū)動的群組自動重塑,保留用戶意圖

4自動生成布局布線網(wǎng)格,并將設(shè)計(jì)中的非統(tǒng)一器件考慮在內(nèi)

5基于網(wǎng)格的分組和約束驅(qū)動的自動布局,包括填充和隔離插入

6自動生成基于網(wǎng)格的電源輸送網(wǎng)絡(luò)

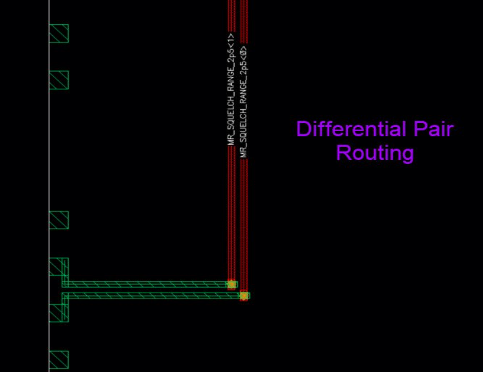

7具備高性能和 QoR,基于網(wǎng)格的約束驅(qū)動自動布線

8支持特殊布線拓?fù)湟詫?shí)現(xiàn)電氣正確性

9允許用戶通過輔助編輯進(jìn)行干預(yù),幫助設(shè)計(jì)師實(shí)現(xiàn)更優(yōu)的模擬布局質(zhì)量

10通過統(tǒng)一的基于任務(wù)的 GUI 改善和簡化用戶體驗(yàn)

11完整的布線環(huán)境,采用類似電子表格的界面,管理和檢查所有布線約束、計(jì)劃、運(yùn)行和分析布線

總結(jié)

Virtuoso Studio 的 Device Level 自動化布線布局解決方案是模擬布局設(shè)計(jì)的轉(zhuǎn)折點(diǎn)。該解決方案可以逐步引導(dǎo)工程師完成對各項(xiàng)功能的探索,最終實(shí)現(xiàn)完整的自動化布局。為了易于使用,此用戶界面經(jīng)過專門設(shè)計(jì),為布局和電路設(shè)計(jì)師創(chuàng)造最佳體驗(yàn),而自動化引擎也能支持先進(jìn)工藝節(jié)點(diǎn)的大量器件。憑借諸如智能器件分組、精確的器件模態(tài)控制、分組和匹配驅(qū)動的自動布局、自動填充和隔離、自動生成電網(wǎng)以及自動布線控制以滿足電氣需求等功能,Virtuoso Studio 器件級 APR 為模擬布局設(shè)計(jì)提供了最全面的自動化解決方案。模擬布局自動化的未來已至,Virtuoso Studio 則是通往它的途徑。

關(guān)于 Cadence

Cadence 是電子系統(tǒng)設(shè)計(jì)領(lǐng)域的關(guān)鍵領(lǐng)導(dǎo)者,擁有超過 30 年的計(jì)算軟件專業(yè)積累。基于公司的智能系統(tǒng)設(shè)計(jì)戰(zhàn)略,Cadence 致力于提供軟件、硬件和 IP 產(chǎn)品,助力電子設(shè)計(jì)概念成為現(xiàn)實(shí)。Cadence 的客戶遍布全球,皆為最具創(chuàng)新能力的企業(yè),他們向超大規(guī)模計(jì)算、5G 通訊、汽車、移動設(shè)備、航空、消費(fèi)電子、工業(yè)和醫(yī)療等最具活力的應(yīng)用市場交付從芯片、電路板到完整系統(tǒng)的卓越電子產(chǎn)品。Cadence 已連續(xù)九年名列美國財(cái)富雜志評選的 100 家最適合工作的公司。

審核編輯:湯梓紅

-

模擬電路

+關(guān)注

關(guān)注

125文章

1588瀏覽量

103611 -

Cadence

+關(guān)注

關(guān)注

65文章

961瀏覽量

143722 -

Studio

+關(guān)注

關(guān)注

2文章

203瀏覽量

29475 -

布局布線

+關(guān)注

關(guān)注

1文章

89瀏覽量

15322 -

Virtuoso

+關(guān)注

關(guān)注

4文章

18瀏覽量

25317

原文標(biāo)題:Virtuoso Studio:Device-Level 自動布局布線已成現(xiàn)實(shí)!

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

求protel軟件PCB圖自動布局自動布線相關(guān)經(jīng)驗(yàn)分享

PCB布局布線的相關(guān)基本原理和設(shè)計(jì)技巧

對GDSII database進(jìn)行g(shù)ate-level寄生參

PCB布局布線技巧100問

有關(guān)PCB布局布線方面疑難問題,都全了!

PCB布局布線的100個基本問題解答

Device Studio亮點(diǎn)功能介紹

Virtuoso布局套件中自定義IC布局設(shè)計(jì)的路由技術(shù)

PCB布局布線技巧104問

快來測測你對 Virtuoso Studio 了解多少?(第二期)

Cadence基于AI的Cadence Virtuoso Studio設(shè)計(jì)工具獲得認(rèn)證

關(guān)于PCB布局布線技巧的104的問題

Virtuoso Studio:寄生參數(shù)提取設(shè)計(jì)

104條關(guān)于PCB布局布線的小技巧

Virtuoso Studio Device-Level自動布局布線解決方案

Virtuoso Studio Device-Level自動布局布線解決方案

評論