MIL(Model In The Loop)模型在環(huán)仿真測試用于在實際系統(tǒng)搭建完成之前進(jìn)行模型測試,使用VeriStand搭建MIL測試環(huán)境,可以在不需要硬件資源的情況下測試控制模型。

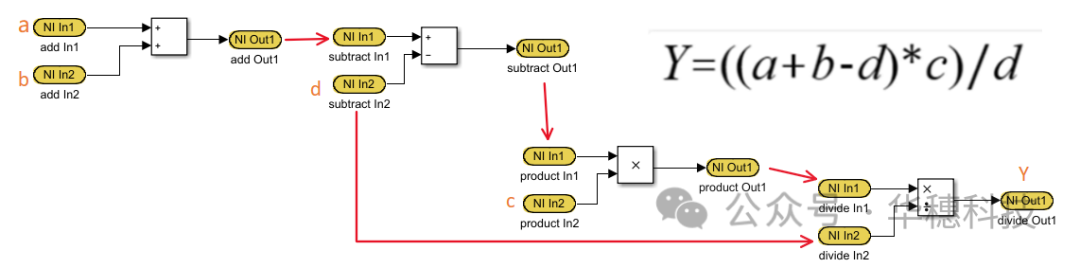

下面小編將帶領(lǐng)大家完成一個簡單的練習(xí),在VeriStand中調(diào)用Matlab模型,實現(xiàn)公式Y(jié)=((A+B-D)*C)/D的運算,在此過程中熟悉VeriStand項目的開發(fā)流程,為學(xué)習(xí)搭建HIL(Hardware In The Loop)測試系統(tǒng)打下基礎(chǔ)。

本文教程:

VeriStand創(chuàng)建MIL測試環(huán)境

一、軟件環(huán)境

VeriStand2020

MATLABR2019a

GCC編譯器(安裝教程參考:教程 | VeriStand硬件在環(huán)仿真測試第一章)

若想使用其他版本的軟件,可以參考NI官方提供的軟件兼容性列表

二、創(chuàng)建Simulink模型

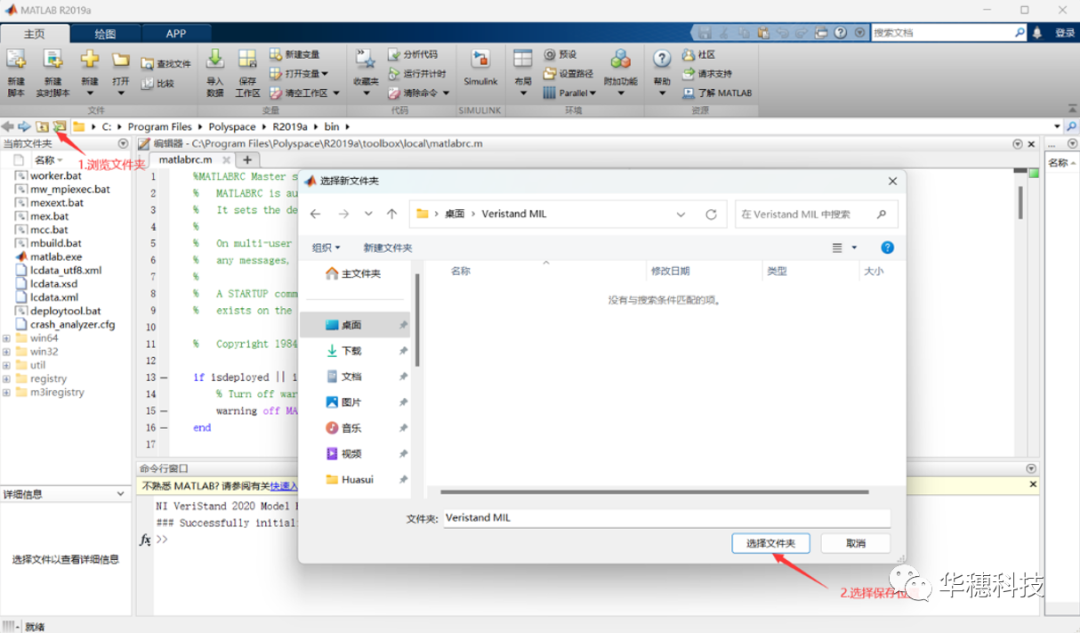

打開MATLAB 2019a,先修改預(yù)覽文件夾,選擇文件保存位置;若未修改文件瀏覽文件夾,編譯Simulink文件時可能會遇到報錯。

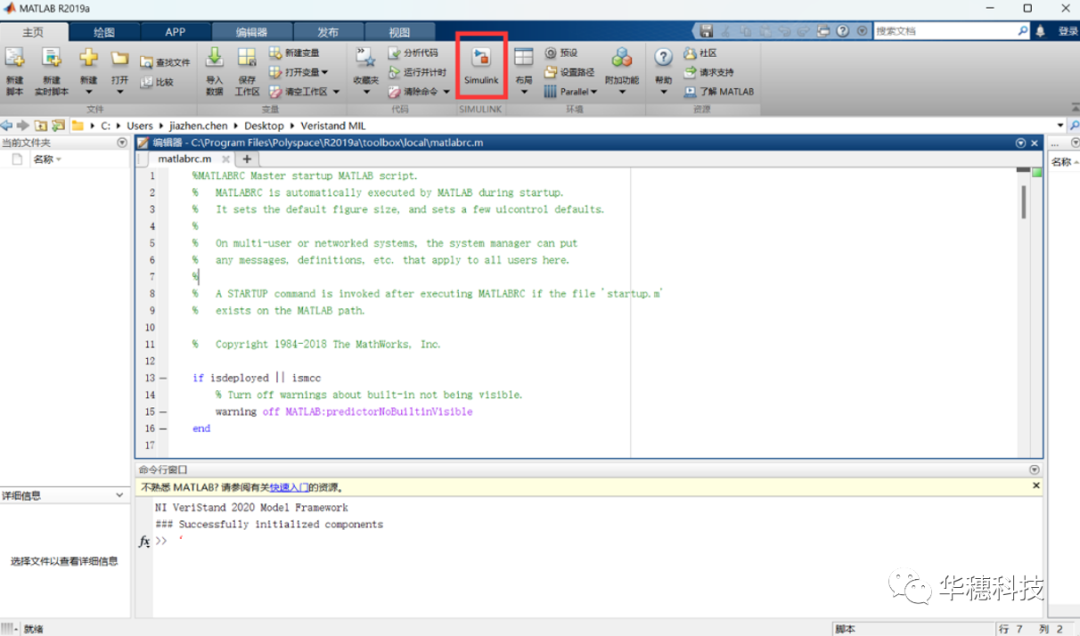

啟動Simulink。

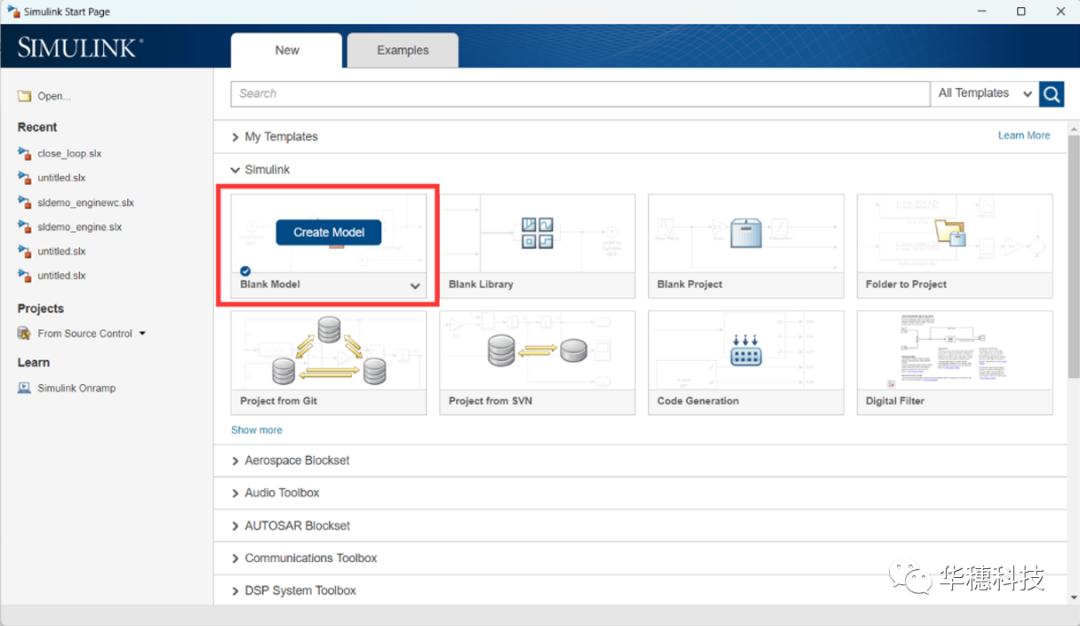

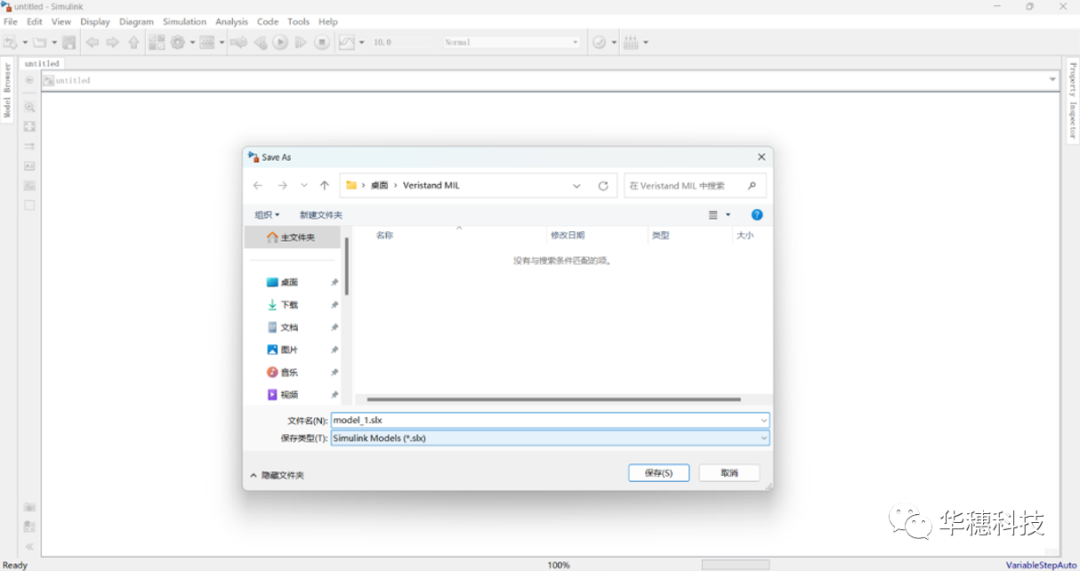

創(chuàng)建空白Simulink模型,將模型保存到文件夾,文件名不能包含非法字符(小編實測不允許出現(xiàn)空格,建議用下劃線分隔字符)。

1. 構(gòu)建加法器模型

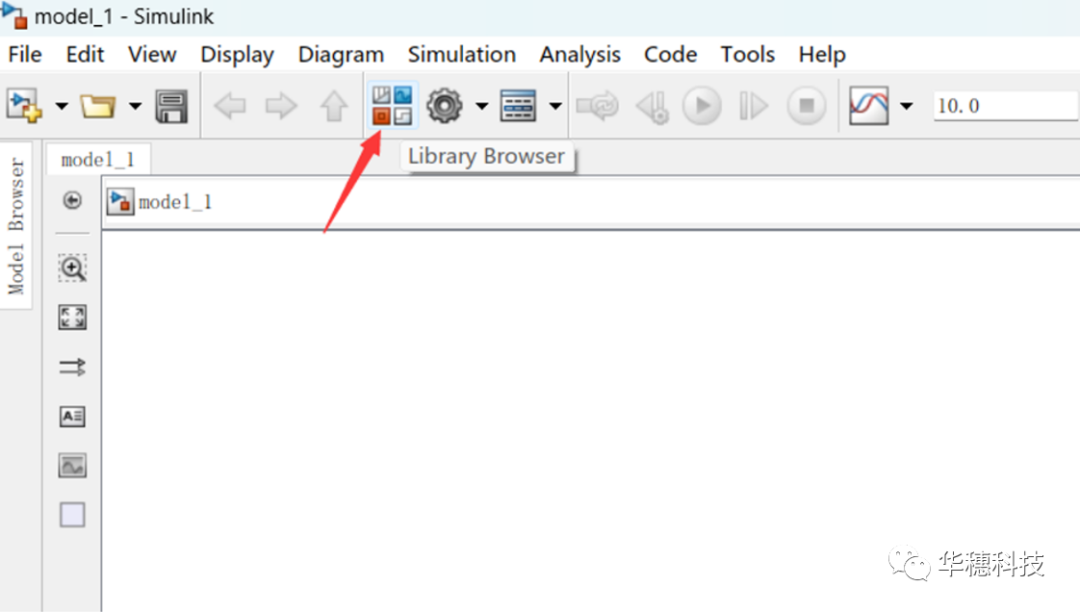

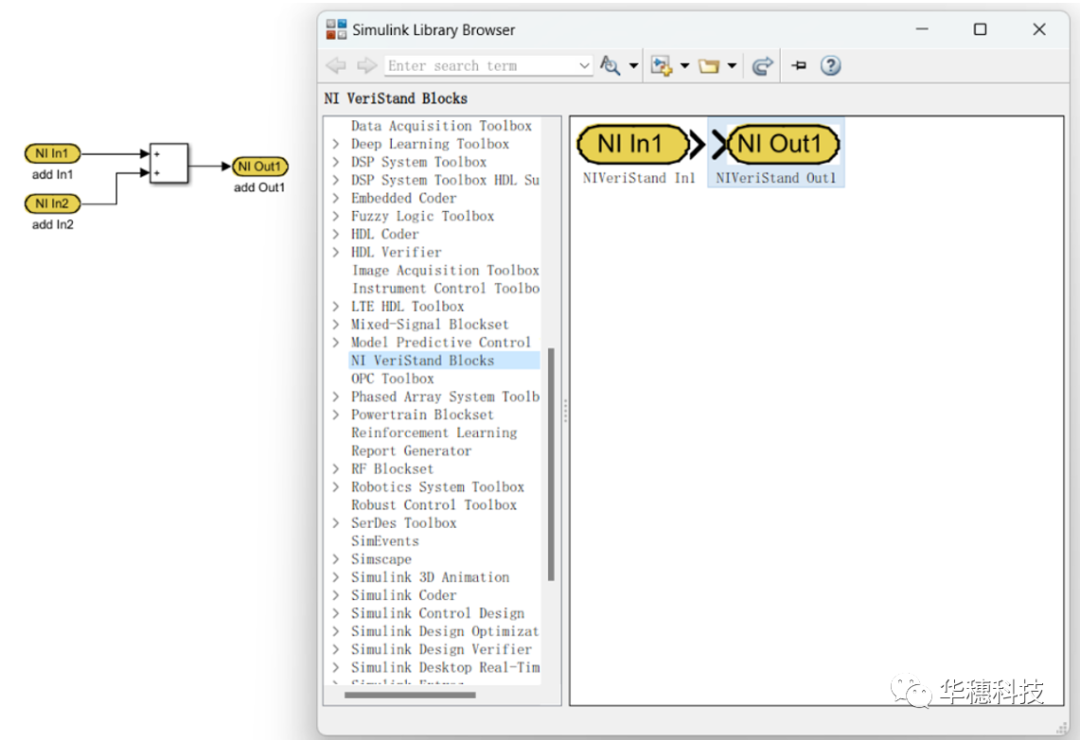

輸入輸出接口選擇NI VeriStand Blocks里的兩個控件,拖到面板上進(jìn)行重命名并連線,小編建議命名邏輯清晰一些,方便后續(xù)編輯端口映射。

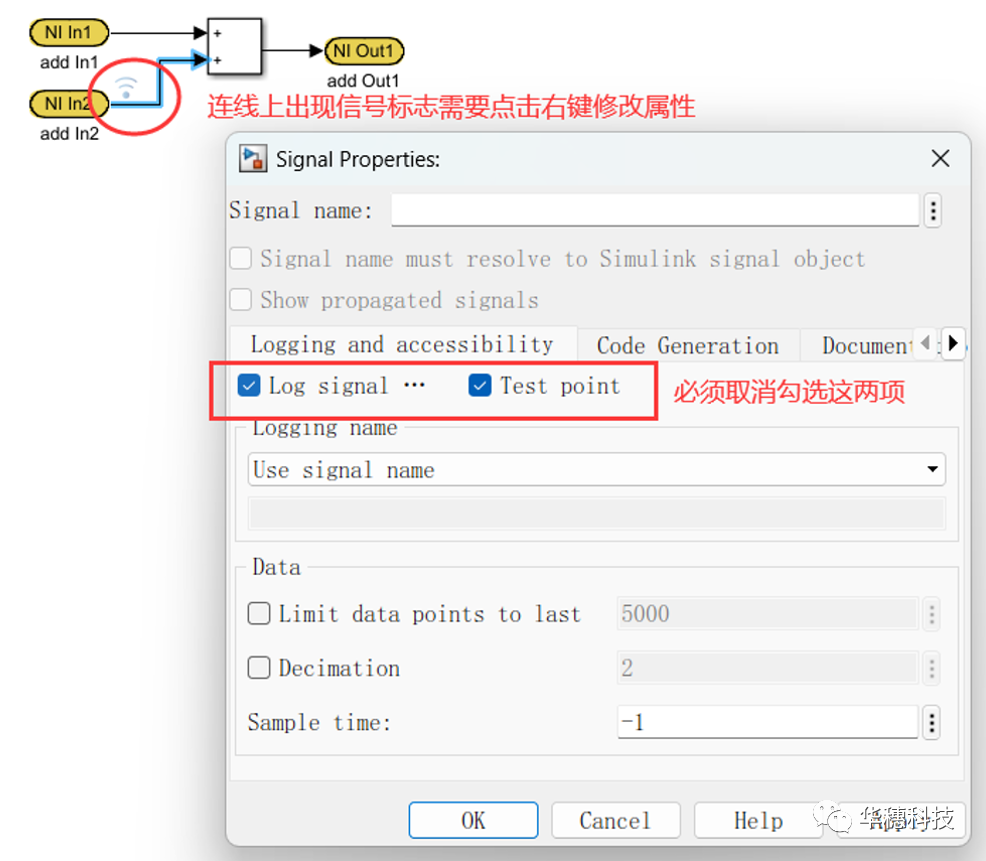

若調(diào)用了其他Simulink模型,注意模塊之間連線的屬性,不能勾選LogSignal和Test Point。

2.配置模型參數(shù)

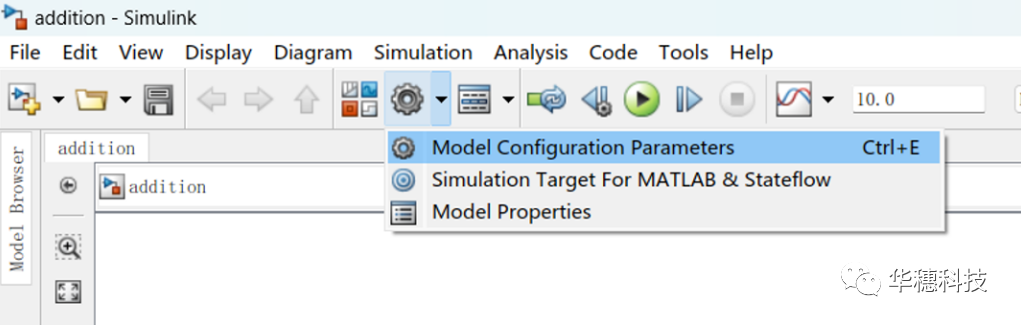

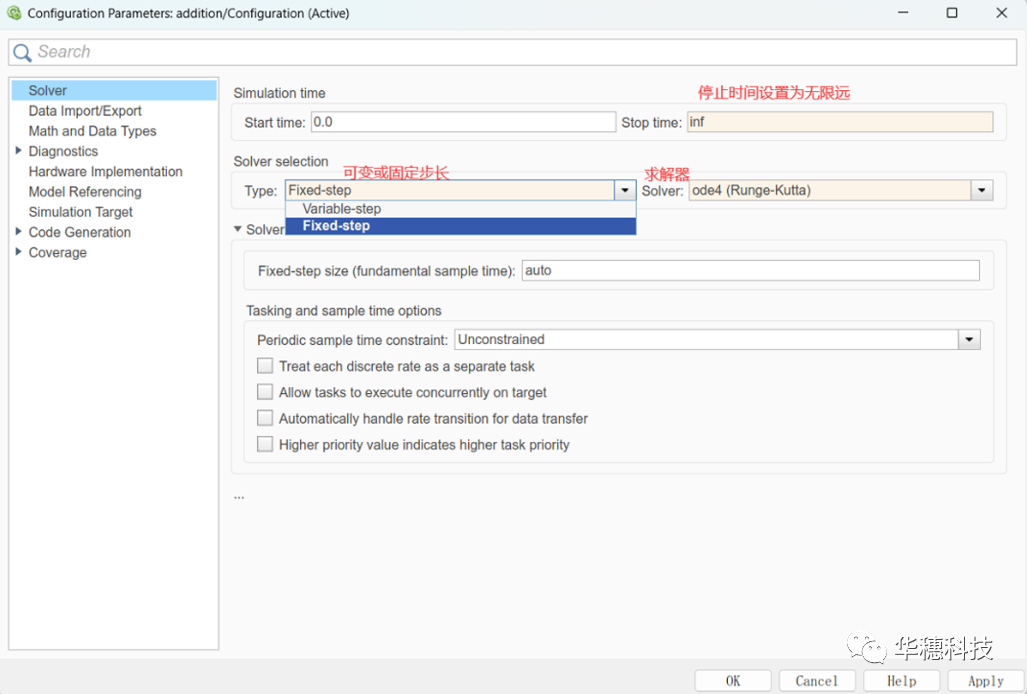

點擊Model Configuration Parameters或按快捷鍵Ctrl+E,設(shè)置模型參數(shù)。

步長越短模型模擬越精確,也相應(yīng)地帶來了更高的計算量;求解器用于計算常微分方程,根據(jù)模型情況選擇合適的求解器可以提高執(zhí)行效率。

Window模式下選擇可變步長或固定步長都可以,推薦使用Auto自動選擇求解器;模型部署在實時系統(tǒng)時只能選擇固定步長,求解器推薦使用ODE4。

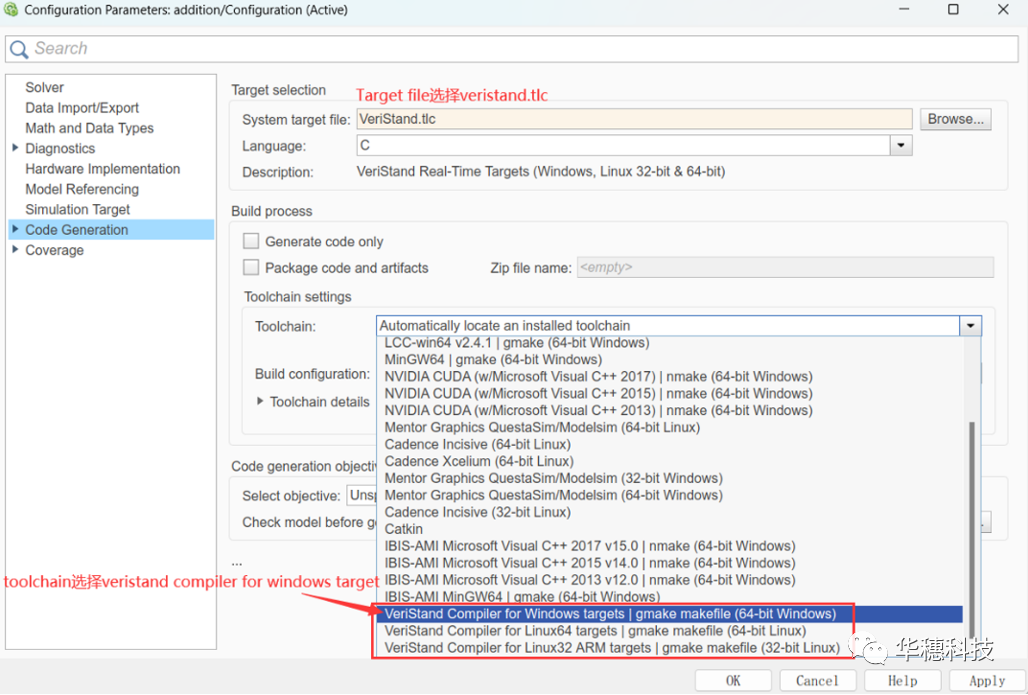

如上圖中所示,在Code Generation中設(shè)置TargetFile和Toolchain參數(shù),完成參數(shù)配置后點擊OK。

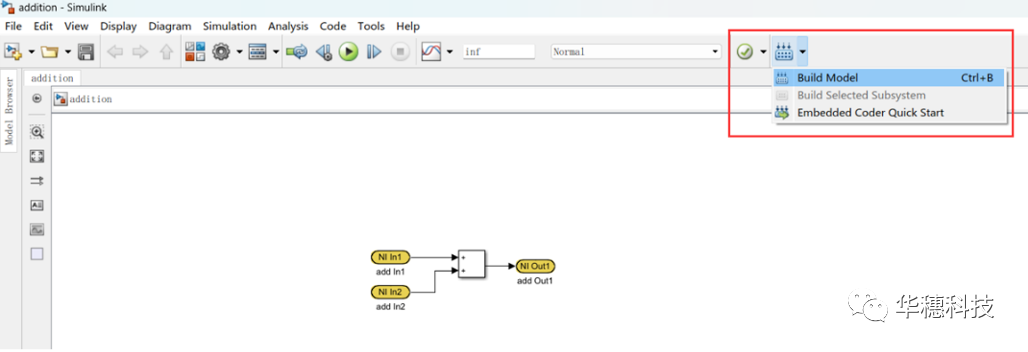

3.模型編譯

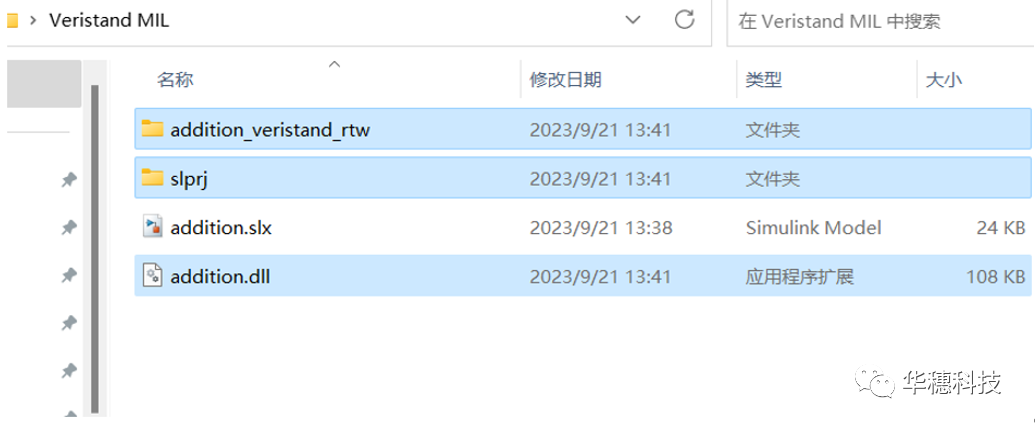

點擊Build Model或按快捷鍵Ctrl+B對模型進(jìn)行編譯,在預(yù)覽文件夾可以看到生成的.Dll文件,該文件可供VeriStand調(diào)用;其余的減法、乘法、除法模型制作方式同理。

二、在VeriStand中調(diào)用模型:

1. 加載模型

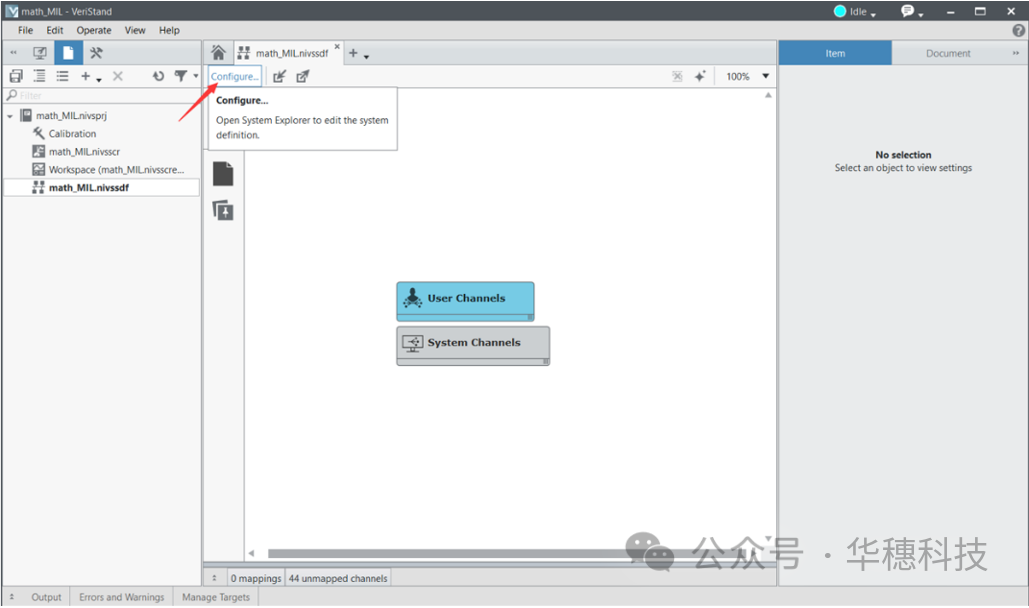

新建VeriStand工程,點擊Configure進(jìn)入設(shè)置。

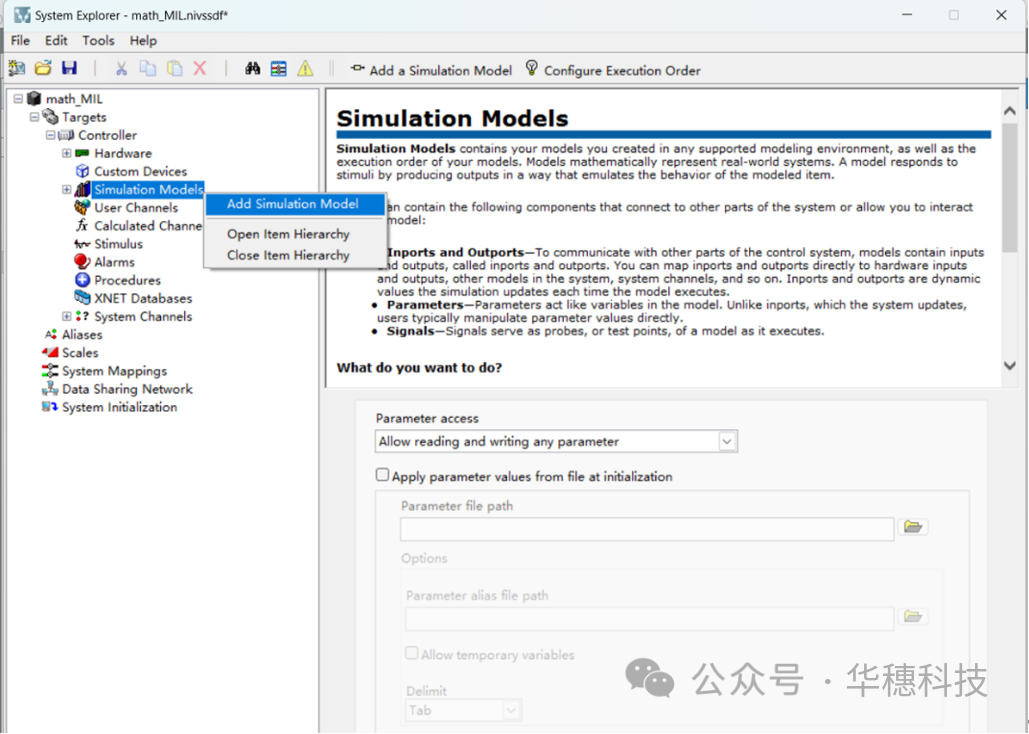

右鍵Simulation Models選擇Add Simulation添加模型。

點擊文件夾圖標(biāo),找到并選擇先前Simulink模型生成的.Dll文件,點擊確定。

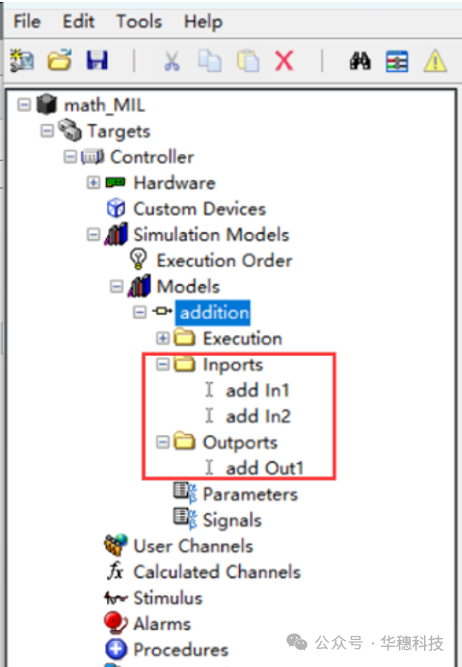

在模型下方可以看到其輸入輸出接口,將剩余需要加載的模型按照同樣的方法加載進(jìn)來,下一步開始配置端口映射。

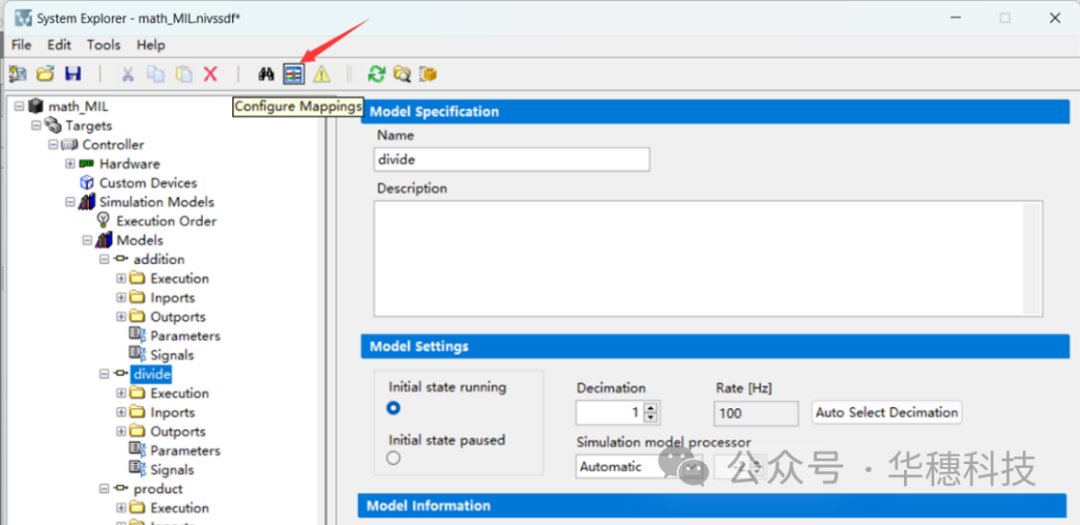

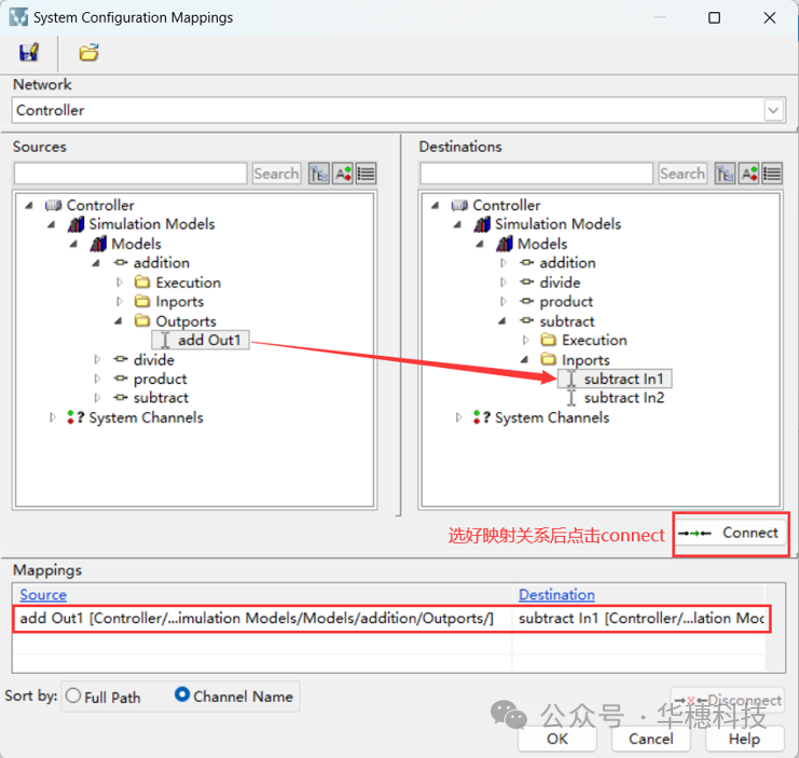

2. 配置端口映射

點擊Configure Mappings編輯映射關(guān)系。

根據(jù)公式的計算順序,其余的接口映射,依圖中箭頭所代表的關(guān)系設(shè)置。

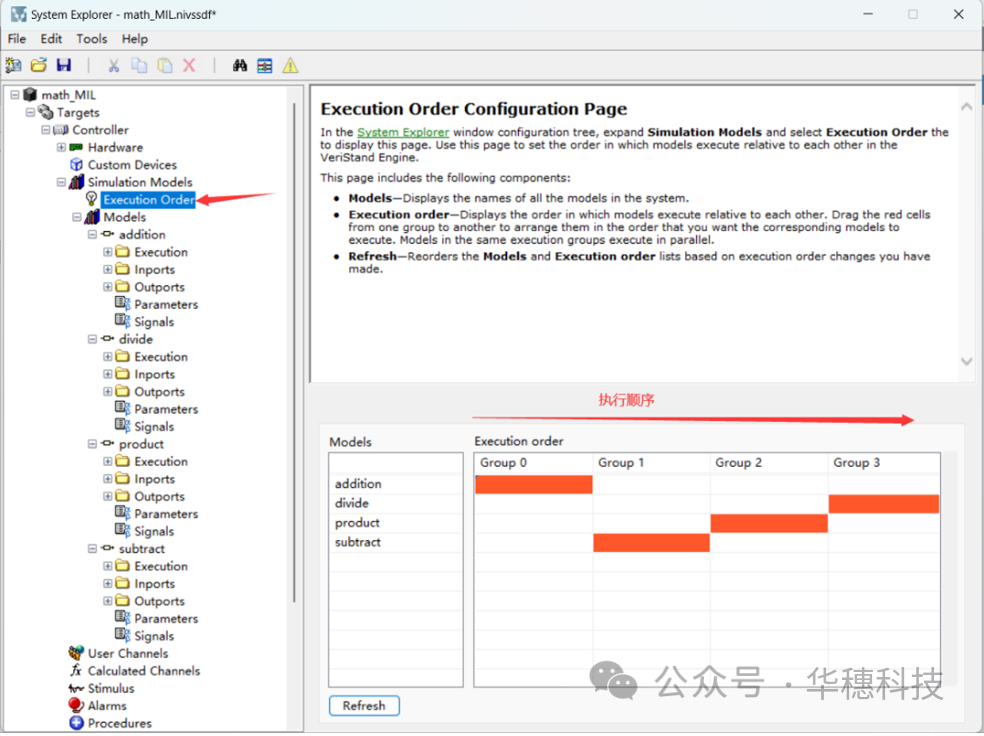

3.設(shè)置模型執(zhí)行順序

點擊Execution Order,在模型欄拖動橙色條紋規(guī)定模型執(zhí)行順序,Group 0~3會依次執(zhí)行,橙色條紋對應(yīng)的模型即是本組需要執(zhí)行的模型,上圖為依據(jù)計算公式設(shè)置的執(zhí)行順序,完成后保存返回主界面。

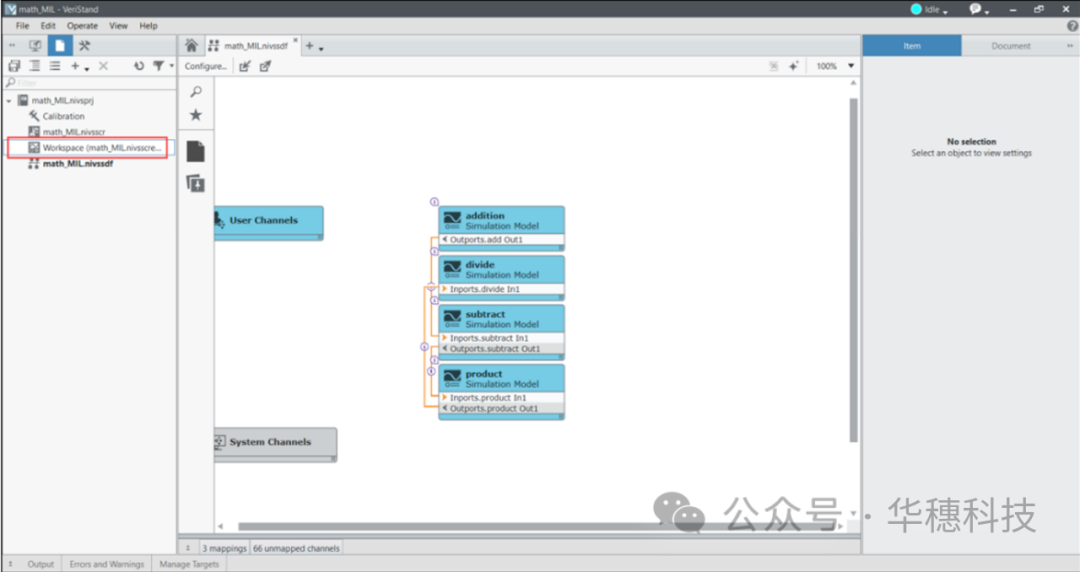

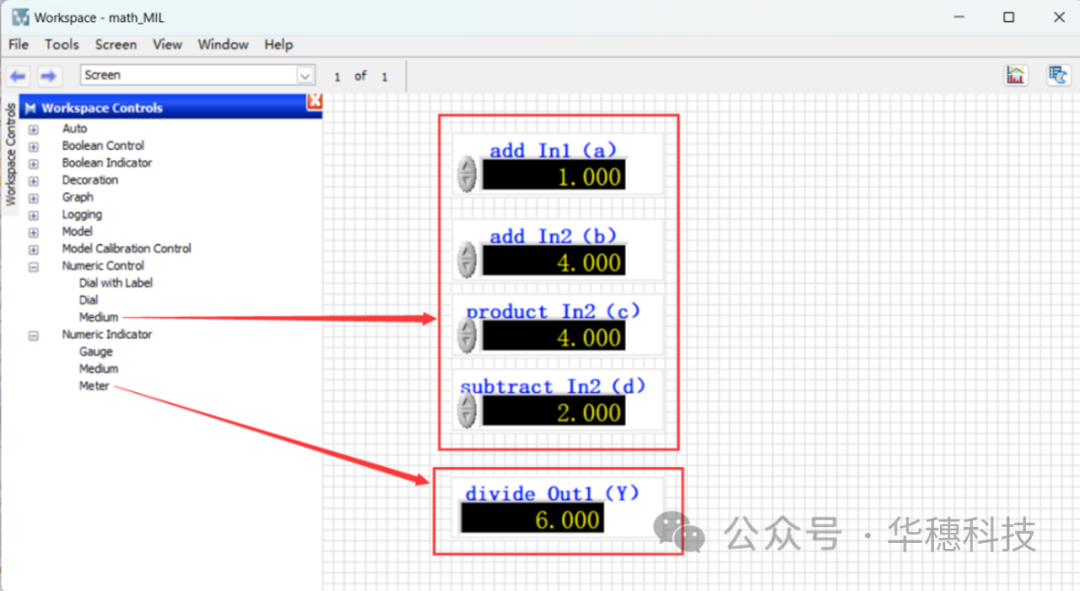

4. 編輯Workspace面板

雙擊Workspace。

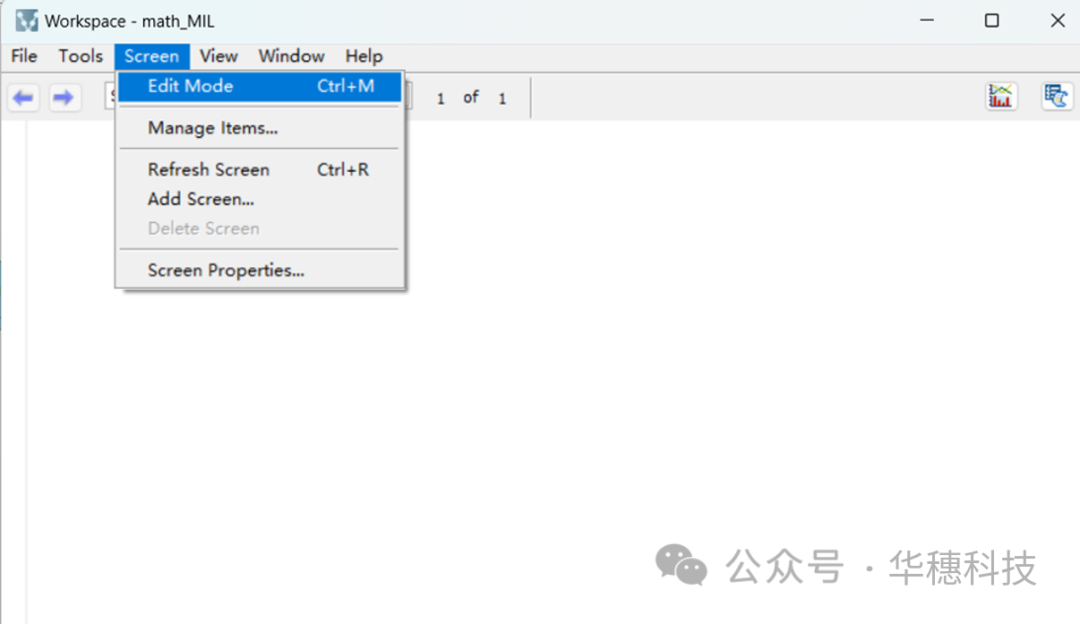

選擇Screen中的Edit Mode。

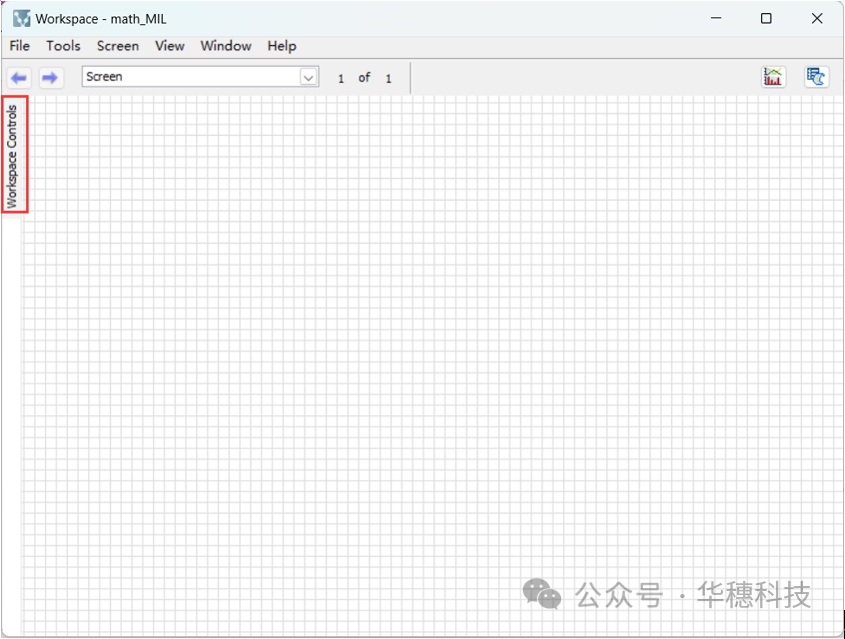

點擊Workspace Controls。

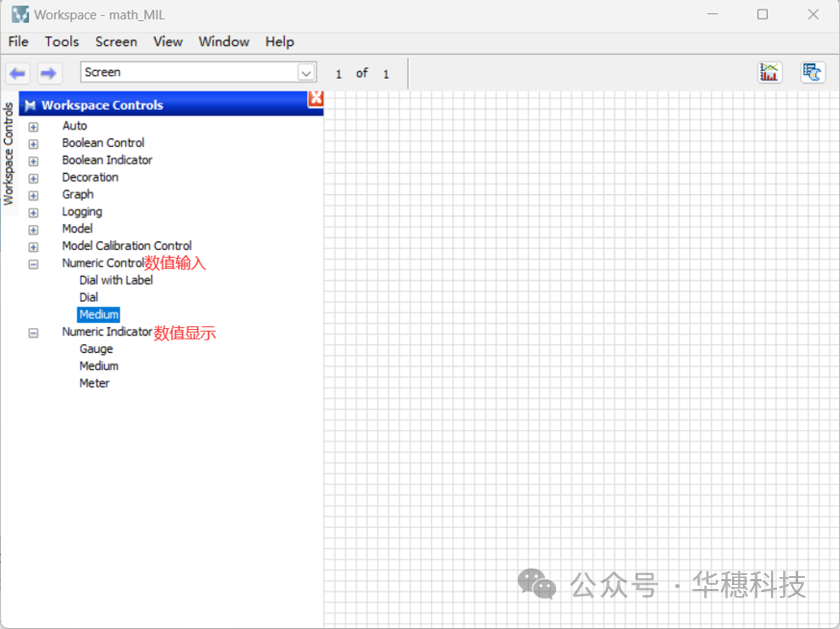

在菜單中選中Numeric Control下的Medium,拖到網(wǎng)格區(qū)域。

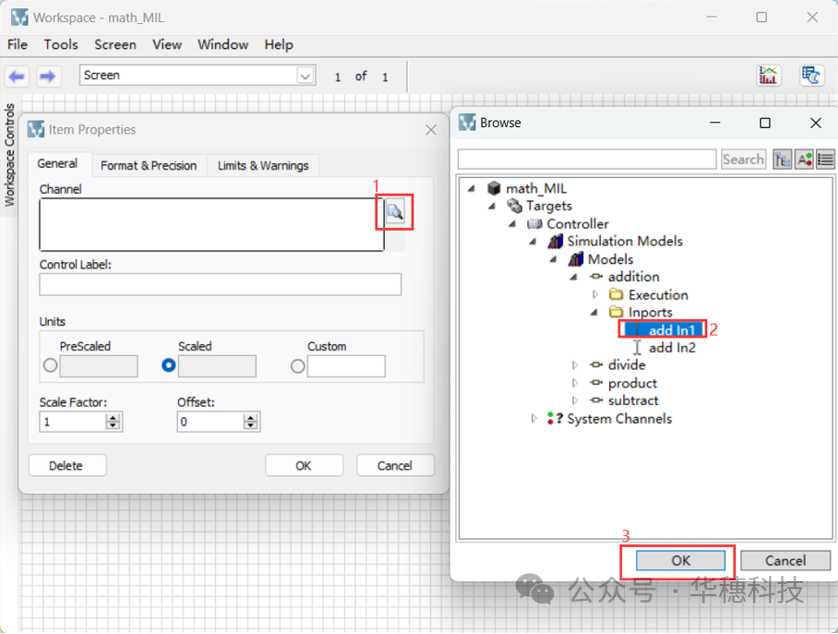

在彈出的屬性配置界面中選擇映射到的端口。

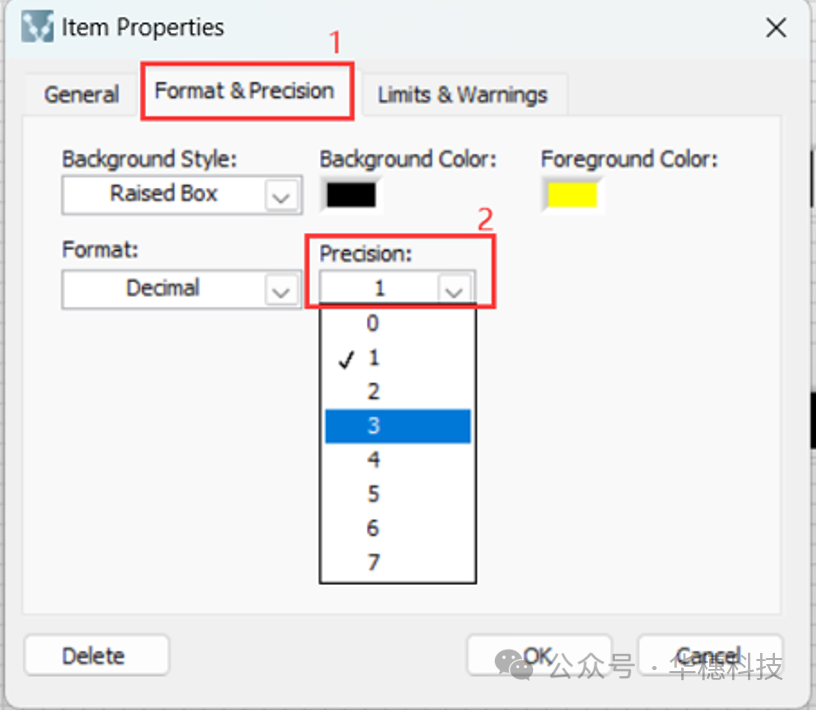

在第二欄的Format & Precision屬性中設(shè)置數(shù)值顯示精度。

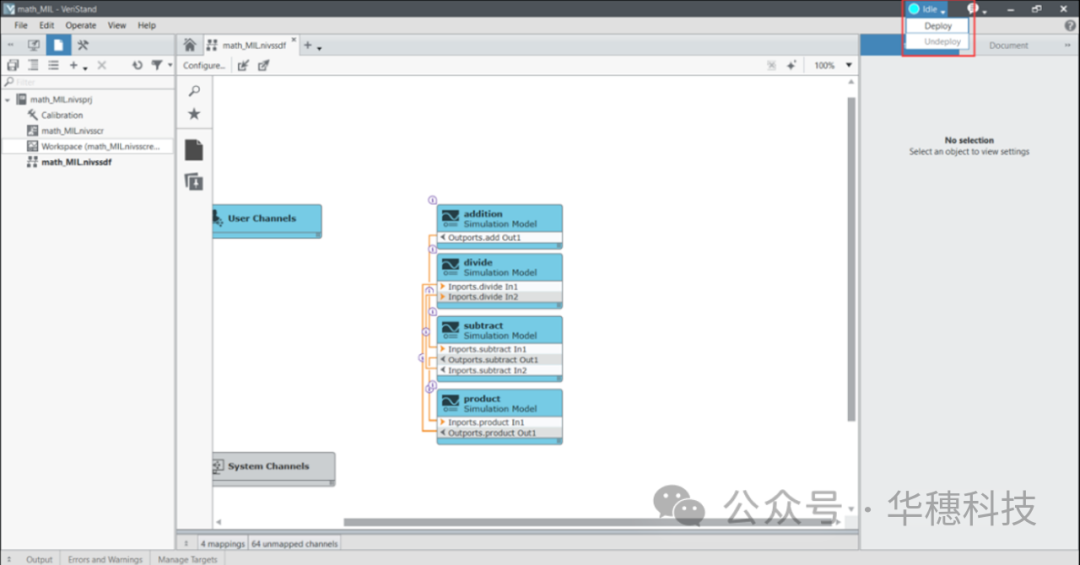

5. 運行部署

選擇右上角的Idle中的Deploy部署執(zhí)行程序。

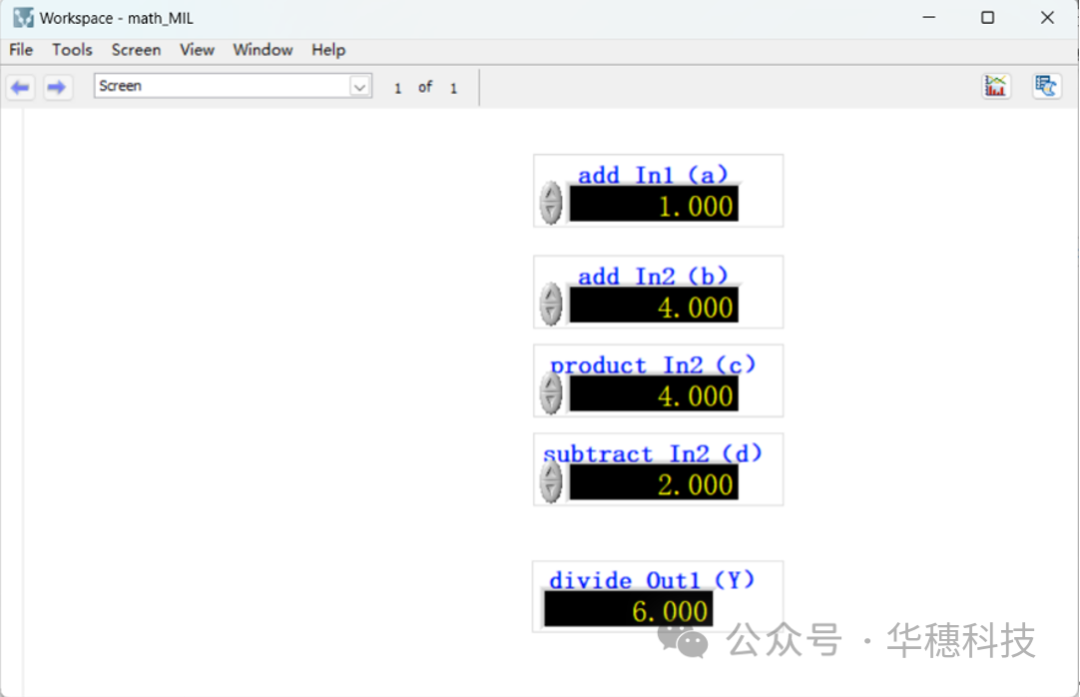

打開Workspace查看執(zhí)行結(jié)果,符合公式Y(jié)=((A+B-D)*C)/D。

至此,我們成功搭建并驗證了一個簡單的MIL測試系統(tǒng),萬變不離其宗,對于更復(fù)雜的MIL、HIL測試系統(tǒng),區(qū)別是調(diào)用了更加復(fù)雜的模型、配合更復(fù)雜的硬件連接方式,其總體上的搭建過程與本文所描述的流程相似。

三、內(nèi)容總結(jié)

1.創(chuàng)建Simulink模型,生成.DLL文件。

2.在VeriStand中調(diào)用Simulink模型。

3.配置端口映射。

4.編輯Workspace面板。

審核編輯:湯梓紅

-

matlab

+關(guān)注

關(guān)注

188文章

2994瀏覽量

233053 -

模型

+關(guān)注

關(guān)注

1文章

3477瀏覽量

49921 -

編譯器

+關(guān)注

關(guān)注

1文章

1653瀏覽量

49815 -

VeriStand

+關(guān)注

關(guān)注

7文章

13瀏覽量

22658 -

mil

+關(guān)注

關(guān)注

0文章

12瀏覽量

8103

原文標(biāo)題:知識分享 | VeriStand創(chuàng)建MIL測試環(huán)境

文章出處:【微信號:華穗科技,微信公眾號:華穗科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

NI發(fā)布最新版本VeriStand,用于機械測試應(yīng)用與嵌入式軟件驗證

如何快速搭建一個MQTT協(xié)議的測試環(huán)境

VeriStand的執(zhí)行機制

NI VeriStand 2016 與matlab 2016 搭配的問題

matlab 2016a 與 NI VeriStand 2016 代碼生成問題

基于配置的軟件環(huán)境NI VeriStand使用手冊

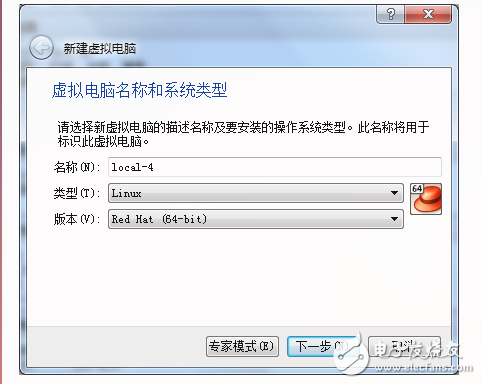

利用Vmware來搭建單機多系統(tǒng)的測試環(huán)境

在NI VeriStand環(huán)境中進(jìn)行FPGA相關(guān)配置

WEB測試環(huán)境搭建和測試方法

在linux環(huán)境下搭建java web測試環(huán)境

測試環(huán)境的搭建和維護_軟硬件測試環(huán)境

搭建測試環(huán)境常用linux命令_linux下web測試環(huán)境的搭建

使用VeriStand搭建MIL測試環(huán)境

使用VeriStand搭建MIL測試環(huán)境

評論