大家都知道在設計階段解決問題的成本是最低,同樣道理在原理圖設計階段做好關(guān)鍵信號、敏感電路的防護設計可以達到事半功倍的效果,本期將與大家探討在原理圖的設計階段如何考慮靜電防護設計。

一、防護對象識別方法

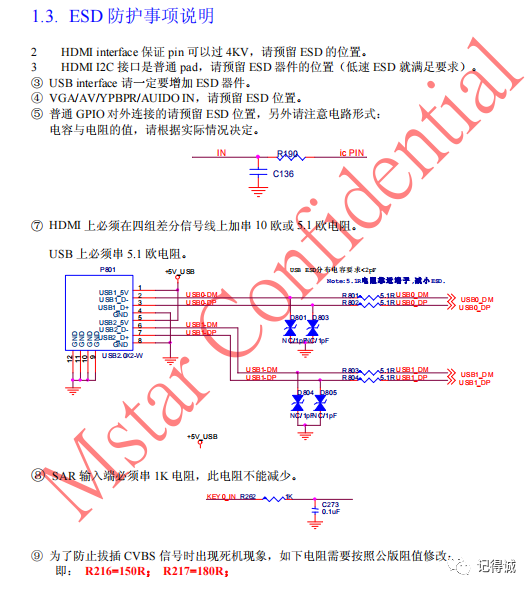

1.1 根據(jù)應用手冊識別防護對象

對于芯片級的防護對象識別應根據(jù)原廠提供的應用手冊,結(jié)合以往的使用經(jīng)驗來識別敏感信號,或者說防護對象。

圖1:原廠應用手冊(AP)防護設計說明

1.2 根據(jù)端口信號類型識別防護對象

根據(jù)靜電放電測試標準要求可知,外部端口根據(jù)其結(jié)構(gòu)類型分別需要做不同的靜電放電測試。所以針對外部互連端口在原理圖設計階段需要重點關(guān)注靜電放電防護設計,具體端口類型如下:

圖2:外部塑膠按鍵、屏蔽縫隙空氣放電測試

圖3:金屬端子外殼測試接觸放電、塑膠端子測試空氣放電

1.3 根據(jù)信號類型識別防護對象

除外部互連端口信號需要重點考慮靜電放電防護,系統(tǒng)內(nèi)部互連端口也需要重點考慮靜電放電防護之外,板內(nèi)的小信號、關(guān)鍵信號、敏感信號也需要重點考慮靜電放電防護。

板內(nèi)需要重點關(guān)注的防護信號如:復位信號、通訊信號、串行Flash通訊信號、敏感GPIO信號、模擬信號、高速差分信號等。

二、電路級ESD防護設計

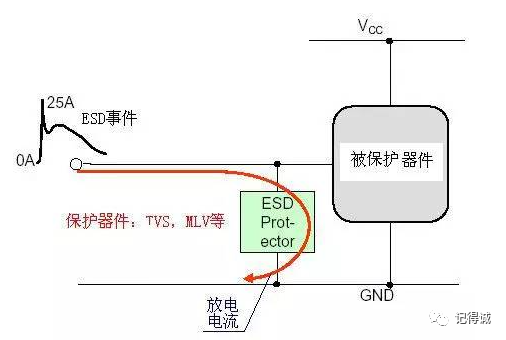

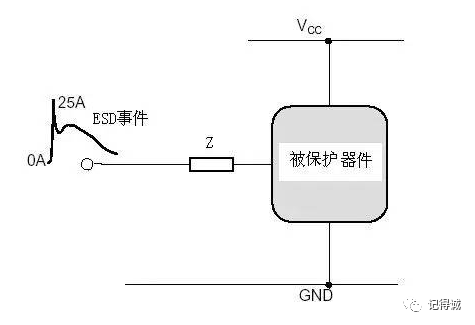

當集成電路IC經(jīng)受靜電放電(ESD)時,放電回路電阻通常很小,無法限制放電電流,造成高達數(shù)十安培的瞬間放電尖峰電流,流入相應的IC管腳,瞬間大電流會嚴重損傷IC,甚至造成IC內(nèi)部燒毀。

當集成電路IC經(jīng)受靜電放電(ESD)時的尖峰脈沖電壓時,會引起IC內(nèi)部死鎖;當脈沖電壓超過內(nèi)部CMOS器件的擊穿電壓時,則會擊穿內(nèi)部半導體器件,導致IC內(nèi)部的集成電路損壞,失效。

根據(jù)集成電路損壞的機理,電路級ESD防護設計主要從靜電尖峰脈沖電壓鉗位、靜電電流限制、以及電壓鉗位與電流限制的雙重保護設計方面進行控制。

2.1 靜電尖峰脈沖電壓鉗位設計(ESD器件并聯(lián))

圖4:并聯(lián)ESD器件進行尖峰電壓鉗位

一是利用齊納二極管反向擊穿特性進行ESD敏感器件保護。二是利用多層金屬氧化物具有非線性電壓-電流(阻抗曲線)關(guān)系進行ESD敏感器件保護。三是利用氣體放電管擊穿氣體時的損耗來進行ESD敏感器件保護。

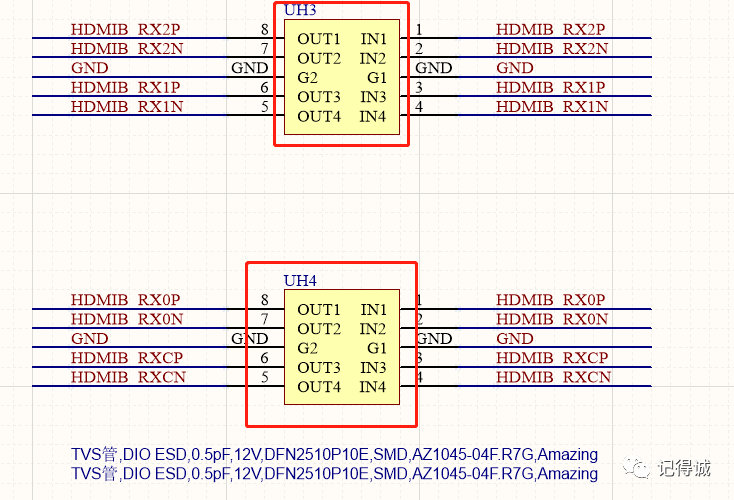

2.1.1 高速差分信號ESD防護設計

在這里插入圖片描述

圖5:高速差分信號并聯(lián)ESD器件防護

設計要點說明:

我們知道高速差分信號需要使用低容值ESD器件,低容值ESD意味著PN結(jié)面積小,則相應的通流量差,在差分信號線上串聯(lián)低阻值的電阻,可以有效減小靜電電流對芯片的沖擊,TVS管器件對脈沖型騷擾電壓起到很好的抑制效果,二者結(jié)合可以對后端芯片進行有效的ESD防護。

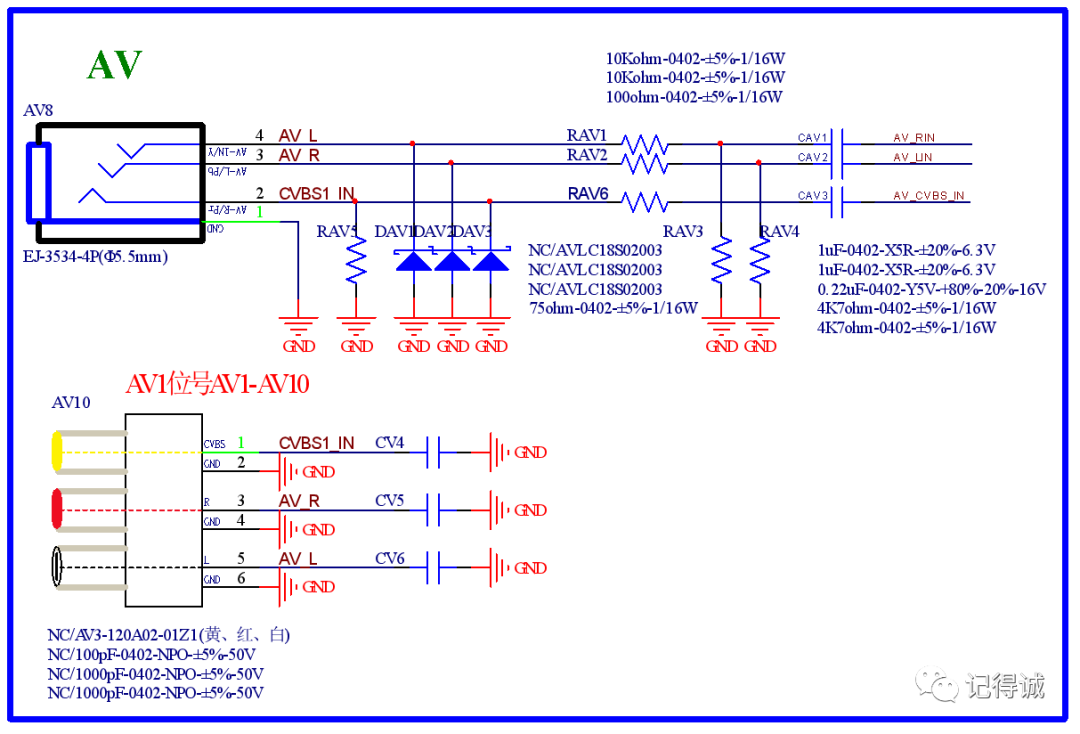

2.1.2 低速信號ESD防護設計

圖6:模擬音視頻信號并聯(lián)ESD器件防護

設計要點說明:

低速信號ESD保護器件可選擇的范圍較寬,低電壓的ESD器件應用較特殊,相對來說成本較高,低速信號還是建議在信號線上串聯(lián)電阻,可以低成本解決ESD保護問題。

2.2 靜電放電電流限制設計(串聯(lián)阻抗)

一般通過串聯(lián)電阻或者磁珠來限制ESD放電電流,達到靜電防護的目的。如GPIO信號、ADC信號、音視頻信號、串口、I2C信號等。電阻的效果通常會優(yōu)于磁珠的效果,磁珠通常在100MHz頻率以上阻抗較大,而電阻阻抗基本恒定。

圖7:串聯(lián)電阻限制靜電放電電流

2.3 增加濾波電路

2.3.1 RC濾波在ESD防護設計中的應用

根據(jù)IEC61000-4-2標準給出的電流波形可知其高次諧波非常豐富,如果用濾波器濾掉主要的能量也能達到靜電防護的目的。對于低頻信號:如GPIO信號、ADC信號、音頻輸入信號可以用RC濾波電路,濾除靜電放電干擾。

審核編輯:湯梓紅

-

原理圖

+關(guān)注

關(guān)注

1322文章

6404瀏覽量

239037 -

ESD

+關(guān)注

關(guān)注

49文章

2265瀏覽量

175105 -

靜電放電

+關(guān)注

關(guān)注

4文章

300瀏覽量

45077 -

靜電防護

+關(guān)注

關(guān)注

11文章

207瀏覽量

47826

原文標題:搞定ESD(八):靜電放電之原理圖設計

文章出處:【微信號:記得誠,微信公眾號:記得誠】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

混合動力汽車在前期設計階段整改案例

原理圖設計階段如何考慮靜電防護設計

原理圖設計階段如何考慮靜電防護設計

評論