我們知道,一個處在系統(tǒng)中的組件,總會有一些指標(biāo)是需要滿足的。自然,pipelinedADC中的OP也要滿足一定的增益和帶寬指標(biāo)。

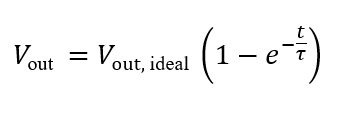

PipelinedADC中的OP主要分布在S/H電路和MDAC電路中。單就運放指標(biāo)計算而言,無論是S/H還是MDAC,都可以作為同一類問題處理——即運放閉環(huán)系統(tǒng)的性能問題。運放有限增益導(dǎo)致即使時間足夠長,輸出仍然存在一個直流誤差;運放的有限帶寬導(dǎo)致在限定的時間窗口期內(nèi),輸出并不能實現(xiàn)100%精度的建立。要使誤差在系統(tǒng)允許范圍內(nèi),運放的增益和帶寬必須要達(dá)到一定限值以上。

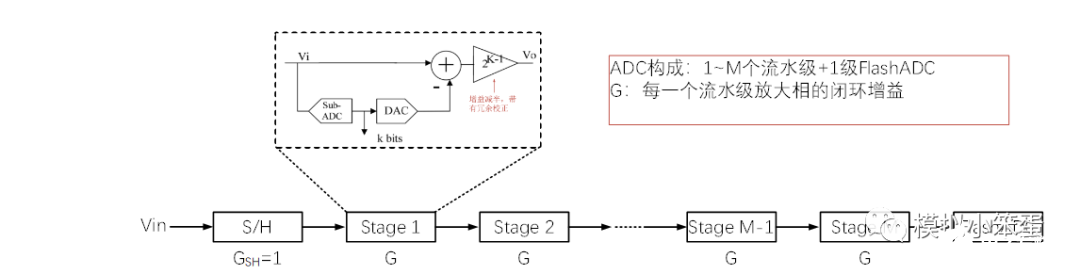

圖:ADC架構(gòu)圖

在計算之前,我們有必要先了解一下ADC的架構(gòu),這對理解計算過程是有幫助的。我們看上圖,它由S/H電路、1~M個流水級和一個FlashADC組成。圖中G表示每個流水極放大相時的閉環(huán)增益。對于1.5bit結(jié)構(gòu),G=2。

OP增益指標(biāo)的計算

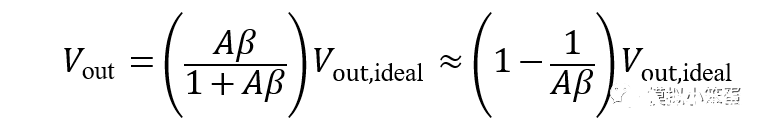

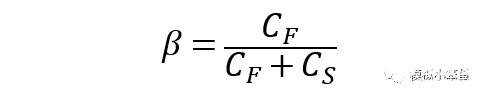

假設(shè)運放的增益為A,且暫不考慮寄生電容Cp的影響, MDAC閉環(huán)時的反饋系數(shù)為β,由于運放帶來的有限開環(huán)增益誤差, 可以證明輸出電壓表達(dá)式為:

公式(1)

公式(2)

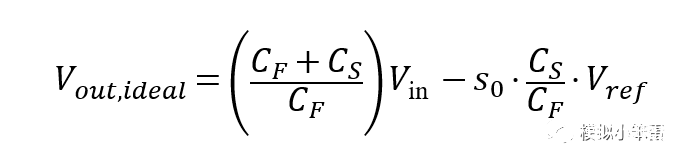

其中, 是Vout,ideal是理想的輸出電壓如下(具體參考:如何推導(dǎo)一個1.5位MDAC的輸出函數(shù)?):

公式(3)

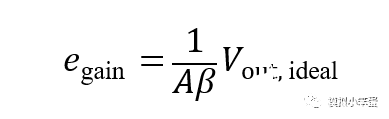

因此, 增益誤差為:

公式(4)

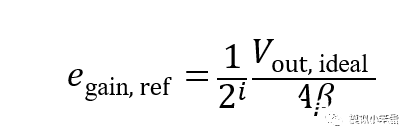

接下來我們將這個誤差量折算到ADC的最前端,折算的方法是將該誤差除以前向增益。根據(jù)前文的ADC架構(gòu)圖,設(shè)當(dāng)前級為第i個流水級(i=1~M),折算到輸入端的誤差為:

公式(5)

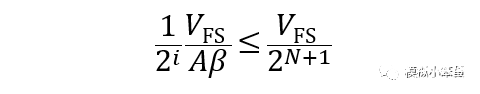

從MDAC傳輸曲線可看出,其最大輸出擺幅是(3/4)*VFS(具體參考:如何推導(dǎo)一個1.5位MDAC的輸出函數(shù)?)。計算時我們按VFS進(jìn)行,則上述最大增益誤差應(yīng)該小于整體精度的1/2。則有:

公式(6)

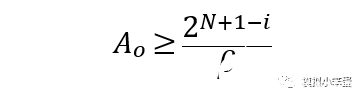

推出:

公式(7)

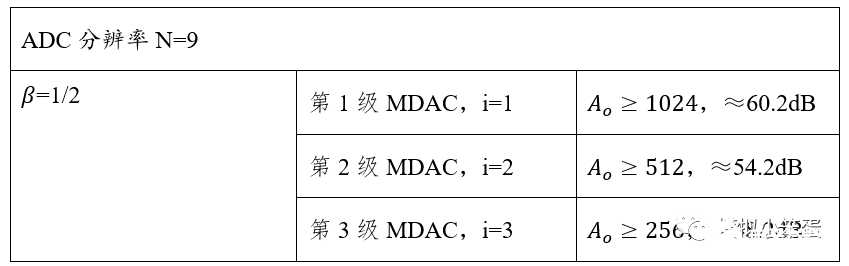

根據(jù)上式,假設(shè)一個9bit的ADC,我們嘗試計算,結(jié)果如下表所示:

注意:

β值受Cp的影響,實際會小于1/2。因此考慮Cp影響后,因此實際要比表中的計算值更大。可以證明,只需要用代替上述公式中的β就可以得到考慮寄生后的表達(dá)式。

公式7也適用于S/H電路中OP的計算,但要取β=1,i=0。

審核編輯:黃飛

-

運放電路

+關(guān)注

關(guān)注

38文章

365瀏覽量

35320 -

模擬IC

+關(guān)注

關(guān)注

8文章

173瀏覽量

29796 -

adc

+關(guān)注

關(guān)注

99文章

6635瀏覽量

548184 -

寄生電容

+關(guān)注

關(guān)注

1文章

297瀏覽量

19649

發(fā)布評論請先 登錄

多傳感器航跡融合的評價指標(biāo)及計算方法

高頻開關(guān)電源系統(tǒng)可靠性指標(biāo)MTBF的計算方法

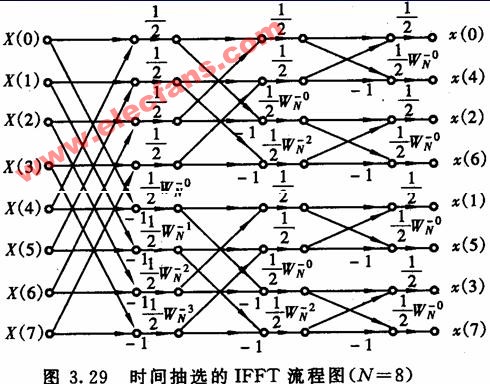

IFFT的計算方法

EMC計算方法和EMC仿真(1) 計算方法簡介

模擬IC設(shè)計之OP帶寬的計算方法

模擬IC設(shè)計之OP的指標(biāo)計算方法

模擬IC設(shè)計之OP的指標(biāo)計算方法

評論