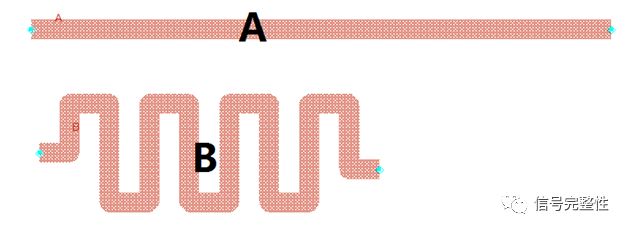

在文章的開頭,給大家提一個問題:相同物理長度的兩段傳輸線如下圖所示,一段直線A,一段繞線B,A和B哪一段的延時會更大?

隨著高速電路的發展,電路的設計在朝著高速高密度的方向發展。速度和密度高了的話,各種信號完整性、EMI的問題就出來。這也就出現了各種各樣的設計要求規則,比如阻抗穩定性、同組同層、等長設計等等。今天咱們就來討論一個由等長而引發的一個設計問題,即繞線設計,

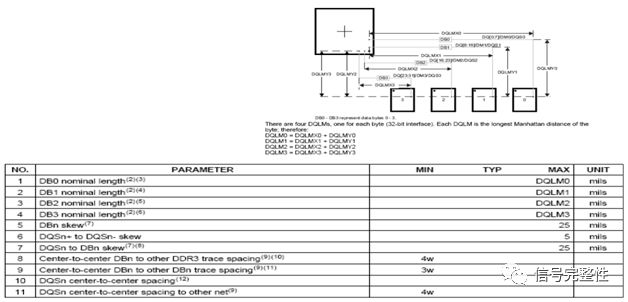

在設計中,特別是DDR3/4/5這類的設計,總會有很多的信號線存在,每一組的數據或者地址控制命令信號線都有一定的等長要求,如下所示為某芯片手冊的要求:

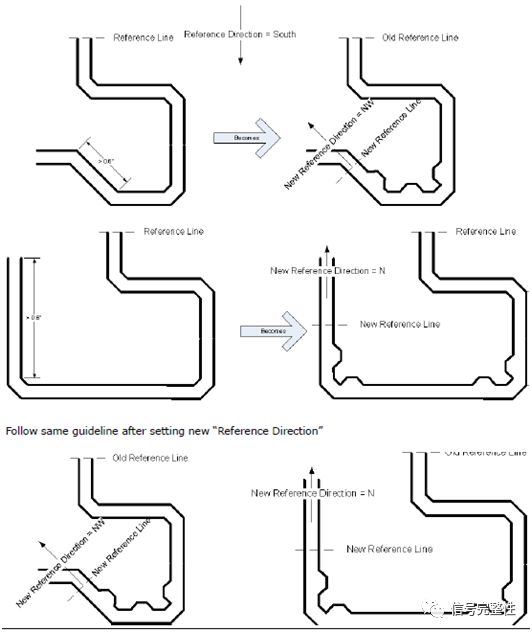

在設計時,當達不到要求時,工程師首先想到的都是繞線,然后還出現了非常多的繞線方式。如下圖所示(此圖來自Intel PDG):

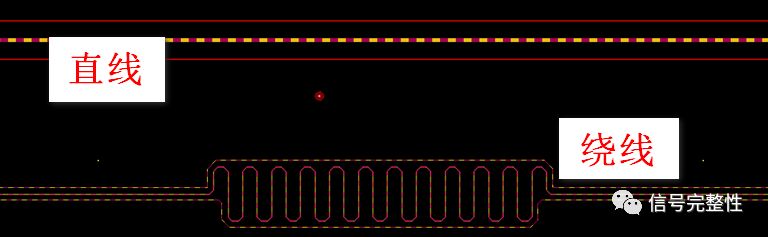

本文就和大家聊一聊平時咱們繞線的方式到底存在一些什么問題?為了完成這個問題的研究,特意做了一個測試板,設計了研究對象為10inch的傳輸線,一段做參考為直線(上),一段為繞線(下),如下圖所示:

一般,大家通常都會認為,這樣已經算等長了,而且是完全等長。但是,通過測量其傳輸特性,測量的結果如下圖所示,我們可以看到,其差異還是不小,相差了12.73ps(紅色圓圈),而且繞線比直線傳輸的更快。

這12.7ps換算成物理長度,約為80mil。80mil的長度應該是讓有經驗的工程師嚇一跳,畢竟平時硬件工程師說:給我做好等長,誤差在2mil的時候都會跳起腳來大罵。

當然,我們這里做實驗設計的為10inch,通常很多布線都沒這么長,但是也有一些布線確實非常長的。

但是,不管怎么樣,這個實驗都告訴了我們,物理等長,不等于實際設計就等長了。這也是為什么,近年來,業界一些廠商都提倡時序等長的原因。

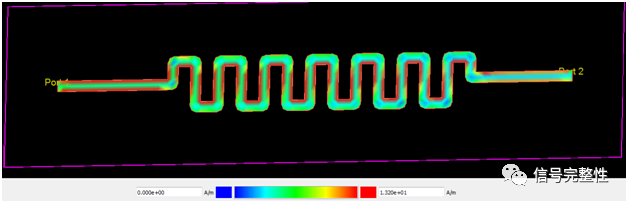

這是為什么呢?原因就在于繞線之后,由于趨膚效應和電磁場效應,信號都是在表面傳遞。為了解釋此現象,在ADS中設計了一段繞線,進行了電磁(EM)仿真,結果如下圖所示:

從上圖中,我們可以看到,在繞線的地方,都是在相對比較緊耦合處場電流密度比較大,呈紅色,在上方(與傳輸線平行)以及傳輸線的中心處,電流密度比較小,呈淺色,這就說明信號靠近邊沿處傳遞,這樣就導致了信號傳遞的“更加快速”,所用的時間更少(本來可以給大家放一張動態圖的,但是沒能做好,有機會的時候,再給大家show一下)。

而直線的仿真結果如下圖所示(長度太長,所以只截取一部分):

通過以上的分析即可說明,相同的物理長度,繞線的一段延時更小,這樣,我們就能回答前面提出來的問題了,顯然是A的延時更大(在上文中也說了繞線更快)。

那么問題又來了,工程師在設計時遇到不“等長”的時候,如何做好設計呢?

第一,把物理等長的觀念改為等時,及不管繞線還是直線,需要的是傳輸延時是一樣的。有的PCB設計工具是可以使用時間來表示物理長度的;

第二,有時序關系的信號線,在設計時做到同進同出同設計,盡量減少繞線;

第三,如果某一段傳輸線確實要繞線,繞線的形狀大一點,波與波的距離大一點,或者繞的比直線更長一點,至于繞多長,我也不知道,還是請工程師進行下仿真吧(這也就是為什么要進行后仿真了)。

當然,好的、方便的設計方法非常多,此為拋磚引玉,希望大家把好的方法也分享出來,有興趣的也可以進一步的與我交流探討。

編者注:這種繞線的研究,并不是說每一種總線設計都需要這樣做,對于一些低速信號、對時序沒有特別要求的信號或者對EMI沒有特殊要求的項目,工程師可以不用考慮。以上內容僅供參考。

審核編輯:劉清

-

DDR3

+關注

關注

2文章

282瀏覽量

42927 -

emi

+關注

關注

53文章

3700瀏覽量

130266 -

信號完整性

+關注

關注

68文章

1432瀏覽量

96426 -

高速電路

+關注

關注

8文章

163瀏覽量

24527 -

ADS仿真

+關注

關注

1文章

71瀏覽量

10778

原文標題:90%的工程師都沒意識到的高速電路設計問題:等長繞線的影響

文章出處:【微信號:SI_PI_EMC,微信公眾號:信號完整性】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

從焊接角度聊一聊,設計PCB的5個建議

來聊一聊Altium中Fill,Polygon Pour,Plane的區別和用法

聊一聊stm32的低功耗調試

聊一下GS的波形

聊一聊關于顯示器選購的一些事

聊一聊平時咱們等長繞線的方式到底存在一些什么問題?

聊一聊平時咱們等長繞線的方式到底存在一些什么問題?

評論