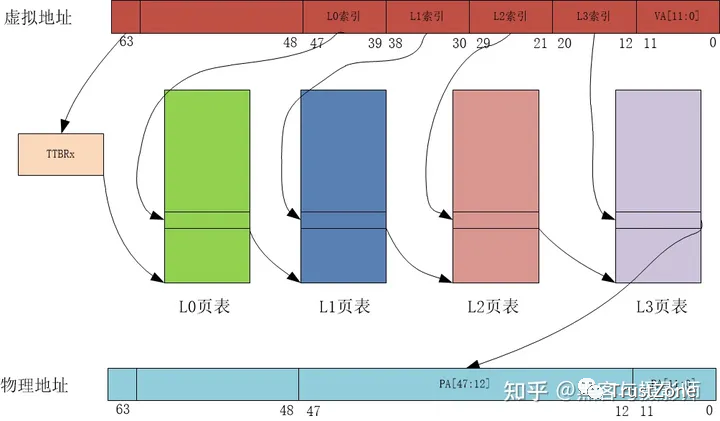

物理頁面大小一級地址總線寬度不同,頁表的級數也不同。以AArch64運行狀態,4KB大小物理頁面,48位地址寬度為例,頁表映射的查詢過程如圖:

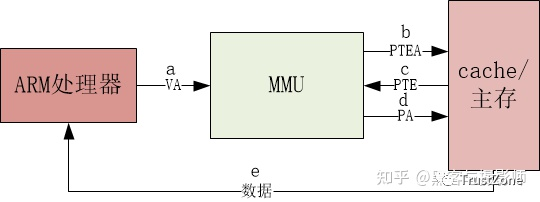

對于多任務操作系統,每個用戶進程都擁有獨立的進程地址空間,也有相應的頁表負責虛擬地址到物理地址之間的轉換。MMU查詢的過程中,用戶進程的一級頁表的基址存放在TTBR0。操作系統的內核空間公用一塊地址空間,MMU查詢的過程中,內核空間的一級頁表基址存放在TTBR1。當TLB未命中時,處理器查詢頁表的過程如下:

? 處理器根據虛擬地址第63位,來選擇使用TTBR0或者TTBR1。當VA[63]為0時,選擇TTBR0,TTBR中存放著L0頁表的基址。

? 處理器以VA[47:39]作為L0的索引,在L0頁表中查找頁表項,L0頁表有512個頁表項。

?L0頁表的頁表項中存放著L1頁表的物理基址。處理器以VA[38:30]作為L1索引,在L1頁表中找到相應的頁表項,L1頁表中有512個頁表項。

?L1頁表的頁表項中存放著L2頁表的物理基址。處理器以VA[29:21]作為L2索引,在L2頁表中找到相應的頁表項,L2頁表中有512個頁表項。

?L2頁表的頁表項中存放著L3頁表的物理基址。處理器以VA[20:12]作為L1索引,在L3頁表中找到相應的頁表項,L3頁表中有512個頁表項。

?L3頁表的頁表項里,存放著4KB頁面的物理基址,然后加上VA[11:0],這樣就構成了物理地址,至此處理器完成了一次虛擬地址到物理地址的查詢與翻譯的工作。

-

處理器

+關注

關注

68文章

19799瀏覽量

233500 -

操作系統

+關注

關注

37文章

7077瀏覽量

124938 -

MMU

+關注

關注

0文章

92瀏覽量

18637

發布評論請先 登錄

MMU多級頁表映射過程

MMU多級頁表映射過程

評論