信息和通信技術(ICT)是數據呈指數增長的源頭,這些數據需要被移動、存儲、計算、傳輸和保護。依賴特征尺寸減小的傳統半導體技術已接近其物理極限。隨著晶體管能效和晶體管尺寸的指數級增長,系統性能的擴展面臨著重大挑戰。而技術躍遷速度減緩至兩年以上,使得通過"More Moore"傳統晶體管尺寸縮小以及"More than Moore"異構集成(HI)實現成本效益型的封裝系統變得越發迫切。異構集成對于實現下一代計算和通信系統的成本和能效至關重要,通過異質集成的先進封裝為產品的密度和尺寸提供了一種創新的替代途徑,正如摩爾定律在過去55年推動了全球半導體行業的發展,異質集成正在并將成為未來的關鍵技術方向。

HI技術的進步是實現ICT中可預見的重大轉變的關鍵,其中包括:

徹底新穎的存儲解決方案和內存

處理高度互聯系統中出現的新安全挑戰的硬件

通用計算的能量消耗呈指數增長

能耗每三年翻倍,超越了尺寸縮放取得的效率改進,需要新的計算范式。因此,本章要解決的廣泛目標是:

宏偉目標:

發現具有根本新的計算軌跡的計算范式/架構,實現超過100萬倍的能效改進。

章節目標:

開發整合模擬和數字系統的技術,包括神經形態和量子計算、感應、光子學和無線通信。

高級封裝和異質集成的本章范圍包括(但不限于):

芯片-封裝架構和協同設計

下一代互連技術

電力傳輸和熱管理

材料

襯底

裝配和測試

性能和工藝建模以及模型驗證

可靠性

先進封裝下的跨領域活動包括:

- 能效和可持續性

- 供應鏈:材料、化學品、襯底

- 制造過程和性能計量

- 安全和隱私

- 設計建模測試和標準

總的來說,不同的應用需要特定領域的架構和適當的系統集成策略,確保信號和電源完整性、功率轉換和傳送、可測試性和安全性的同時高效實現性能、功耗、面積和成本(PPAC)的權衡。系統集成可能的解決策略包括:將獨立生產的組件通過水平集成到更高級別的SiP,將獨立芯粒進行三維(3D)堆疊,以及在單片集成的片上系統(SoC)中進行邏輯和存儲的精細層疊制作。SiP的架構和物理設計需要高保真度和高效性的建模工具和技術,包括基于機器學習的工具。

朝著高密度3D系統集成的進展將提高帶寬密度和能效。水平和垂直互連間距縮放以及下一代互連技術是實現高帶寬密度和能效的關鍵方法。由于I/O帶寬將與計算核心的縮放成比例增長,伴隨著封裝引腳數和I/O功耗的指數級增長,光互連的替代創新是必要的,因為它可以提供高帶寬密度、能效和覆蓋范圍。

系統集成挑戰不僅需要芯片-封裝協同設計,它還涉及封裝材料的選擇、互連間距縮放的工藝開發以及熱解決方案設計,同時需滿足可靠性和制造良率的目標。這反過來需要先進的熱點和缺陷計量、測試和模擬,從基本原理上把控系統性能和可靠性。最后,新型材料是一切互連、高密度襯底、散熱和新興設備開發方面創新的基礎。

Chip Packaging Architectures and Codesign(芯片封裝架構和協同設計)

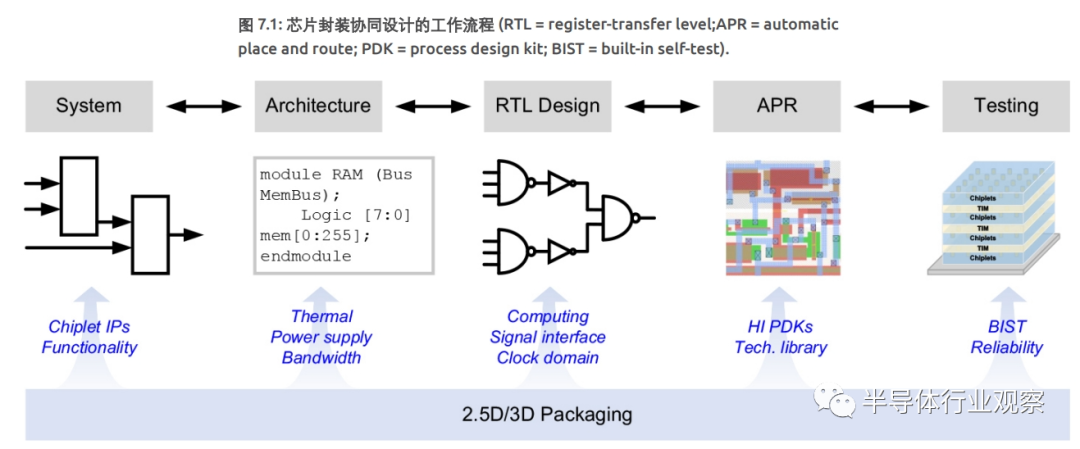

在人工智能、高性能計算、高清晰度傳感和其他新興應用領域,對帶寬、延遲和能效的需求不斷增加,盡管最近在單片芯片設計方面取得了進展,但尺寸縮放趨勢仍滯后于需求。在這種背景下,超越單片芯片的技術創新,尤其是宏觀和微觀層面的2.5D/3D異質集成,對于實現具有各種類型芯粒的未來ICT系統至關重要,并帶來顯著性能和成本效益。(先進封裝架構的趨勢及其對互連的影響在第7.3節中有描述)。這種范式轉變將推動芯粒IP設計、異質架構、片上網絡/封裝級網絡和可靠系統集成的創新(圖7.1)。

一些挑戰和研究需求包括:

為HI設計IP

芯粒及其信令接口將新的硅模塊引入微電子生態系統,具有高帶寬、高面積利用率和低成本,這開啟了IP復用的新技術和商業模式,允許不同的功能宏模塊靈活生產,而無需受到處理能力的限制。這樣的變化需要設計能力來定義物理核和芯粒間的接口,以及軟硬件協同設計對可復用IP模塊進行分類。

異質架構

芯粒和封裝設計之間的緊密協作在整個設計周期中至關重要,包括設計工具、模型和工作流程。系統架構師必須在設計過程的早期參與,分析整個系統和封裝、將設計分區為不同的芯粒,并評估在計算、數據傳輸和制造成本中的權衡。在這個階段的設計和驗證工具,如SystemVerilog,需要整合封裝設計和規劃知識,支持協同設計工作流程,這意味著對當前分離的ASIC和封裝設計流程的重大修訂。此外,對HI系統的早期預測分析對于減少(微)架構定義與設計實施之間的迭代成本至關重要。

HI系統的綜合工具

要實現芯片-封裝聯合設計,需要考慮綜合流程的每個步驟,包括架構定義、RTL設計、布局和布線、驗證以及時序/功耗分析。新一套工具還需要在彼此之間具有平滑的接口,并支持未來的芯粒設計工具包。HI綜合存在的挑戰包括:芯粒間的時序分析、熱/機械應力分析,以及各組件的功耗傳輸和完整性。

測試與可靠性

一個異質系統包含具有明顯不同電氣、機械和熱特性的多個組件。未來的異質系統測試需要提供足夠的可模塊化性質,以適應每個組件的特定測試方法,實現覆蓋率、復雜性和成本的綜合評估。自測試,如內置自測試(BIST),是一種可取的解決方案,但需要更多關于多功能聯合測試的研究。隨著在2.5D/3D集成中各種組件間的熱/機械相互作用不斷增加,可靠性評估需要從當前針對單個模塊的經驗/統計方法,轉向構建描述產品級物理可靠性模型。

Next-generation Interconnects(下一代互連技術)

眾所周知,通過使用更精細的晶體管節點(低于20納米)來縮小芯片尺寸的成本優勢已不再明顯。這就需要一種新的方法,即將單片芯片分解為較小的單元,或者芯粒。為了通過設備芯粒和被動元件的HI實現功能擴展,基板必須從芯片載體轉變為一種集成平臺,這需要新的先進封裝方法,包括:

性能優化:為每個IP塊/芯粒選擇最佳的硅工藝節點。

產品定制:通過選擇最佳性能的芯粒組合,實現對每個產品的定制。

降低成本:與單片SOC相比,單個芯粒的收益更高,能夠降低成本。

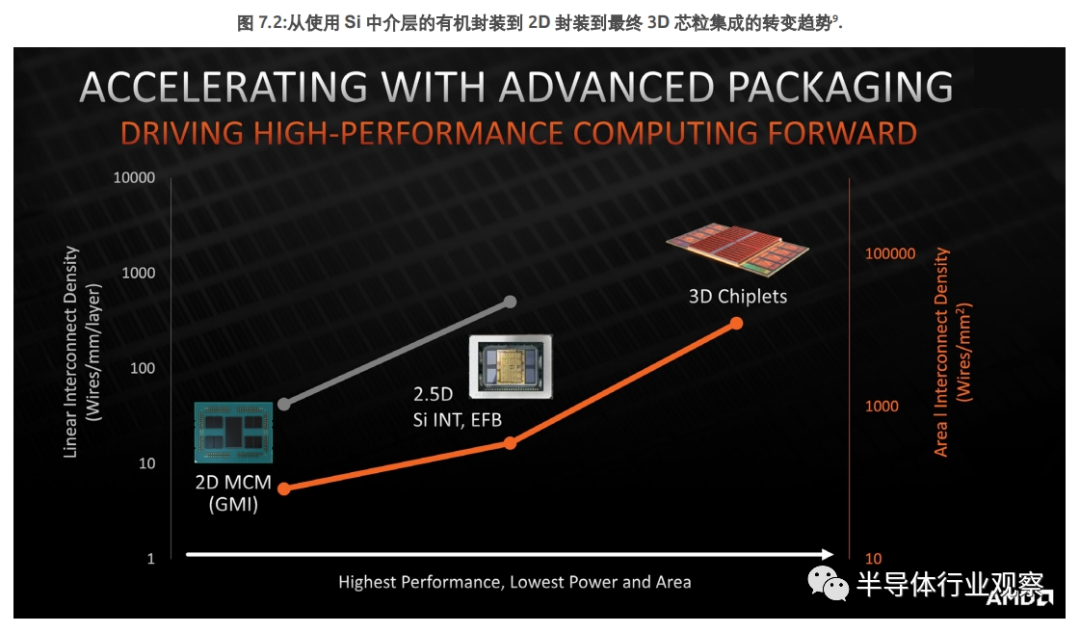

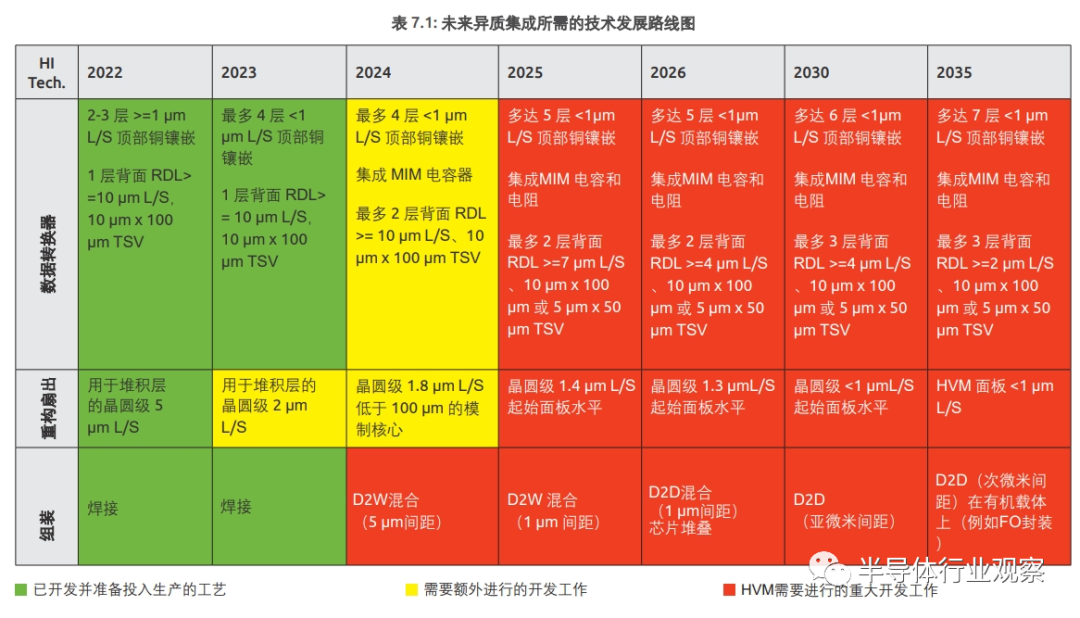

芯粒的廣泛應用預計將繼續,因為該行業致力于推動針對每種應用定制的高性能和低功耗解決方案。下一代封裝需要支持這種異質集成的激增,通過實現適應非常細的間距輸入/輸出芯片(<10μm間距)和非常細的線/空間(亞微米級別的L/S)電路。圖7.2顯示了朝向三維芯粒集成的趨勢,以實現兩個基本性能要求,包括:

(1)以IO/mm和IO/mm2計量的更高帶寬

(2)以pJ/b計量的更高效率

用于連接芯粒并實現這些未來高性能要求的HI路線圖顯示在表7.1中。為了滿足Si中間層未來的需求,需要具備在頂面生產更多層次的堆疊層和背面多層RDL層的能力,基板厚度可能還需要從100微米減少到50微米或更低。對于重構扇出技術,主要的技術驅動力將是為頂部和背面構建層生產低于1μm的 L/S。對于這兩種 HI 技術,需要適應I/O焊盤間距<10μm的芯片。此時組裝技術將從傳統焊接方法過渡到混合鍵合。未來的開發工作需要重點關注芯片到晶圓(D2W)和芯片到芯片(D2D)混合鍵合,以滿足未來的性能和成本目標。

Power Delivery and Thermal Management(供電和熱管理)

供電挑戰

從 20 世紀 70 年代初問世到現在,微處理器在復雜性和功能方面經歷了重大演變。微處理器性能和成本的指數級增長可歸因于半導體行業對摩爾定律的遵守,即芯片中的晶體管數量每兩年就會增加一倍。直到2000年代初,基于 Robert Dennard 提出的模板的傳統縮放方法在保持功率密度恒定方面非常有效。然而,隨著晶體管特征尺寸接近原子尺寸,亞閾值泄漏成為一個問題。因此,工藝工程師不得不通過材料和晶體管結構的創新來替代,以實現必要的面積縮放,跟上摩爾定律的步伐。

盡管非傳統的縮放方法在縮放晶體管面積和改善性能方面大多取得了成功,但在降低功率方面并不那么有效。微處理器的功率密度自21世紀初的Dennard尺寸縮放崩潰后開始上升。此外,盡管Dennard尺寸縮放提供了減少柵極延遲的手段,但尺寸縮放互連維度并沒有導致RC互連延遲的降低。隨著互連延遲接近時鐘周期的重要部分,它成為增加處理器頻率的另一個瓶頸。雖然架構的改進導致每個時鐘周期的指令數(IPC)的提高,但這還不足以克服頻率縮放的不足,這導致了單核性能縮放的放緩,當單核性能趨于穩定時,微處理器架構師采用了多核心和工作負載并行化的方式來最大化性能,由于核心數量的增加導致功率軌道增加,這給將電源傳輸到微處理器的問題增添了復雜性。另一個導致額外電源傳輸挑戰的因素是熱設計功率(TDP)尺寸縮放,在這些高功率段的微處理器中,未來將會吸收超過1000安培的電流。對于低功率移動處理器,主要側重于減少設備的整體尺寸并最大化電池壽命,因此,微處理器、內存和電壓調節器所占用的面積被迫縮小,以騰出空間給更大的電池。此外,對更薄設備的追求意味著微處理器和電源傳輸組件(例如電感器和電容器)的高度都不得不縮小。

供電解決方案

集成電壓調節器(IVR)已經成為解決前述許多電源傳輸挑戰的關鍵解決方案。IVR廣義上被定義為在封裝或芯片上整合電壓調節的解決方案。IVR選項變得越來越受歡迎,并已在許多商用微處理器上實施。通過細粒度電源管理以最小化功耗,導致了大量電源軌的出現。由于缺乏平臺級資源,使得在平臺上擁有數十個穩壓器并不現實。更有效的方法是利用有限的資源擁有少量強大的平臺級穩壓器,這可以提供封裝級別或芯片上的各種集成電壓調節器的輸入電源。推動IVR發展的另一個因素是處理器功率水平的穩定增長,尤其是數據中心的CPU和GPU。隨著功率水平的提高,供電網絡中的路由損耗會對整個系統效率產生重大影響。IVR 可以通過以更高的電壓為處理器供電來解決這個問題。這減少了通過供電網絡的電流,并最大限度地減少了 PD 網絡中的布線損耗。在高功率水平下,布線損耗的減少足以抵消 IVR 引入的轉換損耗。

IVR 可根據其拓撲進行寬泛的分類。最簡單的片上供電解決方案是電源門開關,電源門用于關閉閑置電路的電源,以最大限度地減少其泄漏功耗。功率門的常見應用是使用單個平臺級電源向多個內核供電。功率門的最大缺點是它們無法調節輸出電壓。線性或低壓差 (LDO) 穩壓器通過在設計中包含控制環路來解決這一缺陷。由于沒有能量存儲元件,LDO 也相對容易在芯片上實現。然而,LDO 通常僅限于輸入電壓接近輸出電壓的應用。因此,它們不是高功率電源軌的最優選擇,因為使用 IVR 的動機是通過以明顯更高的電壓引入電源來最大限度地減少布線損耗。

開關穩壓器更適合需要更高輸入電壓的 IVR 實施。開關穩壓器使用儲能元件來實現高效電壓轉換。降壓穩壓器中的儲能元件是電感器,而開關電容穩壓器(SCVR)則使用電容器作為其儲能元件。由于電容器通常比電感器具有更高的能量存儲密度,因此可以設計高效緊湊的 SCVR。然而,簡單的 SCVR 的調節性能較差,因為它們最適合從輸入到輸出的固定比率轉換,并且當輸入到輸出電壓顯著偏離最佳比率時,效率通常較低。

最近,已經引入了基于新型切換電容器的混合拓撲結構,以解決這些缺點。還實施了基于降壓調節器和線性調節器的混合方案。為了生成具有較少電感器的可擴展芯片內電源域,已經實施了單電感器多輸出(SIMO)調節器,并增加了線性電壓調節器用于瞬態管理。

最近引入了新的基于開關電容器的混合拓撲來解決這些缺點,還有基于降壓穩壓器和線性穩壓器的混合方案。為了使用更少的電感器生成數量可擴展的片上電源域,采用了單電感器多輸出 (SIMO) 穩壓器,并增加了用于瞬態管理的線性穩壓器。

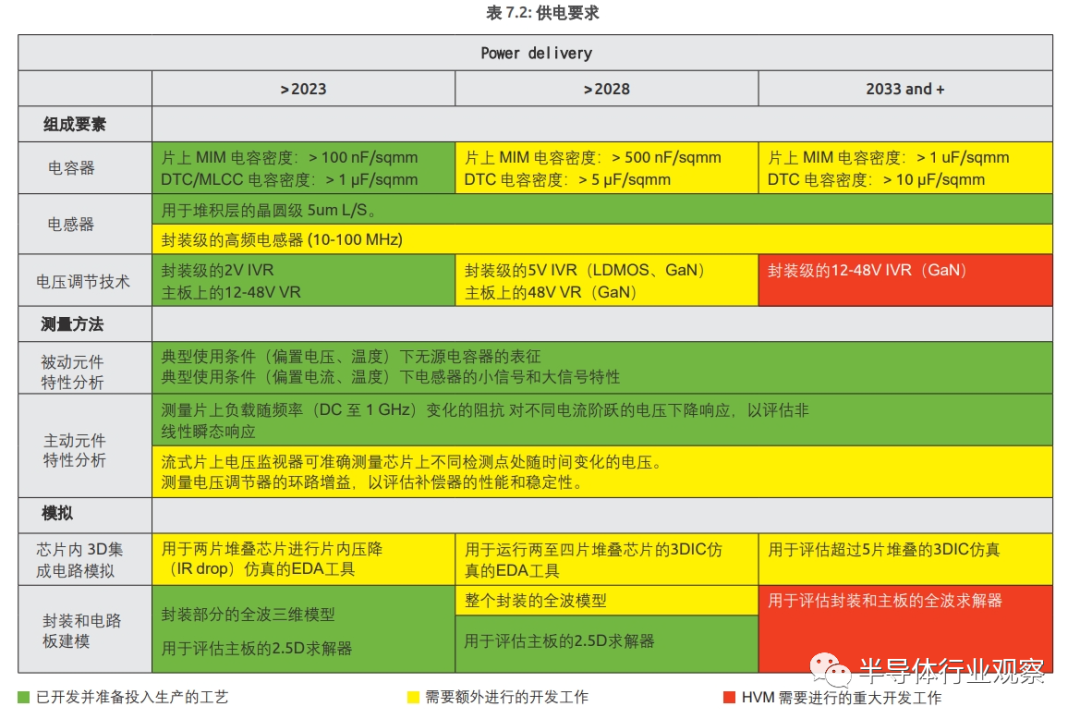

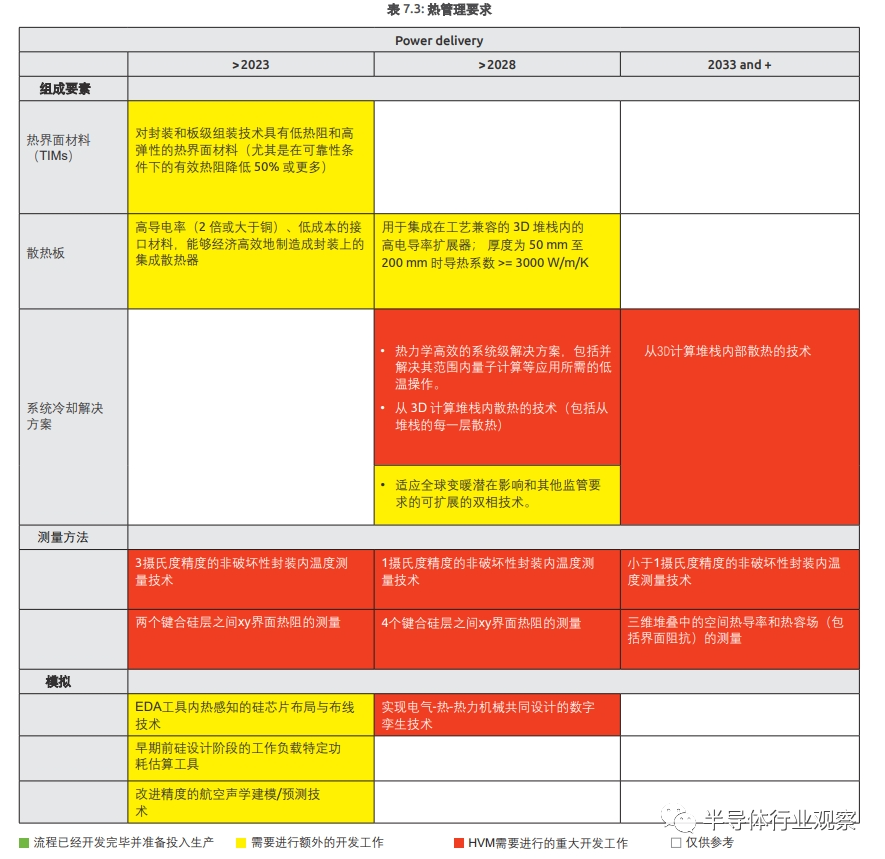

表7.2列出了先進封裝未來的供電要求。

熱管理挑戰

理解應對先進封裝和異質集成的熱挑戰的未來路線圖,需要首先回顧歷史架構趨勢。在早期的高性能計算應用中,摩爾定律下的晶體管尺寸縮放和產品架構選擇旨在提高性能,導致熱問題的焦點首先集中于解決高功率密度(由于更高頻率的晶體管運行和工藝縮放)以及應對更高的總封裝功耗。這種不可持續的趨勢在21世紀初得以突破,這要歸功于架構的改進,例如多核架構和對每個時鐘周期的指令的更高關注。隨著多核架構的出現,重點是利用摩爾定律的能力提供額外的核心用于計算性能和并行指令。這個時代也看到了首次向IP(如內存控制器、圖形等)的異質集成的趨勢。近年來,由于先進的封裝技術,這種趨勢加速發展,它允許不同數量的芯粒、電源傳輸元件、內存塊等在封裝級別整合,通常是形成一個3D異質封裝。最近的產品中,有超過1000億個晶體管,跨五個不同的工藝節點整合成一個單一封裝,并包含47個活動的計算瓦片。

這些趨勢預計將持續下去,而且很可能會加速到未來的計算產品中。因此,以下是與工藝縮放和先進封裝相關的熱挑戰:

由于持續的工藝擴展,小芯片級別的功率密度增加,并且性能/頻率隨著時間的推移而增加。在 3D 堆棧將創建附加有效功率密度的架構中,這種情況將會加劇,需要仔細進行堆棧之間的平面布局優化,減輕功率密度,以使架構能夠支持。

異質架構傾向于多點熱優化,因為零件可能面臨多種工作負載,以及核心/執行單元數量持續增加。而高級封裝熱架構通常需要進行熱權衡以改進,封裝的一個部分中的熱量以封裝的另一部分為代價。

高速IO的功率密度不斷增加(例如高速SERDES)。在某些情況下,需要將這些 IP 塊放置在3D堆棧的基礎芯片中。這將增加 IP 模塊功耗的難度,因為硅金屬堆疊(無論是面對面還是面對背的3D堆疊)中的互連和介質層導致基礎芯片和3D堆棧頂部之間的熱阻較高。

需要跨封裝規模和系統規模進行熱優化。封裝的尺寸和復雜性一直在增加,而系統冷卻方法也越來越靠近封裝(例如,從銅散熱器轉向距離封裝相對較近的液體冷板)。導致需要對系統散熱器與封裝熱設計進行協同設計(并且通常要考慮到特定的工作負載)。這首先出現在移動領域,筆記本電腦散熱解決方案中熱管的位置、尺寸和方向需要考慮封裝核心布局,隨著 3D 集成和先進封裝的不斷增加以及系統級熱解決方案的改進,這種需求預計將會增長。

隨著 3D 封裝中每層硅厚度的減小,熱點的橫向擴散水平大幅降低。當熱量離開封裝時,這會增加有效功率(熱)密度,并增加對封裝內熱缺陷的敏感性。例如,當硅厚度從 700μm 減小到 100μm 時,與封裝接觸的熱界面中的臨界缺陷尺寸相應減小。,這需要以高分辨率(x、y和z)了解3D堆棧內的熱特性(特別是電導率)。

以上挑戰推動著對新的元件、測量和模擬技術的需求,如表7.3所示。

Materials(材料)

加工后保留在半導體封裝內的材料(例如直接材料)被定義為成分。這些材料包括載體(基板、引線框架、中介層、構建材料、重新分布層等)、芯片附著、封裝材料、底部填充,以及熱解決方案(例如蓋子、熱界面材料等)。與成分相反,“輔助”材料用作工藝消耗品(例如膠帶、抗蝕劑、化學品和漿料);這些不屬于本節的范圍。

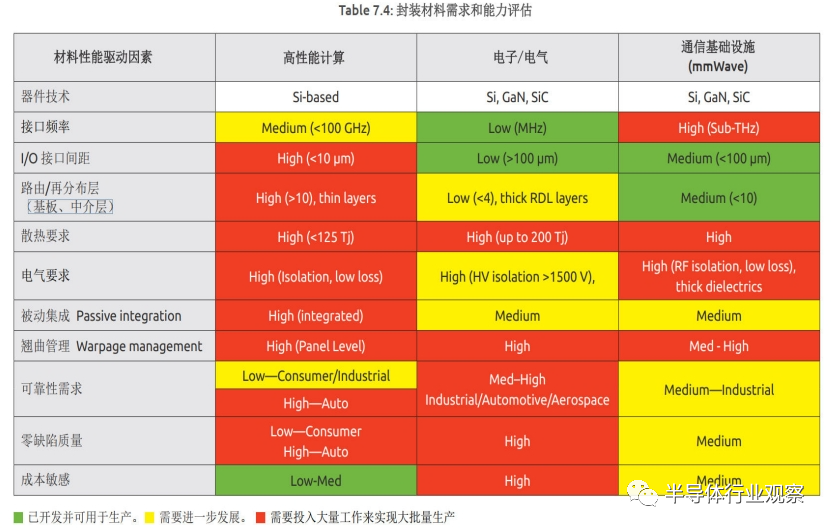

應用驅動因素,包括高性能計算、電力電子/電氣和亞太赫茲通信基礎設施,將用于指定新材料功能,以在先進封裝的背景下增強系統級性能。重點領域包括所需的材料改進 以實現更高的封裝布線密度/小型化、改進的電氣性能以及機械和熱性能的增強,從而提高可加工性和可靠性。需要先進的熱解決方案在最大器件結溫、尺寸和成本的限制內實現系統級性能。封裝平臺要求范圍從傳統的層壓板和基于引線框架的封裝到高密度倒裝芯片/扇出晶圓級和大尺寸面板級封裝,以實現下一代產品的成本和性能目標。

下一頁上表7.4中列出了應用性能需求,進而推動了材料特性、加工性和性能的需求。具體的材料需求和發展路線在第8章中有詳細說明。

襯底(Substrates)

由于襯底從芯片載體過渡到集成平臺,襯底平臺的驅動屬性也需要過渡到新的規模關系和目標上去。該襯底平臺的驅動屬性或屬性包括凸塊間距和I/O縮放,用于芯片互連和通過嵌入分立元件進行供電。

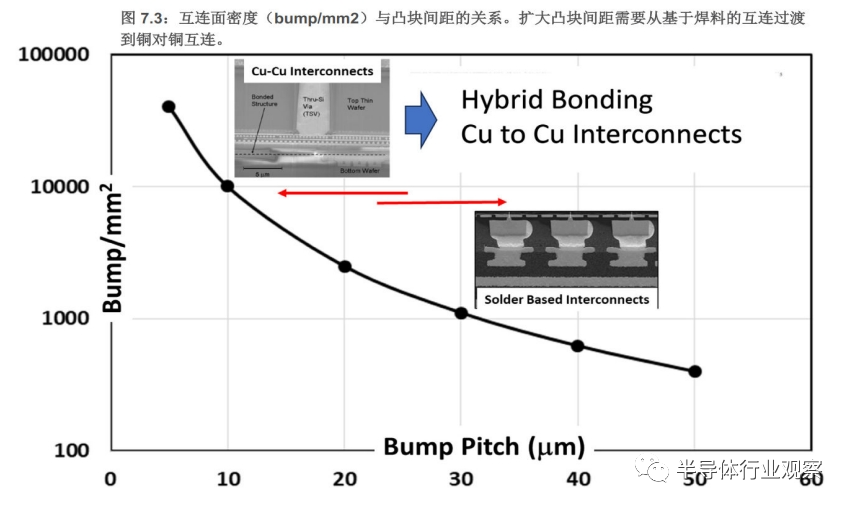

對于高性能計算(HPC)應用,行業領導者提出了一種可擴展到10,000 IO/mm2的平臺。將這一性能指標轉換為互連上意味著互連面積密度等于10,000個凸塊或焊盤每平方毫米,這就要求凸塊或焊盤間距為10微米。如圖7.3所示,這一密度要求互連置于焊料互連和銅銅互連之間的過渡區域——這一過渡將給組裝和基底技術帶來挑戰。對于基板技術來說,走線寬度、銅厚度、相關間距要求以及介電材料和堆積盲孔焊盤直徑將影響面密度能力。

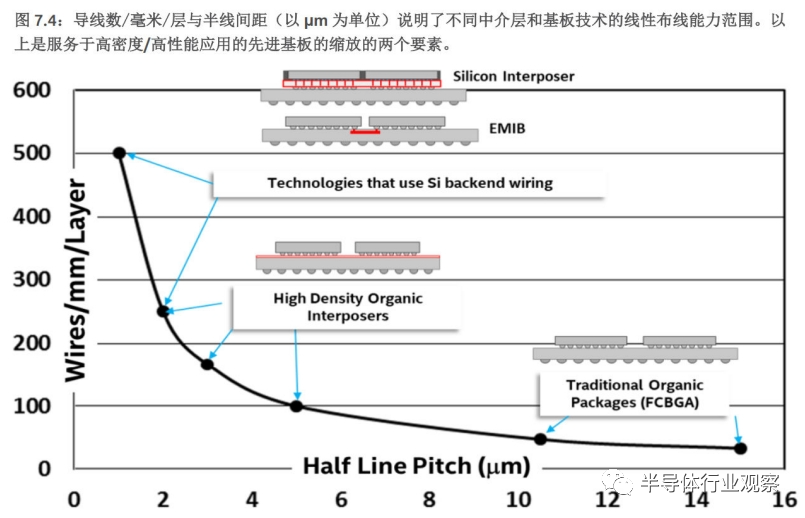

此外,利用HI技術的HPC應用將需要更高和更低的線密度的布線層。布線層數將取決于所需的IO密度,以及所需的集成度和性能水平。同樣,如圖7.4所示,導線數/毫米/層與以微米為單位的半線間距說明了不同中介層和基板技術的線性布線能力范圍。

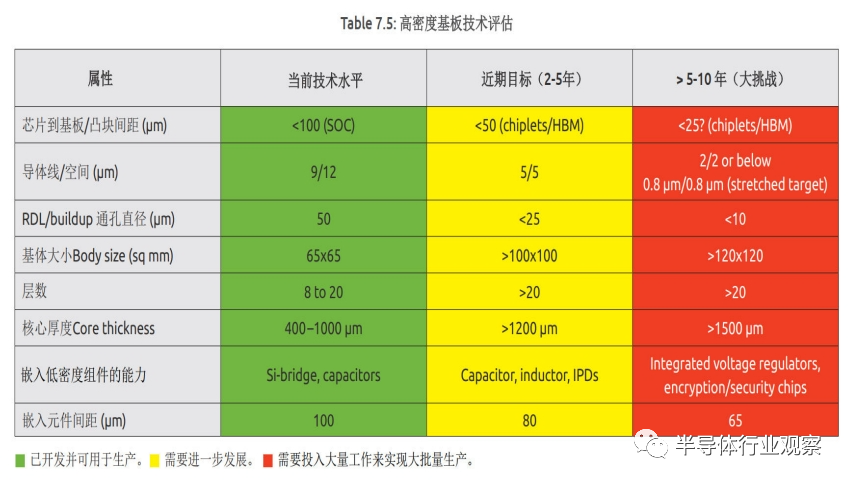

總而言之,未來的高密度襯底實現有幾種選擇。一種方法是將細間距凸塊芯片(大多數情況下是芯粒)連接到高密度有機基底上,其特征線寬和空間≤2μm。雖然有人擔心目前的材料和工藝可能無法支持低于5μm的特征線寬和空間,但目前正在研究開發新的材料和工藝,以實現預期目標。另一條途徑是使用有機/無機再分布層(RDL)來對附著的細間距凸塊進行布線。模制或組裝的RDL結構將附著在密度較低的層壓基板上。此外,還可以使用潛在的新材料替代品。表7.5總結了高密度基板技術的發展趨勢。

在任何途徑中,都有必要專注于制造科學和工程,以提高經濟效益,促進先進的基板制造實踐。為了使美國在這一領域具有競爭力,人們需要制定具體的運營目標,包括產量、產出和利用率,并與工業4.0(智能制造)計劃保持一致。

工作頻率高于6GHz的射頻器件需要創新的解決方案,以實現高水平的功能集成,同時確保最佳的芯片工作溫度。因此,對新材料、結構和裝配技術的需求不斷增長。

5G和6G設備中使用的基板不再是簡單的印刷電路板(PCB)。使用的基板是支持系統集成的關鍵構件,通常被稱為系統級封裝(SiPs)。它們現在正推動著先進集成電路基板技術的發展,這在以前是以標準印刷電路板為載體的。

未來的系統,尤其是那些工作頻率高于100GHz的系統[1-3年內:110-170GHz(D波段);3-5年內:220-350GHz(G波段)],是支持實施多個芯片的尖端產品,能夠處理和傳輸更多的數據。用于制造射頻封裝和模塊的先進基板技術比以往任何時候都更受微型化的驅動。

在不久的將來,人們將需要能夠同時嵌入多個無源元件和至少一個有源元件的技術。因此,下一代射頻設備將需要先進的集成電路基板技術,不僅需要具有更高對準精度的組裝技術外,還需要例如L/S低于15/15μm,間距小于20μm,焊盤小于30μm的微型化技術。

此外,導電走線和天線貼片需要以超低的表面粗糙度制造。在使用低Dk/Df材料的同時,這些跡線可能會受到分層的影響。因此,這些通常以層壓板為基礎的基板可能需要粘合促進劑來避免分層,同時仍能保證出色的性能。最后,這種面板級系統(500mm面板上μm量級)的制造需要基于仿真的流程優化,以避免翹曲和可靠性問題。

組裝和測試(Assembly and Test)

裝配

電子系統的封裝必須考慮防止機械損傷(芯片的機械保護)、電氣連接(輸入/輸出)、冷卻(去除電路功能和器件泄漏的散熱)、空間轉換(從微觀到宏觀互連的過渡)、射頻噪聲發射、靜電放電和產品安全。

傳統的裝配工藝流程如下:

模具、分揀和拾取/背面磨削

芯片和組件的放置和連接

封裝(底部填充膠)

散熱解決方案/蓋子連接

球柵陣列(BGA)和組件連接

檢查

模塊測試

掃描并打包

先進封裝包括各種組裝技術。這些組裝技術用于將芯片集成到封裝中,能延續摩爾定律,提高系統性能和能效,并降低成本。各種組裝技術包括扇出晶圓級封裝(FOWLP)、再分布層(RDL)、系統級封裝(SiP)、2.xD(中介層、橋接板)和3D集成。

組裝技術和工具已從傳統的二維多芯片模塊封裝發展到可在二維SiP上實現裸片/芯粒(不同尺寸和功能)和元件的異質集成。人們需要對生產線進行改造和優化,以實現多芯片、組件放置(包括頂面金屬(TSM)和背面金屬(BSM))、焊膏篩選、焊膏檢測和自動光學檢測。組裝流程需要元件之間有更嚴格的間距,并采用先進的基本規則將芯片連接到層壓板上。例如,在封裝步驟中,需要在限制區域內使用具有高通量的新型點膠工具,進行精確、可重復的小批量點膠,從而實現毛細管底部填充。除了由更小間距驅動的先進裝配技術外,發展組件返工工藝也是需要的。最后,這些新的裝配工藝必須是可制造的,同時還要滿足制造產量目標,確保足夠的可靠性規格,并在成本上有競爭力。

裝配挑戰

從傳統倒裝芯片封裝(間距200-150μm,基于焊料的互連)到基于銅柱(CuP)的細間距(130μm)的轉變,以及提供更高互連密度的新層壓板設計基本規則,為組裝和制造帶來了新的挑戰。最終采用大型層壓格式(>80mm x 80mm)、增強型熱解決方案和新型互連結構(CuP)必然會導致組裝前和組裝過程中的材料和工藝發生變化。這些受影響材料和工藝的一些例子是:不同的助焊劑策略(噴涂與浸漬)、新型封裝材料以及熱性能仍與BGA產品兼容的替代熱界面材料。需要新的工具來處理這些大型層壓板增加的翹曲,以確保BGA共面性和/或元件篩選-工藝兼容性(TSM/BSM)。這些復雜的模塊布局也需要新的檢測工具。

為了解決高帶寬和在向芯粒過渡過程中對額外I/O的需求,有必要推進超細間距封裝(<=55微米間距)、CuP和先進封裝解決方案(如2.xD、硅橋)以及3D垂直集成等更先進技術的發展。組裝芯粒(可能更薄、多間距,懸臂)以及使用這些先進技術元件的組件,需要更精確的切割/拾取和放置工具,同時能夠處理更薄的硅。此外,還需要替代的芯片連接方法和工具,例如用熱壓焊接取代大規模回流焊,并加入可能用于封裝和/或助焊的非導電漿料(NCP)材料。此外,封裝工藝本身可能需要在有限的區域內進行更精確的點膠,這就需要新的點膠工具和/或新的點膠泵。這些更高密度的復雜模塊布局還需要新的檢測工具來進行晶圓進料檢測、連接前和連接后檢測以及封裝檢測。這些新的裝配工藝必須具有可制造性、可靠性和成本競爭力。由于某些高性能應用可能需要更高的潔凈室規格,因此必須考慮裝配極細間距封裝時的污染控制。

在未來十年甚至更長的時間內,需要向更細的間距(<10μm)發展,以滿足未來芯片性能對互連密度的極高要求,并在保持信號和電源完整性的同時,降低功耗以提高能效。組裝技術和工藝需要從基于焊料的互連過渡到無焊料互連(Cu-Cu)。這一過渡將涉及硅堆疊解決方案的開發,以及晶圓到晶圓(D2W)或晶粒到晶粒(D2D)混合鍵合工具的開發。此外,混合鍵合工藝還需要化學機械平坦化(CMP)等晶片精加工設備,以及比組裝/制造生產線更清潔的環境。

共封裝光學器件(CPO)對于滿足未來的帶寬和功率需求至關重要。我們可以預見CPO的廣泛應用,從數據中心(多芯片模塊或MCM CPO)到人工智能/高性能計算(3D CPO 晶圓級處理),再到未來的硅光子(SiPh)芯片系統。將光學引擎集成到SiP和其他采用先進封裝解決方案的產品中,會面臨獨特的挑戰,這些挑戰取決于光學引擎集成到封裝中的裝配步驟。例如,可能需要使用無焊劑芯片連接工藝、低溫固化熱界面材料、密封帶材料以及低溫BGA合金。構建光學引擎需要一整套不同的技能,包括光纖連接組裝工藝、模塊連接(回流光纖元件的能力)和光學特性分析。CPO面臨的巨大挑戰之一將是光纖連接組裝,因為隨著設計基本規則的改進,光纖的密度會增加,連接工藝的復雜性也會增加。

測試挑戰

先進的封裝和異構集成產生了各種各樣組合的系統級封裝設計和應用。這種組合制造中測試的開發在許多方面都具有挑戰性。具體來說,在設計中使用現成的現有芯片會導致非優化的測試設計(DFT,design-for-test)集成。DFT的插入通常是在單芯片設計基礎上進行的,沒有考慮到SiP中多個芯片的影響。這導致DFT存在缺陷,使自動測試設備(ATE,Auto Test Equipment)中的儀器更加昂貴,由于測試時間更長(順序比率與并發測試的可能性相比)、掃描測試模式數量龐大以及必須傳輸到SIP-ATE測試儀的數據量更大,總體測試成本會更高。

考慮到模擬、射頻、毫米波和光子學應用,對ATE的數字和非數字通道數提出了更高的要求。具有細間距凸塊芯粒也具有挑戰性,不過它們為測試的進一步發展提供了機遇。

要應對未來預期的挑戰,就必須進行創新。SiP DFT需要實現全行業的標準化,并在市場上得到廣泛采用,同時還需要支持制造級和短測試時間的測試架構,以及具有電源感知的診斷測試功能。采用SiP封裝和芯粒設計新標準的EDA行業領導者需要促進ATE儀器/軟件產品以更低的成本、模塊化、高通用性和重復利用率實現迅速發展。此外,還需要通過SiP配置感知引擎和具有電源感知節流功能的超級SiP內建自檢(BIST)引擎,在芯片中實現自動掃描和算法測試模式的生成、采樣。

性能和過程建模以及模型驗證(Performance and Process Modeling and Model Validation)

經過驗證的性能和工藝建模是加速微電子和先進封裝技術發展的關鍵。復雜的異質集成(HI)系統建模面臨的一個重大挑戰是需要跨越近八個數量級的長度尺度(從埃到厘米),跨越材料/結構、器件、芯片和封裝,同時需要將材料、電氣、光子、電磁、熱和機械行為結合起來。從廣義上講,建模有幾種作用:

從頭開始介入開發新型材料和界面;

在設計探索過程中評估大致性能;

通過詳細分析,為改進設計創建準確的行為評估;

通過模擬協助制造工藝開發

通過缺陷預測提高制造工藝產量。

為了使模型發揮其預期作用,必須對其進行嚴格驗證。

通常,模型中的數據表示包括每個長度尺度上的物理和幾何屬性。各尺度之間的信息交換包括材料、幾何和模擬屬性。由于每個尺度都有自己的控制方程,因此需要在尺度之間建立接口,以提供一個獨立于底層模型的模塊化鏈接平臺。因此,模型抽象需要模塊化、靈活化,并且與規模、材料和幾何無關。機器學習(ML)模型可能是此類抽象的理想候選。

以下是建模中必須解決的特定元素的詳細信息。

用于協同設計的快速多物理場、多分辨率建模

從原子到系統級(多尺度)的快速、大規模和耦合多物理場建模和分析是實現異構集成協同設計的必要條件。不同長度尺度的多物理場模型需要在不同精度水平上進行結合,以支持不同的協同設計需求。需要融合機器智能和領域專業知識,以顯著加快器件、電路和系統級的建模、分析和優化。

跨設計層的異構不確定性量化(UQ,uncertainty quantification)

需要對過程變化下復雜異構系統的不確定性進行量化。這類模型非常具有挑戰性,因為存在許多相互關聯的設計模塊、高維不確定性源以及對不確定性統計行為的了解不足。

芯片和封裝結構的高保真失效模型

詳細的多尺度行為模型對于準確估算加工條件的失效時間或可行性十分必要。隨著硅通孔(TSV)和互連線被縮小到亞微米長度尺度,以及焊接凸點被縮小到數十微米,微觀結構將會影響電遷移驅動的空洞和疲勞斷裂。目前還沒有針對這些失效機制的高保真模型

材料和界面模型

半導體技術的規模化導致材料和結構之間的尺寸趨同,進而產生了新的特性和特征。其中的例子包括電子、電氣、熱、機械和化學特性之間的復雜融合。此外,規模化使得界面對材料變得至關重要。一般來說,需要建立從量子到連續體的材料和界面模型。

材料屬性數據庫

器件級(FEOL、BEOL金屬和低維材料)、芯片級(三維互連和接合界面)和封裝級(焊料/底部填充膠、模塑料、再分布層、凸塊、熱界面材料和冷卻解決方案)的結構建模需要開發一個準確的材料特性數據庫。此外,還需要利用計算流體動力學(CFD)建模來發展有效傳熱系數預測的經驗關聯式。表7.6列出了上述建模需求的現狀。

可靠性(Reliability)

異質集成封裝的可靠性至關重要,其可以滿足高性能電子系統日益增長的需求。巨大的挑戰包括先進封裝架構、材料和結構的集成(如先進的粘合劑和自修復材料的使用),先進建模和仿真技術的使用,以及新測試和鑒定方法的開發。

一般而言,產品的可靠性是指產品在預期使用壽命內執行其核心功能的能力。核心功能性能的降低以及輔助功能的喪失將被視為可靠性的降低或受損,但不是可靠性的喪失。先進封裝和異質集成的可靠性損失和降低是由器件、封裝、子系統和系統的過應力和/或磨損機制引起的故障造成的。過應力失效發生在施加的負載超過材料的臨界負載/強度時,而磨損失效則發生在重復或循環施加亞臨界負載時。過應力失效機制通常是災難性的、突發性的,例如脆裂、脫粘、熔化和介電擊穿。磨損失效機制是漸進和累積破壞性的,例子包括互連開裂、脫粘和電遷移。

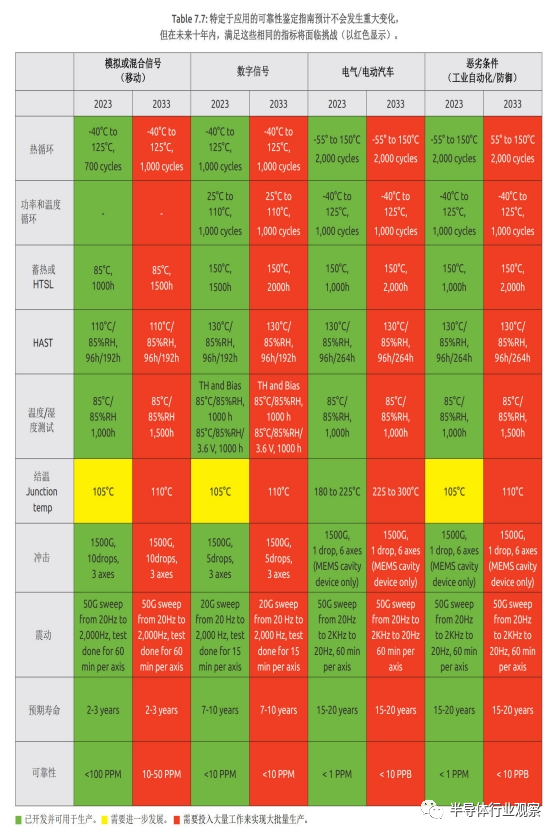

過應力和磨損失效機制都是由熱、機械、電氣、化學、輻射、磁和濕度負載單獨作用以及相互組合作用引起的,例如熱機械、熱濕機械、熱電和熱化學負載。這些負載可能來自產品的內部工作和/或外部環境或操作條件。這些內部和外部條件的具體應用程度和持續時間對于評估可靠性至關重要。這種評估可通過物理原型和測試以及虛擬(模擬)原型和測試來進行。表7.7提供了針對具體應用的可靠性鑒定準則。

隨著三維、混合接合、嵌入式橋接和其他先進技術的發展,異構集成正在以新材料、創新工藝和測試協議進行橫向和縱向發展。然而,在要求更高的功能、更好的性能和更強的功率的同時,還需要更小的尺寸、更輕的重量和更低的成本,這就給可靠性和測試帶來了挑戰。這些先進封裝的可靠性對于實現這些技術至關重要。因此,表中的鑒定指標在未來10年內不會發生重大變化,但會以紅色顯示,特別是因為這些新材料、新工藝和新尺寸在設計時如果沒有預先考慮到可靠性,那么要達到(與原有設計)相同的可靠性指標將非常困難。

挑戰、未來需求和可能的解決方案(Challenges, Future Needs, and Possible Solutions)

基于傳統半導體尺寸規模,對更高性能和更大帶寬的需求已達到其物理極限。因此,隨著晶體管柵極間距縮小速度的放緩和芯片尺寸達到掩膜極限,芯粒系統架構成為行業的答案。要實現高性能計算以及未來量子和人工智能技術的芯粒集成,需要先進的封裝解決方案。總體而言,封裝引腳數和I/O功耗的指數級增長、特定領域的架構、IP重用的技術和商業模式以及混合技術節點芯片將推動異構集成和先進封裝的進步。

先進封裝的技術進步需要新的設計工具,使封裝設計能夠支持協同設計工作流程和預測建模,以最大限度地降低架構和設計實施之間的迭代成本。在設計和分析HI/AP系統時,模型需要跨越近八個數量級的長度尺度,并且需要進行多物理場分析,這些都將是重大挑戰。由于CPU和GPU功率的增加會導致路由損耗,從而對整個系統的效率產生重大影響,因此需要使用集成穩壓器以更高的電壓供電。功率耗散的增加將需要通過封裝熱設計對系統散熱策略進行協同設計。在3D堆棧架構中,這種情況將加劇,這將產生累積的有效功率密度,需要仔細的堆棧間布局優化,以降低架構需要支持的功率密度

下一代封裝的極端互連密度需求將推動超細間距(間距小于10μm)和超細線/空間(低于1μm L/S)電路的發展。組裝技術和工藝需要從基于焊料的互連過渡到無焊料互連(銅-銅)。這一過渡將需要開發硅堆疊解決方案和用于芯片到芯片或芯片到芯片混合鍵合的工具。最后,對更小尺寸、更輕重量和更低成本的需求將推動可靠性和測試方面的挑戰。雖然在未來10年內,認證指標可能不會發生重大變化,但如果這些新材料、新工藝和新尺寸在設計過程中不考慮可靠性因素,要達到相同的可靠性指標將面臨挑戰。

本號對所有原創、轉載文章的陳述與觀點均保持中立,推送文章僅供讀者學習和交流。文章、圖片等版權歸原作者享有,如有侵權,聯系刪除。

北京漢通達科技主要業務為給國內用戶提供通用的、先進國外測試測量設備和整體解決方案,產品包括多種總線形式(臺式/GPIB、VXI、PXI/PXIe、PCI/PCIe、LXI等)的測試硬件、相關軟件、海量互聯接口等。經過二十年的發展,公司產品輻射全世界二十多個品牌,種類超過1000種。值得一提的是,我公司自主研發的BMS測試產品、芯片測試產品代表了行業一線水平。

-

半導體

+關注

關注

335文章

28538瀏覽量

231912 -

封裝

+關注

關注

128文章

8454瀏覽量

144710 -

ICT

+關注

關注

3文章

424瀏覽量

36947 -

芯片封裝

+關注

關注

11文章

568瀏覽量

31228 -

先進封裝

+關注

關注

2文章

458瀏覽量

496

發布評論請先 登錄

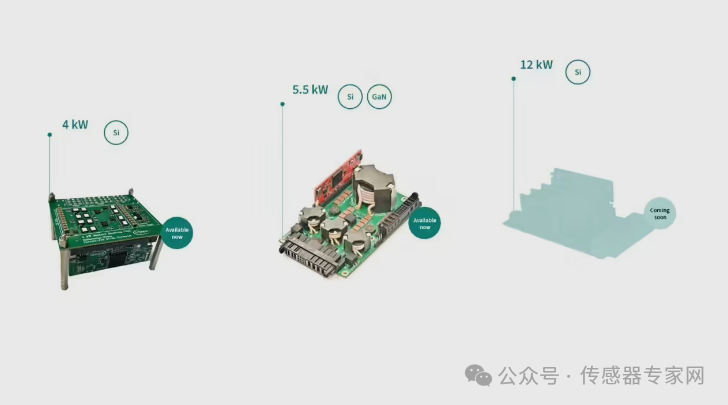

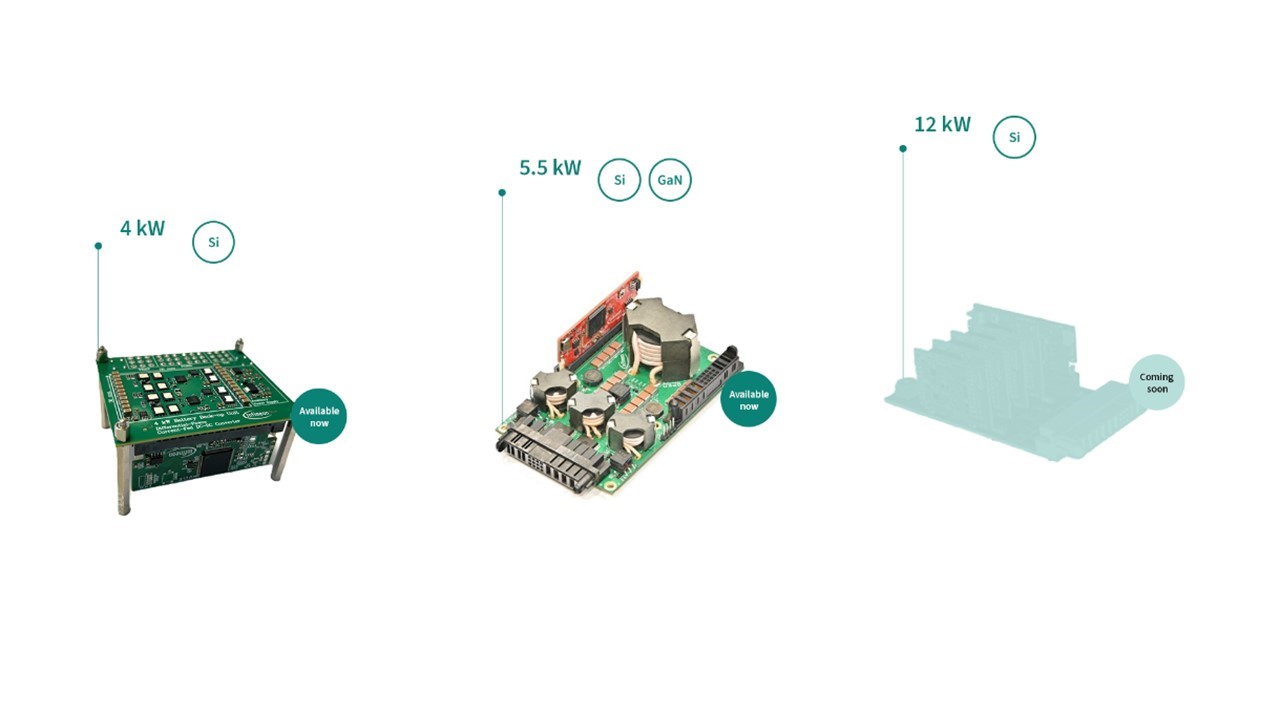

英飛凌公布AI數據中心電池備份單元BBU路線圖,全球首款12kW系統在列

英飛凌針對AI數據中心推出先進的電池備份單元技術, 進一步完善Powering AI路線圖

OpenAI簡化大模型選擇:薩姆·奧特曼制定路線圖

英特爾IEDM 2024大曬封裝、晶體管、互連等領域技術突破

睿創微納五年&十年功勛員工頒獎大會圓滿舉行

Chiplet在先進封裝中的重要性

關于RISC-V學習路線圖推薦

未來10年智能傳感器怎么發展?美國發布最新MEMS路線圖

何小鵬宣布未來十年愿景,加速全球化AI汽車布局

沃達豐與谷歌深化十年戰略合作

2024學習生成式AI的最佳路線圖

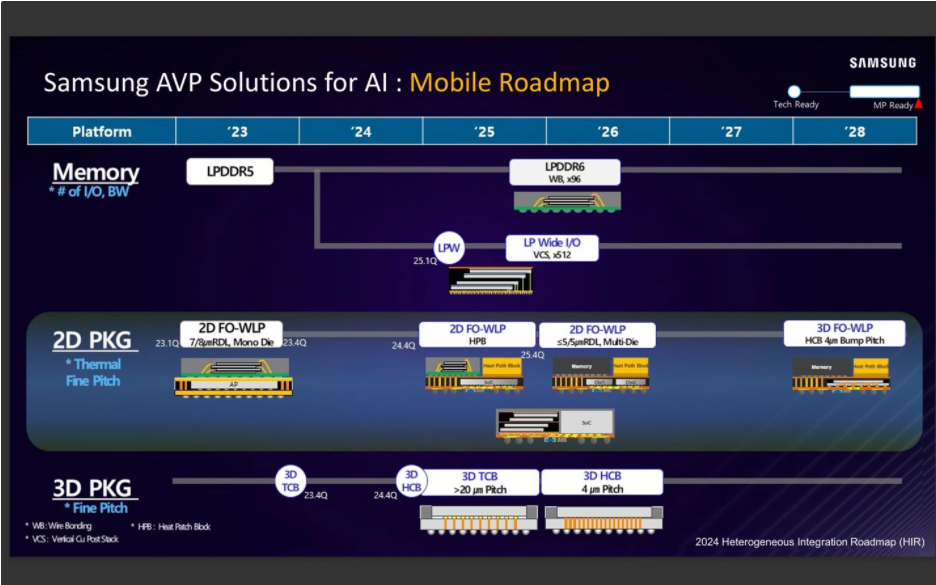

三星電子公布2024年異構集成路線圖,LP Wide I/O移動內存即將面世

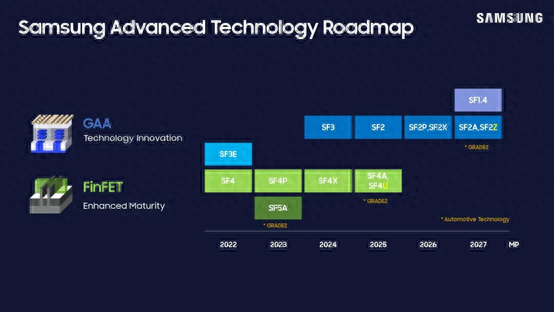

三星公布最新工藝路線圖

英飛凌為AI數據中心提供先進的高能效電源裝置產品路線圖

先進封裝,十年路線圖

先進封裝,十年路線圖

評論