本應(yīng)用筆記旨在幫助客戶(hù)使用Microchip的10/100/1000 Mbps以太網(wǎng)器件系列設(shè)計(jì)PCB。本文檔提供有關(guān)PCB布線的建 議, PCB 布線是保持信號(hào)完整性和減少EMI問(wèn)題的關(guān)鍵環(huán)節(jié)。本文涵蓋以下主題:

?通用PCB布線指南

?以太網(wǎng)布線指南

?EMI注意事項(xiàng)

?ESD注意事項(xiàng)

?常見(jiàn)布線問(wèn)題疑難解答

01通用PCB布線指南

電源注意事項(xiàng):

確保足夠的電源額定值。確認(rèn)所有電源和穩(wěn)壓器都能提供所需的電流大小。

電源輸出紋波應(yīng)限制在50 mV以下(為了獲得最佳性能,最好小于10 mV)。

所有電源和地平面上的噪聲水平應(yīng)限制在50 mV以下。

鐵氧體磁珠的額定電流應(yīng)為預(yù)期提供電流的4-6倍。另外,還應(yīng)考慮因溫度產(chǎn)生 的降額。

器件去耦:

PCB裝配上的每個(gè)高速半導(dǎo)體器件都需要去耦電容。每個(gè)電源引腳都需要一個(gè)去耦電容。

去耦電容值取決于應(yīng)用。典型的去耦電容值范圍為0.001 μF至0.1 μF。

總?cè)ヱ?a href="http://www.asorrir.com/tags/電容/" target="_blank">電容應(yīng)大于提供給數(shù)字輸出緩沖器的負(fù)載電容,以避免將噪聲引入電源。

通常,選擇II類(lèi)介電電容進(jìn)行去耦。首選方案是X7R介電陶瓷電容,因?yàn)樗哂谐錾姆€(wěn)定性、合理的封裝尺寸以及優(yōu)異的電容特性。設(shè)計(jì)人員的第二個(gè)選擇是X5R介電電容,因?yàn)樗哂谐錾姆€(wěn)定性。但是,X5R在封裝尺寸與電容特性方面可能會(huì)存在一定的限制。考慮去耦電容特性時(shí),低電感至關(guān)重要。

每個(gè)去耦電容都應(yīng)盡可能靠近要去耦的電源引腳。

所有去耦電容引線應(yīng)盡可能短。最佳做法是將電容直接連接到地以及頂層的電源引腳。如果不得不使用過(guò)孔,則焊盤(pán)到過(guò)孔的連接長(zhǎng)度應(yīng)小于10 mil。走線連接應(yīng)盡可能寬,以降低電感。

強(qiáng)烈建議考慮通過(guò)兩個(gè)過(guò)孔連接所有旁路電容的地,以極大地減小該連接的電感。

PCB旁路:

旁路電容應(yīng)放置在靠近PCB上所有電源入口點(diǎn)的位置。這些電容從高速數(shù)字負(fù)載吸收高頻電流。

設(shè)計(jì)中的所有電源連接和所有穩(wěn)壓器均應(yīng)使用旁路電容。

旁路電容的值取決于應(yīng)用,由電源的頻率以及負(fù)載瞬態(tài)幅值和頻率決定。

所有旁路電容引線應(yīng)盡可能短。最佳做法是將電容直接連接到地以及頂層的電源引腳。如果不得不在表面貼裝焊盤(pán)外使用過(guò)孔,則焊盤(pán)到過(guò)孔的連接長(zhǎng)度應(yīng)小于10 mil。走線連接應(yīng)盡可能寬,以降低電感。

強(qiáng)烈建議考慮通過(guò)兩個(gè)過(guò)孔連接所有旁路電容的地,以極大地減小該連接的電感。

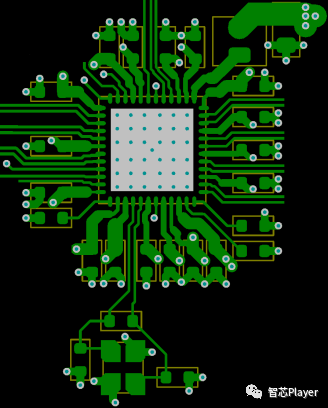

圖1 PCB旁路技術(shù)示例

PCB大電容:

必須適當(dāng)利用大電容,以將開(kāi)關(guān)噪聲降至最低。大電容有助于保持恒定的直流電壓和電流大小。

設(shè)計(jì)中的所有電源平面和穩(wěn)壓器均應(yīng)使用大電容。

旁路電容的值取決于應(yīng)用,由電源的頻率以及負(fù)載瞬態(tài)幅值和頻率決定。

所有大電容引線應(yīng)盡可能短。最佳解決方案是在表面貼裝焊盤(pán)內(nèi)使用平面連接過(guò)孔。在表面貼裝焊盤(pán)外使用過(guò)孔 時(shí),焊盤(pán)到過(guò)孔的連接長(zhǎng)度應(yīng)小于 10 mil。走線連接應(yīng)盡可能寬,以降低電感。

遵循良好的設(shè)計(jì)原則,只要在電路中使用鐵氧體磁珠,就應(yīng)在鐵氧體磁珠的每一側(cè)放置大電容。

如果在USB連接器上使用鐵氧體磁珠來(lái)對(duì)VCC 進(jìn)行濾波,則建議不要在USB連接器側(cè)使用大電容。這是限制USB 電路浪涌電流的一種嘗試。Microchip 強(qiáng)烈建議在鐵氧體磁珠內(nèi)側(cè)使用4.7 μF的大電容。

PCB層策略:

所有以太網(wǎng)LAN設(shè)計(jì)至少使用4層PCB。

在典型的 PCB 層疊結(jié)構(gòu)中,頂層(元件側(cè))為信號(hào),第2 層為固定連續(xù)地平面,第 3 層為固定電源平面,第4 層為 另一個(gè)信號(hào)。第 1 層被視為主要的關(guān)鍵布線和元件層,因?yàn)槠湔路绞枪潭〝?shù)字地平面。另外,第 1 層不需要通過(guò) 過(guò)孔來(lái)連接位于第 1層的元件。

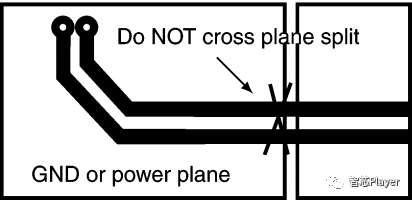

所有PCB走線(尤其是高速和關(guān)鍵信號(hào)走線)應(yīng)在固定連續(xù)地平面層相鄰的第 1層上布線。這些走線必須具有連續(xù) 的參考平面,才能滿(mǎn)足其整個(gè)傳導(dǎo)長(zhǎng)度的要求。應(yīng)避免信號(hào)走線穿過(guò)平面分割處(圖2),因?yàn)檫@會(huì)導(dǎo)致不可預(yù)測(cè) 的返回路徑電流, 并且可能引起信號(hào)完整性問(wèn)題以及產(chǎn)生EMI問(wèn)題。如果不得不穿過(guò)參考平面中的分割處,請(qǐng)考慮 添加拼接電容。

需要將以太網(wǎng)機(jī)架地平面與數(shù)字地平面分離。

避免在PCB設(shè)計(jì)和系統(tǒng)設(shè)計(jì)中形成接地回路。

為了便于布線并最大程度減少信號(hào)串?dāng)_問(wèn)題,多層設(shè)計(jì)中的相鄰層應(yīng)以正交方式布線。

圖2信號(hào)穿過(guò)平面分割處的示例

推薦的層疊布局

? 四層板

- 信號(hào) 1 (頂層)

- GND

- 電源平面/GND

- 信號(hào)2

? 六層板

- 信號(hào) 1 (頂層)

- 電源平面/GND

- 信號(hào)2(最適合時(shí)鐘和高速信號(hào))

- 信號(hào)3(最適合時(shí)鐘和高速信號(hào))

- GND

- 信號(hào)4

信號(hào)完整性問(wèn)題:

根據(jù)需要為所有高速開(kāi)關(guān)信號(hào)和時(shí)鐘線提供交流端接。在走線的負(fù)載端進(jìn)行上述端接。隨著PCB上走線長(zhǎng)度的增加,這一設(shè)計(jì)問(wèn)題變得更加關(guān)鍵。

提供阻抗匹配的串聯(lián)端接,以最大程度地減小關(guān)鍵信號(hào)(地址、數(shù)據(jù)和控制線)中的振鈴、過(guò)沖和下沖。這些串聯(lián)端接應(yīng)位于走線的驅(qū)動(dòng)器端,而不是走線的負(fù)載端。隨著PCB上走線長(zhǎng)度的增加,這一設(shè)計(jì)問(wèn)題變得更加關(guān)鍵。

盡量減少在整個(gè)設(shè)計(jì)中使用過(guò)孔。過(guò)孔會(huì)增加信號(hào)走線的電感。

請(qǐng)務(wù)必查看整個(gè)PCB設(shè)計(jì),了解是否有走線在任何參考平面切口上方穿過(guò)。這很有可能會(huì)引起EMC問(wèn)題。

通常,應(yīng)查看所有信號(hào)串?dāng)_設(shè)計(jì)規(guī)則以避免串?dāng)_問(wèn)題。確保走線間有足夠的間隔,以避免串?dāng)_問(wèn)題。

也可使用保護(hù)走線來(lái)最大程度地減少串?dāng)_問(wèn)題。

PCB走線注意事項(xiàng):

避免在高速數(shù)據(jù)走線中使用90度角。這類(lèi)角度會(huì)影響走線寬度和快速信號(hào)的阻抗控制。

要使 PCB 走線能夠提供所需電流量,應(yīng)為其設(shè)計(jì)合理的寬度。在頂層或底層的局部區(qū)域中使用迷你平面,這樣可確保提供足夠的電流。

連接任何電源平面或地平面的所有元件引線應(yīng)盡可能短。最佳解決方案是在表面貼裝焊盤(pán)內(nèi)使用平面連接過(guò)孔。在表面貼裝焊盤(pán)外使用過(guò)孔時(shí),焊盤(pán)到過(guò)孔的連接長(zhǎng)度應(yīng)小于10 mil。走線連接應(yīng)盡可能寬,以降低電感。這包括為電源層供電的任何鐵氧體磁珠以及為電源層供電的熔絲等。

晶振電路:

將所有晶振電路元件置于頂層。這將使所有這些元件及其走線以同一數(shù)字地平面為參考。

盡可能將所有晶振元件和走線與其他信號(hào)隔離。晶振對(duì)雜散電容和其他信號(hào)的噪聲敏感。晶振還可能干擾其他信號(hào)并引起EMI噪聲。

負(fù)載電容、晶振和并聯(lián)電阻應(yīng)靠近彼此放置。負(fù)載電容的接地連接應(yīng)較短,并遠(yuǎn)離USB和VBUS電源線的返回電流。負(fù)載電容的返回路徑應(yīng)連接到數(shù)字邏輯電源的地平面。

從以太網(wǎng)器件到晶振、電阻和電容的PCB走線應(yīng)在長(zhǎng)度上匹配,彼此應(yīng)盡可能靠近,同時(shí)保持最短的路徑。長(zhǎng)度匹配的優(yōu)先級(jí)應(yīng)高于最短的路徑長(zhǎng)度。

驗(yàn)證晶振電路在應(yīng)用的整個(gè)工作范圍內(nèi)工作時(shí)是否符合規(guī)范(+/-50 PPM)。這包括溫度、時(shí)間和應(yīng)用容差。

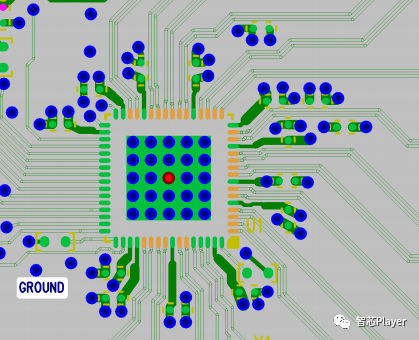

接地標(biāo)志(外露焊盤(pán))中的過(guò)孔:

在GND標(biāo)志上打滿(mǎn)過(guò)孔,以確保到地平面的熱連接和電氣連接良好。地平面應(yīng)為1 oz或更高值,以確保器件具有固定的GND參考。這將有助于降低GND噪聲并為器件提供理想的散熱效果。圖3給出了標(biāo)志焊盤(pán)中的接地過(guò)孔區(qū)示例。

圖3標(biāo)志焊盤(pán)中的接地過(guò)孔區(qū)示例 02

標(biāo)志焊盤(pán)中的接地過(guò)孔區(qū)示例

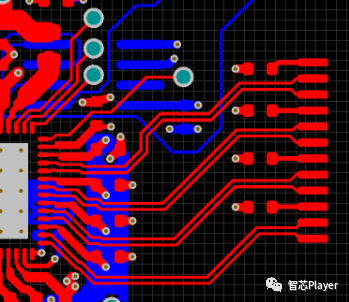

以太網(wǎng)差分對(duì):

每個(gè)TRxP/TRxN信號(hào)組都應(yīng)作為差分對(duì)布線。這包括從RJ45 連接器到LAN器件的整段走線。

單個(gè)差分對(duì)應(yīng)盡可能靠近布線。通常,在開(kāi)始計(jì)算阻抗時(shí),選擇最小的走線間距(4-5 mil)。然后調(diào)整走線寬度以 獲得必要的阻抗。

差分對(duì)應(yīng)構(gòu)造為 100?受控阻抗對(duì)。

差分對(duì)應(yīng)遠(yuǎn)離所有其他走線布線。嘗試使所有其他高速走線與以太網(wǎng)前端保持至少0.300英寸的距離。

確保器件與RJ45 之間的對(duì)內(nèi)和對(duì)間偏移分別小于50 mil和600 mil。

差分對(duì)的長(zhǎng)度應(yīng)盡可能短。

盡可能不要過(guò)孔。如果使用過(guò)孔,請(qǐng)保持最小值并始終匹配過(guò)孔,以便平衡差分對(duì)。

最大程度減少層變化。盡可能使差分對(duì)以相同的電源/地平面為參考。

通常,將千兆位以太網(wǎng)的四個(gè)差分對(duì)連接到RJ45連接器時(shí),至少有一對(duì)需要通過(guò)過(guò)孔連接到相對(duì)的外部層。在這種 情況下,必須確保電路板另一側(cè)(通常是第4層)上的布線經(jīng)過(guò)對(duì)地阻抗較低的連續(xù)參考平面。切勿越過(guò)平面邊界 布線。

為獲得最佳抗擾度,布線時(shí)盡可能使每個(gè)差分對(duì)互相遠(yuǎn)離。

端接應(yīng)始終使用與差分布線相同的參考平面。

應(yīng)先對(duì)差分對(duì)進(jìn)行布線。確定布線后再添加端接。只需將端接“放在”差分布線上即可。

以太網(wǎng)前端的所有電阻端接應(yīng)具有 1.0%容差值。

以太網(wǎng)前端的所有電容端接都應(yīng)具有嚴(yán)格的容差和高質(zhì)量的電介質(zhì)。

為了實(shí)現(xiàn)最佳分離效果,可以通過(guò)在差分對(duì)之間插入地平面孤島來(lái)進(jìn)行實(shí)驗(yàn)。應(yīng)使該地平面與任何走線的間距保持 為電解質(zhì)距離(PCB內(nèi)銅層的間距)的3至5倍。

如果存在端口串?dāng)_問(wèn)題,則可以使用上文所述的相同分離技術(shù)來(lái)分離不同的以太網(wǎng)端口。可以在以太網(wǎng)通道之間插 入地平面。應(yīng)使該地平面與任何走線的間距保持為電解質(zhì)距離的3至5倍。

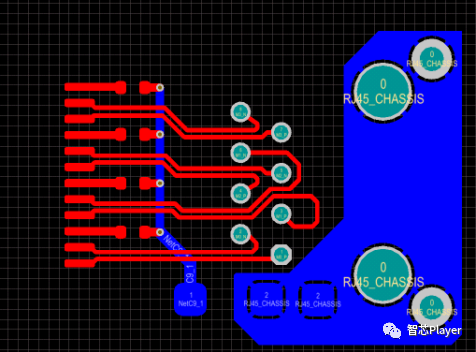

圖4芯片到磁件差分對(duì)布線示例

圖5磁件到RJ45差分對(duì)布線示例

RJ45連接器:

磁件能夠隔離本地電路和以太網(wǎng)信號(hào)連接的其他設(shè)備。IEEE 隔離測(cè)試在隔離側(cè)施加壓力,以測(cè)試隔離的介電強(qiáng)度。隔 離繞組的中心抽頭有一個(gè)“Bob Smith”端接, 通過(guò)75?電阻和 1000 pF電容連接到機(jī)架地。端接電容應(yīng)具有3 kV的電 壓容差。

要通過(guò)EMI兼容性測(cè)試,可參考以下實(shí)用建議:

建議將RJ45 連接器的金屬屏蔽層連接到機(jī)架地以減少EMI發(fā)射。

為了進(jìn)一步減少EMI 問(wèn)題,可以在適當(dāng)平面之間放置帶狀線來(lái)代替外層的微帶線。請(qǐng)注意,將帶狀線直接放在彼此 的頂部可能會(huì)導(dǎo)致通道之間出現(xiàn)電容耦合。不過(guò),對(duì)于差分對(duì),這種耦合可能是有益的。

最好不要使電路地平面與形成耦合的機(jī)架地重疊,而應(yīng)使機(jī)架地成為一個(gè)隔離孤島,并在機(jī)架地和電路地之間留出 空隙。在機(jī)架地和電路地空隙上放置兩到三個(gè)1206焊盤(pán)。這樣就能通過(guò)實(shí)驗(yàn)選擇合適的感性、容性或阻性元件,以 通過(guò)EMI發(fā)射測(cè)試。1206焊盤(pán)的位置應(yīng)盡可能靠近電路板上的電源入口,以使兩個(gè)地之間的電流遠(yuǎn)離任何敏感電路。

為了最大程度提高ESD 性能,設(shè)計(jì)人員應(yīng)考慮選擇不帶LED 的RJ45 模塊。這將簡(jiǎn)化布線并允許以太網(wǎng)前端中具有 更大的間隔,以改善ESD/敏感性性能。

此外,還可通過(guò)使用表面貼裝觸點(diǎn) RJ45 連接器來(lái)提高 ESD 性能。這可以簡(jiǎn)化布線并允許以太網(wǎng)前端中具有更大的 間隔,以改善ESD敏感性性能。

分立和嵌入式RJ45 和磁件模塊的元件放置:

以太網(wǎng)器件與磁件之間的距離應(yīng)小于 1英寸。如果無(wú)法實(shí)現(xiàn),則最大值不得超過(guò)3英寸。

磁件與RJ45 之間的距離應(yīng)小于 1英寸。

從以太網(wǎng)器件到RJ-45 連接器測(cè)得的差分對(duì)的總長(zhǎng)度應(yīng)小于4英寸。

磁件:

以太網(wǎng)的磁件可以是集成的,也可以是分立的。建議使用分立模塊以更好地控制EMI。

為了最大程度地提高ESD性能,設(shè)計(jì)人員應(yīng)考慮選擇分立變壓器,而不是集成磁件/RJ45模塊。這可以簡(jiǎn)化布線并 允許以太網(wǎng)前端中具有更大的間隔,以改善ESD/敏感性性能。

使用分立磁件時(shí), 務(wù)必使用端接:四個(gè) 75? 端接用于線纜側(cè)中心抽頭, 未使用的引腳連接到 EFT(電快速瞬變) 電容。

使用連接到地平面的EFT電容以及75?端接。建議值為 1500 pF/2 KV或 1000 pF/3 KV。電容與走線和元件的間距至少應(yīng)保持50 mil。

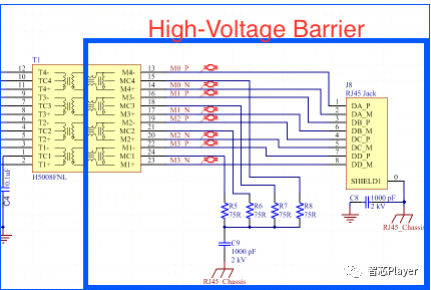

實(shí)現(xiàn)地分割以進(jìn)行高壓安裝(不需要集成磁件)。通常,在 PCB 上磁件到 RJ45 連接器的中間區(qū)域清除所有平面。TRxP/TRxN對(duì)應(yīng)是這一清除區(qū)域中僅有的走線,從而形成LAN應(yīng)用所需的高壓勢(shì)壘的一部分。

阻抗不連續(xù)會(huì)導(dǎo)致意外的信號(hào)反射。最大程度減少過(guò)孔(信號(hào)通孔)和其他不規(guī)則傳輸線的數(shù)量。如果必須使用過(guò) 孔,合理的做法是每段差分走線經(jīng)過(guò)兩個(gè)過(guò)孔。

ETHRBIAS/ISET:

ETHRBIAS/ISET電阻設(shè)置內(nèi)部參考電流源。因此,ETHRBIAS/ISET引腳是一個(gè)高阻抗節(jié)點(diǎn),在ETHRBIAS/ISET走線上 產(chǎn)生的任何噪聲都會(huì)直接影響內(nèi)部參考電流,從而對(duì)眼圖質(zhì)量造成負(fù)面影響。ETHRBIAS/ISET 電阻應(yīng)放置在靠近 ETHRBIAS/ISET引腳的位置,并且接地回路應(yīng)盡可能短且直接連接地平面。電阻走線應(yīng)非常短,并與附近的走線隔離。

03EMI注意事項(xiàng)

PCB EMI設(shè)計(jì)指南:

在原理圖和PCB設(shè)計(jì)周期中都必須考慮如何實(shí)現(xiàn)EMC設(shè)計(jì)。

最好從產(chǎn)生EMC的根源解決EMC 問(wèn)題。

標(biāo)識(shí)關(guān)鍵電路:

發(fā)射—— 時(shí)鐘、總線和其他重復(fù)電路。

?如果使用晶振,則確保熱引線盡可能短且匹配。

?向時(shí)鐘振蕩器添加較小的阻尼電阻或鐵氧體。

?控制時(shí)鐘布線

?當(dāng)心有噪聲的振蕩器模塊。

?如有可能,應(yīng)避免使用振蕩器。振蕩器會(huì)增加EMI、功耗和抖動(dòng)。

?如有可能,應(yīng)使用晶振。

抗擾度—— 復(fù)位、中斷和關(guān)鍵控制線。

?向電路輸入端添加高頻濾波器。

?控制走線布線。

?不要使高速信號(hào)走線穿過(guò)任何平面分割處。

謹(jǐn)慎選擇需要考慮EMI的器件:

越慢越好—— 上升時(shí)間和時(shí)鐘。

對(duì)于信號(hào)和電源,使用高速CMOS時(shí)需要小心。

電路板設(shè)計(jì):

多層板在發(fā)射和抗擾度方面的性能要出色得多。

不要在電源和地平面中嵌入走線。

密切注意電源去耦:

用高頻電容為每個(gè)器件去耦。

使用高頻電容旁路電路板的每個(gè)電源輸入。

電容引線應(yīng)盡可能短。

為了在超高速設(shè)計(jì)中改善噪聲和EMI,可以組合使用 0.1 μF、0.01 μF和容值更低的電容。

I/O電路注意事項(xiàng):

信號(hào)、電源和地是通過(guò)I/O的三個(gè)EMI路徑。

向所有I/O線路添加高頻濾波器,即使是慢速線路也是如此。

正確實(shí)現(xiàn)I/O平面的隔離。

04ESD注意事項(xiàng)

RJ45 連接器必須具有金屬屏蔽層,以確保最高的ESD性能。

RJ45 連接器的金屬屏蔽層必須直接連接到系統(tǒng)機(jī)架地平面的兩個(gè)點(diǎn)。

必須在磁件到RJ45 連接器的中間區(qū)域清除所有電源平面和非以太網(wǎng)走線。間隔至少應(yīng)保持0.250 英寸。

N/S和E/W磁件的固定方式不同;因此,磁件的選擇和位置對(duì)于ESD 性能至關(guān)重要。

正確布局高壓勢(shì)壘。

選擇帶有機(jī)架接地片的特定RJ45 連接器,并將它安裝在遠(yuǎn)離8引腳連接的位置,這已被證實(shí)是ESD的最佳配置。

RJ45 連接器相對(duì)于其他連接器和整個(gè)PCB的位置對(duì)于整體ESD性能非常重要。

確保與高壓勢(shì)壘區(qū)域相關(guān)和位于其中的所有電路僅以機(jī)架地為參考。高壓勢(shì)壘區(qū)域中的LED、電容和反并聯(lián)二極管 如果以數(shù)字地為參考,會(huì)對(duì)高壓勢(shì)壘帶來(lái)不利影響(見(jiàn)圖6)。

電源電壓線應(yīng)與其返回線緊密纏繞在一起。

PCB的所有電源入口都必須正確旁路,盡可能靠近PCB上的電源連接器。

接地連接應(yīng)遠(yuǎn)離敏感電路。這種策略將迫使ESD流遠(yuǎn)離敏感電路,并將其引向地。

整個(gè)設(shè)計(jì)中的所有信號(hào)走線均應(yīng)保持最短。考慮向長(zhǎng)度超過(guò) 12英寸的信號(hào)線添加數(shù)字地“保護(hù)走線”。

如果允許 ESD 進(jìn)入數(shù)字地平面,則可能導(dǎo)致數(shù)字接地層發(fā)生“接地反彈”。這可能導(dǎo)致意外的系統(tǒng)行為和/ 或系統(tǒng) 故障。應(yīng)盡一切努力確保不允許任何ESD源進(jìn)入PCB上的任何數(shù)字地或電源平面。

圖6高壓勢(shì)壘—— 延伸到磁件的中間位置

審核編輯:湯梓紅

-

pcb

+關(guān)注

關(guān)注

4367文章

23486瀏覽量

409538 -

以太網(wǎng)

+關(guān)注

關(guān)注

41文章

5631瀏覽量

175879 -

emi

+關(guān)注

關(guān)注

53文章

3750瀏覽量

131098 -

千兆以太網(wǎng)

+關(guān)注

關(guān)注

0文章

70瀏覽量

14067 -

PCB布線

+關(guān)注

關(guān)注

22文章

472瀏覽量

42731

發(fā)布評(píng)論請(qǐng)先 登錄

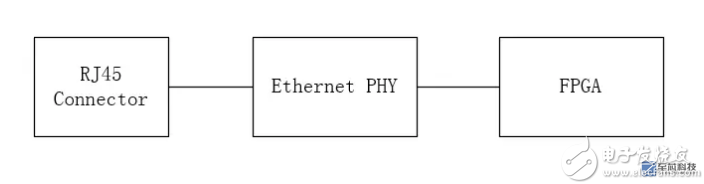

簡(jiǎn)談基于FPGA的千兆以太網(wǎng)

簡(jiǎn)談基于FPGA的千兆以太網(wǎng)

簡(jiǎn)談基于FPGA的千兆以太網(wǎng)設(shè)計(jì)

千兆比以太網(wǎng)交換機(jī)設(shè)備技術(shù)規(guī)范

ATM與千兆以太網(wǎng)的區(qū)別

以太網(wǎng)的傳播速率_以太網(wǎng)的傳輸介質(zhì)

千兆以太網(wǎng)傳輸速率_千兆以太網(wǎng)物理層標(biāo)準(zhǔn)

千兆以太網(wǎng)發(fā)展現(xiàn)狀_千兆以太網(wǎng)前景

以太網(wǎng)技術(shù)聯(lián)盟發(fā)布了800千兆位以太網(wǎng)的規(guī)范

千兆以太網(wǎng)發(fā)展現(xiàn)狀 千兆以太網(wǎng)技術(shù)優(yōu)勢(shì)

FPGA如何為以太網(wǎng)和千兆以太網(wǎng)解決低功耗問(wèn)題

千兆以太網(wǎng)設(shè)計(jì)指南

千兆以太網(wǎng)設(shè)計(jì)指南

評(píng)論