點擊藍字關注我們

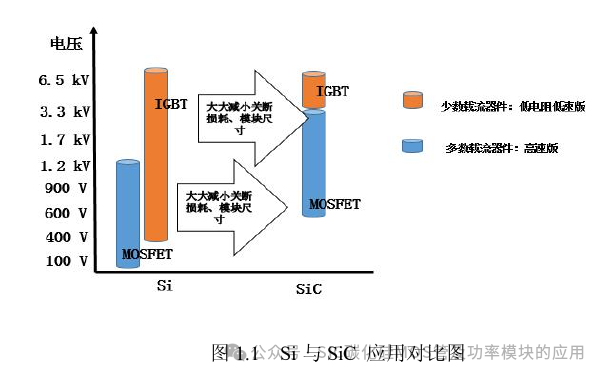

對于高壓開關電源應用,碳化硅或SiC MOSFET與傳統硅MOSFET和 IGBT相比具有顯著優勢。SiCMOSFET很好地兼顧了高壓、高頻和開關性能優勢。它是電壓控制的場效應器件,能夠像IGBT一樣進行高壓開關,同時開關頻率等于或高于低壓硅MOSFET的開關頻率。之前的文章中,我們介紹了SiCMOSFET特有的器件特性和如何優化SiC柵極驅動電路。今天將帶來本系列文章的第三部分SiC MOSFET的封裝、系統性能和應用。

封裝

WBG半導體使高壓轉換器能夠在更接近低壓轉換器(低于100V)開關頻率的情況下工作。對于低壓轉換器而言,半導體封裝的發展對當今開關性能的實現起到了關鍵作用。硅MOSFET封裝取得了進步,例如雙面散熱、夾焊、熱增強功率封裝和低電感、無引線封裝。同樣,柵極驅動器IC封裝也“瘦身”明顯。更短的芯片到引線、鍵合線連接,加上模制無引線封裝(MLP),對于最大限度地減少驅動器側的寄生電感至關重要。驅動器和MOSFET(DrMOS)共封裝是減少寄生電感、提高效率和縮小電路板面積的最新步驟。DrMOS得以實現也是因為引入了類似低壓轉換器應用中所使用的封裝改進措施。

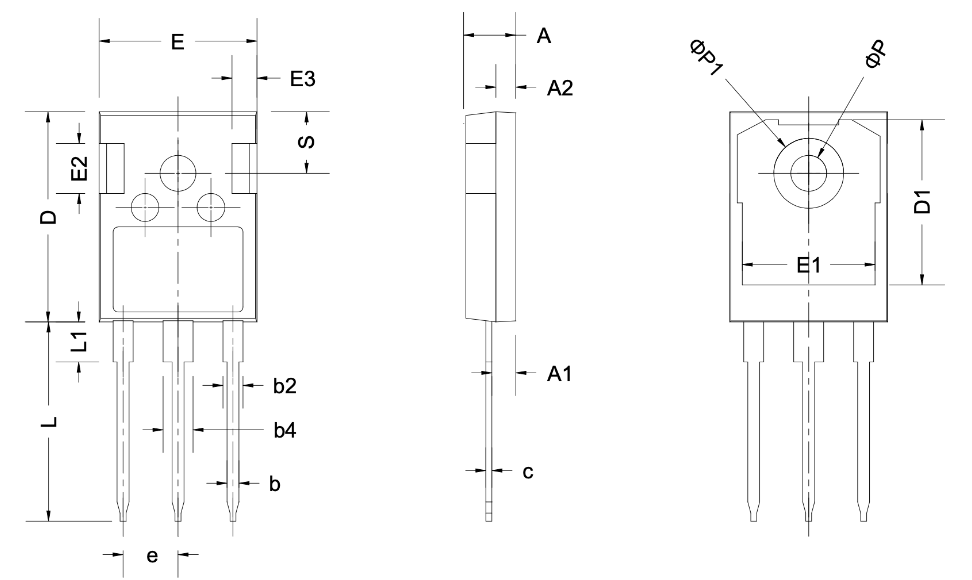

在高壓轉換器領域,爬電距離和電氣間隙等最小間距要求使得高性能 SiC MOSFET依然采用低性能To?220型和To?247型封裝。這些封裝已經十分完善,長期以來一直是行業標準。它們非常適合工業應用,堅固且易于散熱,但其長引線和內部鍵合線導致寄生電感更高。SiC MOSFET現在使這些寄生電感受到熱應力、頻率和dV/dt速率的影響,以前在高壓硅晶體管中,這是從未設想到的。可以說,SiC促進了對高壓分立封裝的重新思考。

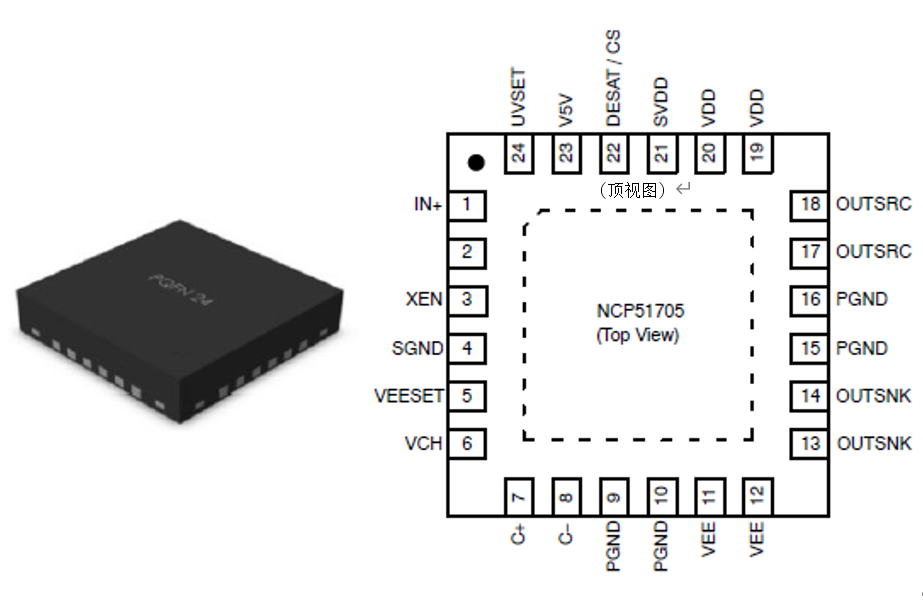

不像分立器件,SiC柵極驅動器能夠充分利用那些原本用于低壓電源轉換器的驅動器件的封裝改進。NCP5170芯片封裝成24引腳、4x4 mm、熱增強MLP,如圖15所示。

圖15.NCP51705 24引腳、4x4mm、MLP封裝和引腳輸出

所有高電流電源引腳都布了兩個,位于IC的右半部分。此外,這些引腳都通過內部雙鍵合線連接到芯片,以實現盡可能最低的電感。所有低功耗數字信號僅為單引腳,位于IC的左半部分,為PWM或數字控制器提供了方便、直接的接口。

NCP51705封裝的底部包括一個電絕緣、導熱、暴露的焊盤。該焊盤未連接到PGND或SGND,但會通過熱通孔連接到隔離銅PCB焊盤進行散熱。

如果散熱成為一個問題,應特別注意四個主要的功耗因素:

-

與驅動外部SiC MOSFET相關的OUTSRC和OUTSNK損耗。這些是與開關頻率成比例的柵極電荷相關損耗。降低開關頻率將降低功耗;

-

VDD和V5V之間的LDO,能夠提供高達20mA的電源。切勿加載V5V到其他負載,電壓軌僅用于數字隔離器或光耦合器的偏壓

-

VDD和VCH之間的LDO,這是內部電荷泵的一部分

-

內部電荷泵電源開關,可禁用并用外部負偏壓替換,如電荷泵—VEE(VEESET)部分所述

系統性能

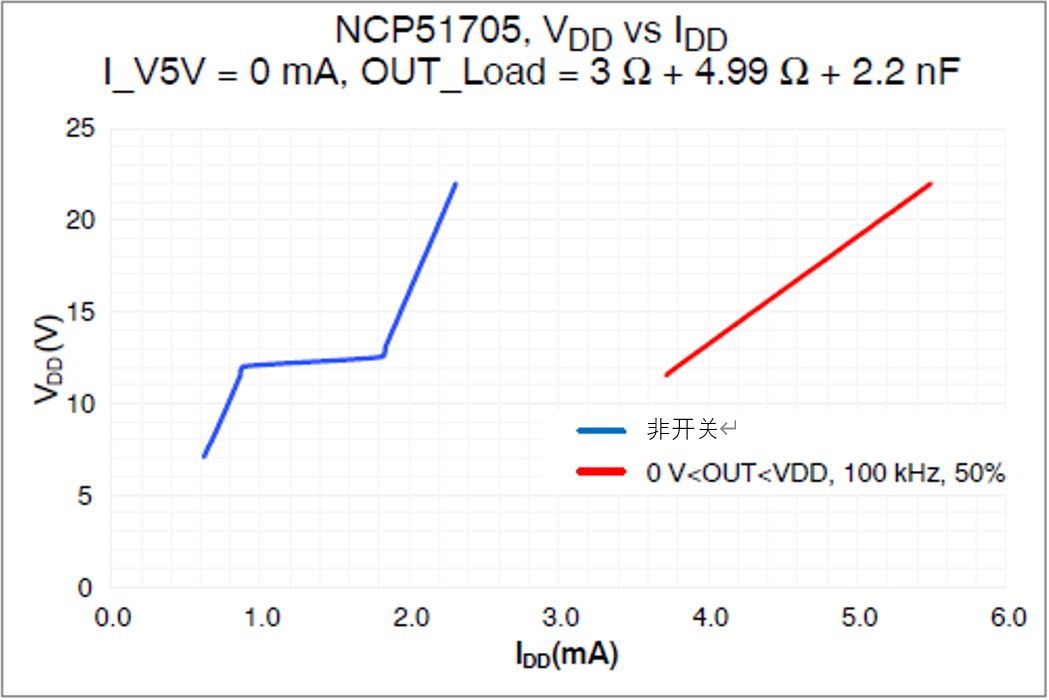

對于VDD>7V,靜態電流線性緩升,直至超過設置的UVLO閾值。圖16所示的藍色曲線表示在沒有PWM輸入信號并且VDD(UVLO)=12V,V5V調節器無負載的情況下,VDD相對于IDD的變化曲線。對于7V

紅色曲線表示在禁用內部電荷泵的同時向IN+施加100kHz、50%占空比脈沖輸入的情況。使用4.99Ω+2.2nF負載,這是典型SiC MOSFET的等效輸入阻抗。外部灌拉電阻為3?。對于12V

圖16.VDD與IDD,非開關與開關

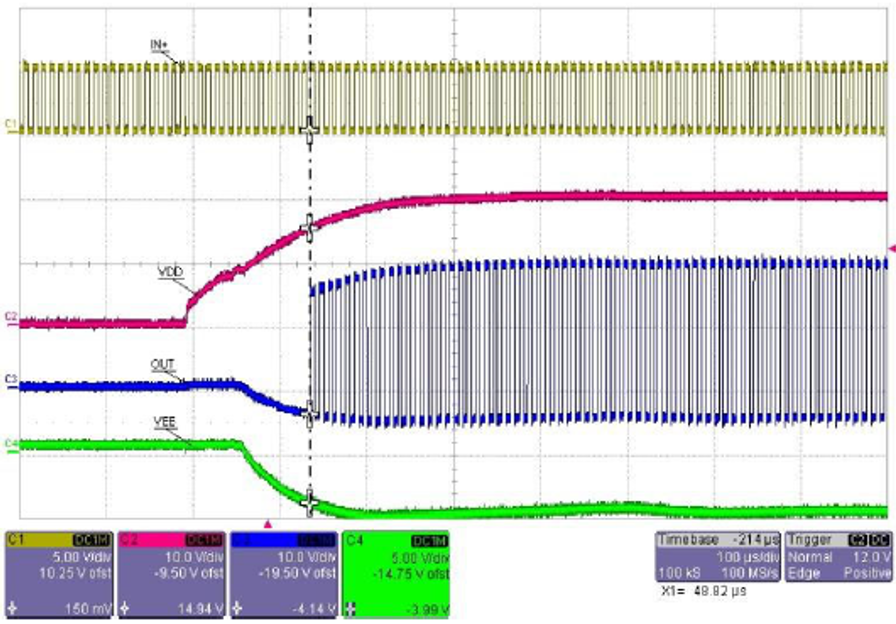

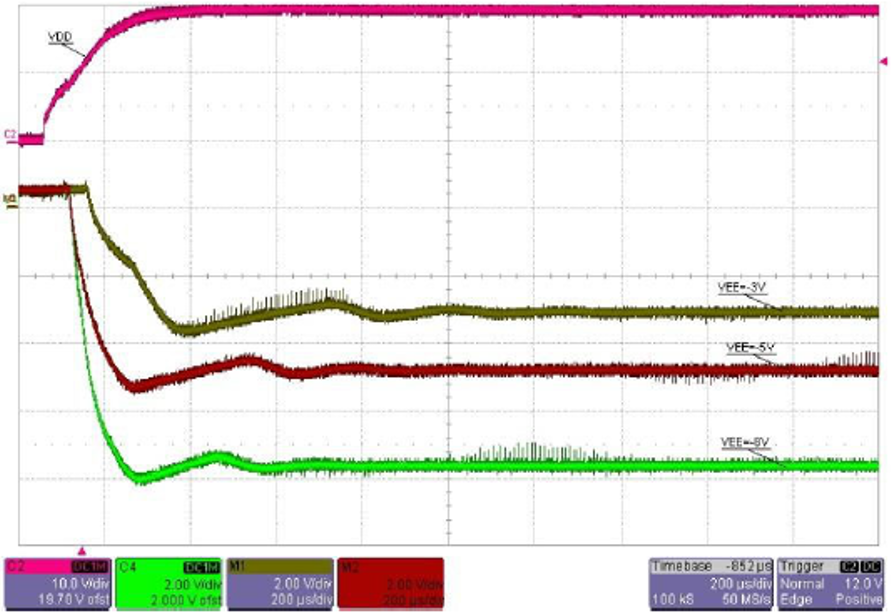

圖17所示的啟動波形顯示了在VDD之前已經輸入了PWM信號到IN+。VDD從0V上升至20V,UVSET=2V(未在圖中顯示),相當于VDD(UVLO)=12V。VEE被設置為在?5V調節,VEESET=V5V(未在圖中顯示),相當于VEE(UVLO)=?4V。當VEE=?4V時,輸出便會使能,此時VDD>12V(VDD=15V)。還要注意,在近100μs的時間內,OUT(VGS)小于20V。根據VDD爬升的dV/dt速率,該時間可能更長,因此,在編程UVSET時應考慮SiC MOSFET的熱應力。

圖17.CH1-IN+、CH2-VDD、CH3-OUT、CH4-VEE;

VDD(UVLO)=12V,VEE(UVLO)=-4V

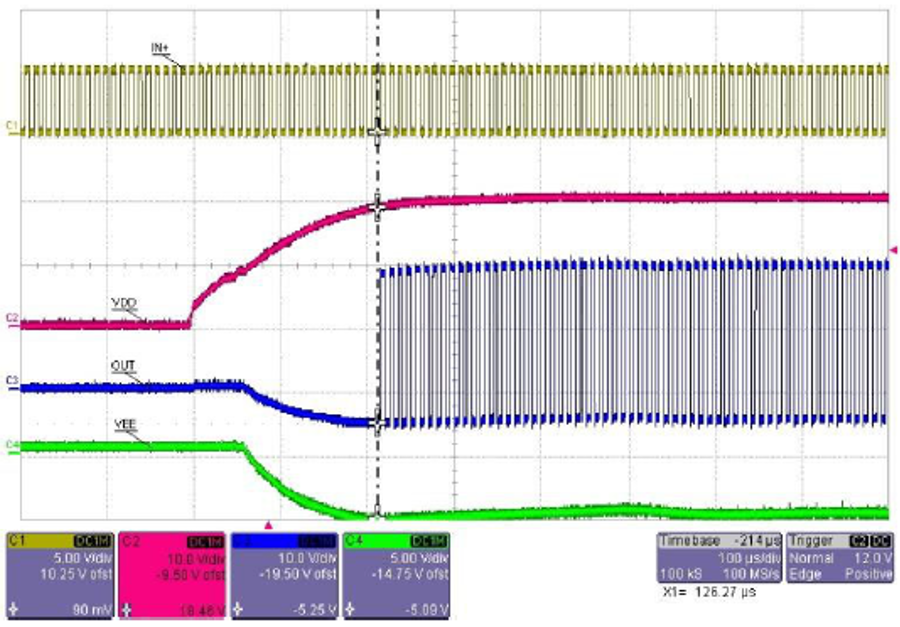

圖18中顯示了相同的啟動波形,但UVSET=3V(未顯示),相當于 VDD(UVLO)=18V。在這種情況下,當VDD=18V時,OUT(VGS)便會啟用,此時VEEEE=?5V)。哪個UVLO占優勢取決于VDD與VEE的dV/dt速率。關鍵點是NCP51705輸出被禁用,直到VDD和VEE都高于或低于各自的UVLO閾值。與圖17相比,請注意較高的UVLO設置對 OUT(VGS)的影響,其中第一個OUT脈沖出現在20V和?5V附近。

圖18.CH1-IN+、CH2-VDD、CH3-OUT、CH4-VEE;

VDD(UVLO)=18V,VEE(UVLO)=-4V

NCP51705內部電荷泵有一個緩慢的控制回路,其效果可從VEE啟動期間觀察到的輕微下沖和<400μs的穩定時間中看出,如圖19所示。超過400μs時,VEE電壓穩定至?3V、?5V或?8V的調節設定值。

圖19.VEE啟動

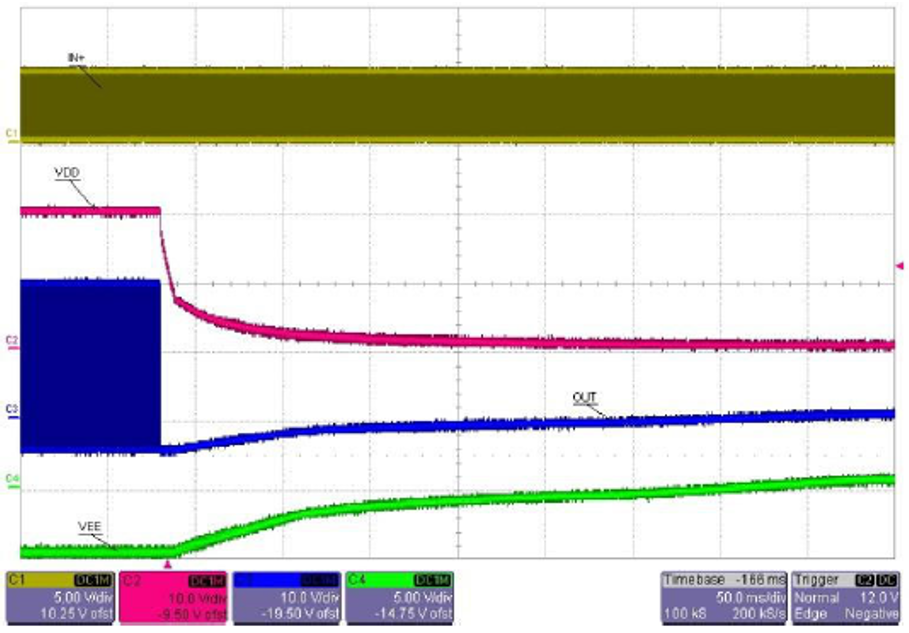

關機操作平穩,無毛刺。如圖20所示,OUT停止開關并跟蹤掉電的 VEE。VEE從?5V到0V的放電時間約為300ms。

圖20.CH1-IN+、CH2-VDD、CH3-OUT、CH4-VEE;關閉

圖21顯示了圖20中時間基準的放大圖。UVSET被配置為3V(VDD(UVLO)=18V),內部VDD UVLO遲滯在內部固定為1V。當輸出被禁用時,光標位置顯示VDD=17V(18V?1V滯后),此時VEE=?4.5V(VEESET=V5V),并且根據其?4V UVLO仍處于有效電壓范圍。盡管VDD的衰減很慢,但在UVLO_OFF之后,也可以看到最后一個輸出脈沖的終止很干凈,沒有雜散脈沖或毛刺。

圖21.CH1-IN+、CH2-VDD、CH3-OUT、CH4-VEE;

關閉,VDD_UVLO(OFF)=17V

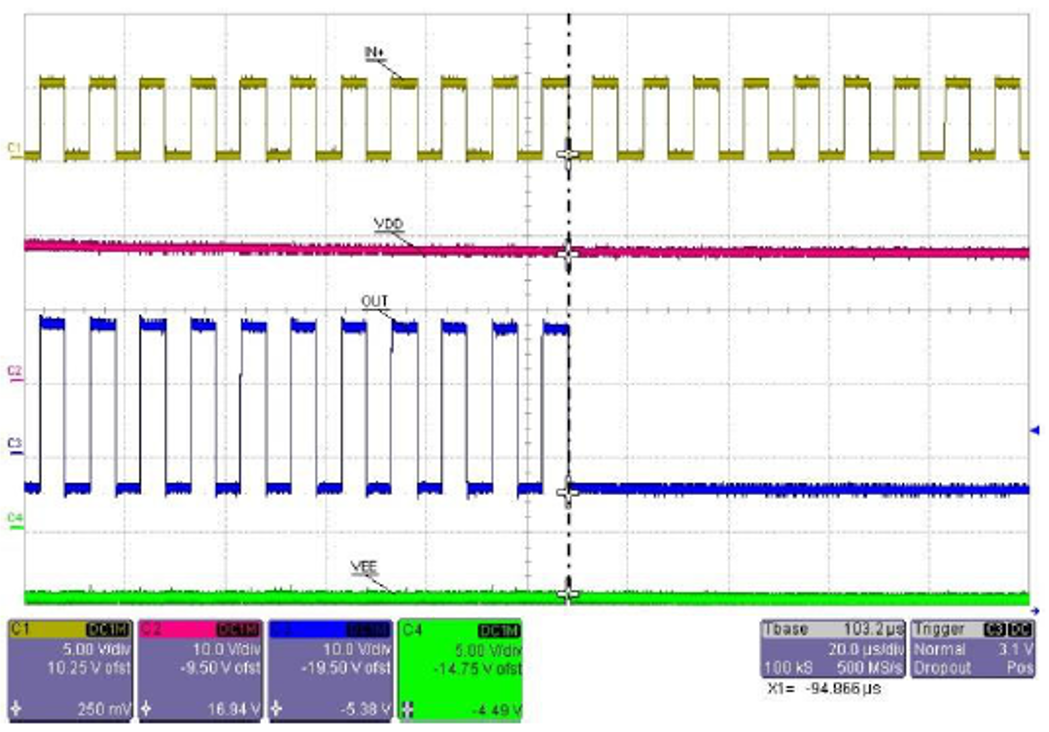

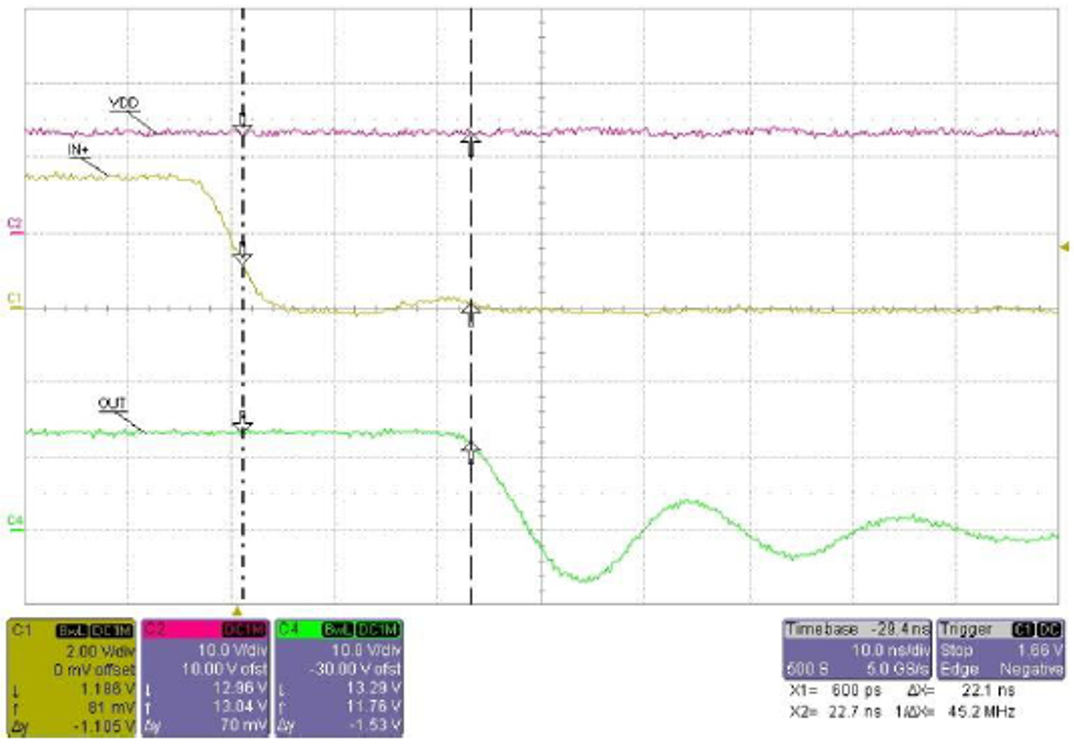

導通傳播延遲的測量范圍從90%IN+上升至10%OUT上升。通常SiC 驅動器將在更高的VDD下工作,但大多數SiC MOSFET傳播延遲被指定為VDD=12V,1nF負載條件下的測得。圖22顯示了在這些標準測試條件下測得的導通傳播延遲為19ns。

圖22.CH1-IN+、CH2-VDD、CH4-OUT;上升沿傳播延遲

同樣,關斷傳播延遲的測量范圍從10%IN+下降至90%OUT下降。圖23顯示了在相同標準測試條件下測得的關斷傳播延遲為22ns。每個邊緣的輸出上升和下降時間約為5ns。

圖23.CH1-IN+、CH2-VDD、CH4-OUT;下降沿傳播延遲

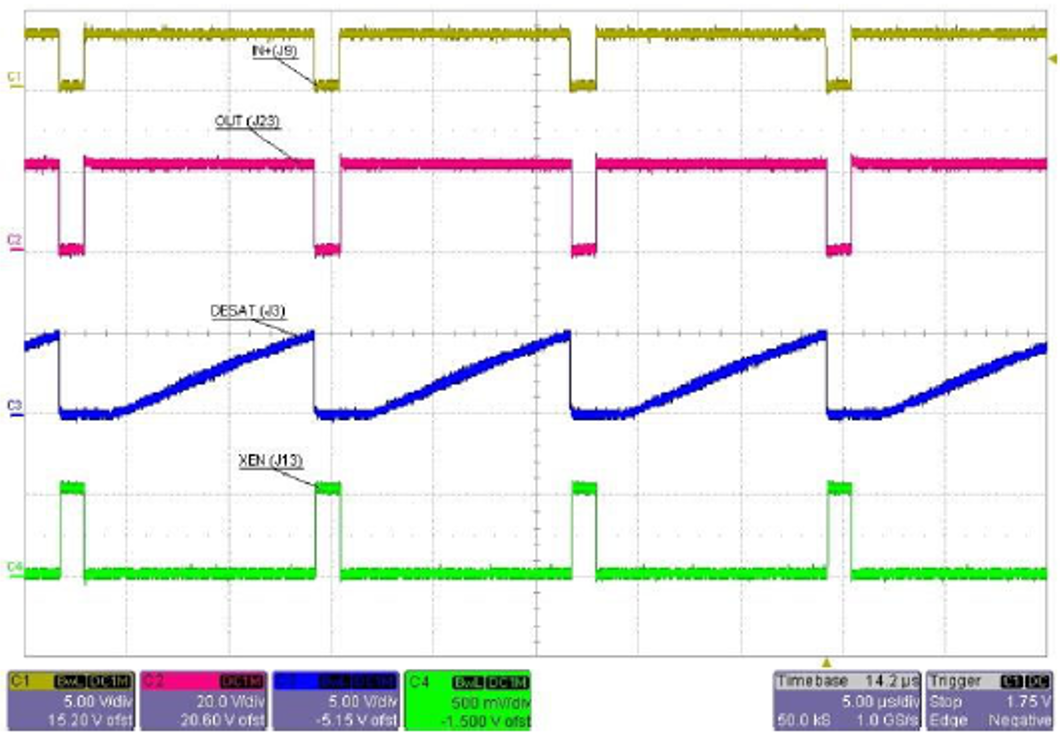

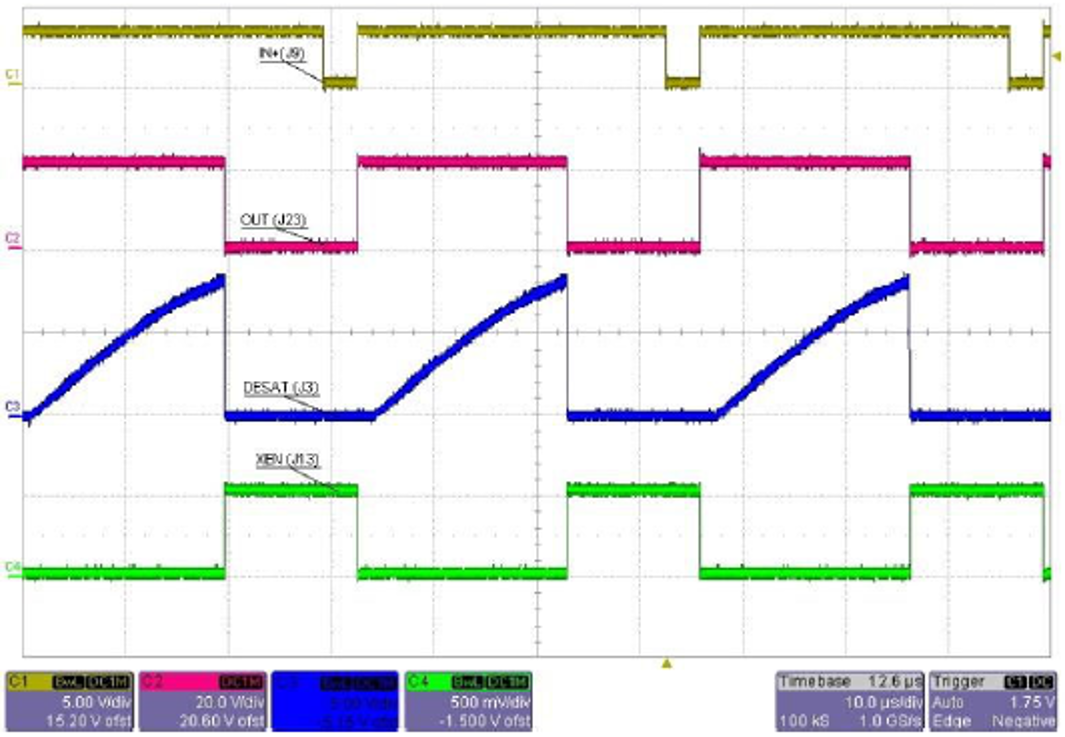

DESAT和XEN波形分別如圖24和圖25所示。由于測試僅用于IC驗證(無功率器件級),因此將100pF固定電容連接到DESAT引腳。圖24所示的波形表明DESAT低于7.5V閾值,輸出在正常操作下切換。如果IN+頻率降低(導通時間增加),則100pF DESAT電容將可以充電至更高的電壓。如圖25所示,DESAT電壓已達到7.5閾值。輸出后沿在輸入電壓切換為低之前終止。DESAT小斜坡用于強調終止的OUT脈沖上沒有出現毛刺的事實。在開關電源應用中,DESAT引腳上可以使用小型(<100pF)外部電容進行高頻噪聲濾波。

XEN信號與OUT信號相反。無論驅動器是正常運行還是面臨DESAT故障,XEN信號都能準確跟蹤任一情況下的反向OUT信號。

圖24.CH1-IN+、CH2-OUT、CH3-DESAT、CH4-XEN;VDESAT<7.5V

圖25.CH1-IN+、CH2-OUT、CH3-DESAT、CH4-XEN;VDESAT=7.5V

應用

SiC MOSFET可以適用于目前使用IGBT的各種應用場景。一些較常見的用途包括高壓開關電源、混合動力和電動汽車充電器、電氣化鐵路運輸、焊機、激光器、工業設備及其他注重高溫操作的環境。尤其值得一提的兩個領域是太陽能逆變器和高壓數據中心。更高的直流電壓有利于減小線規厚度、接線盒、互連,并最終最大限度地減少導通損耗,從而提高效率。目前,大多數大型光伏系統均采用1kV直流母線,未來趨向于采用1.5kV總線。同樣,使用380V配電網絡的數據中心可以將直流電壓提升至800V。

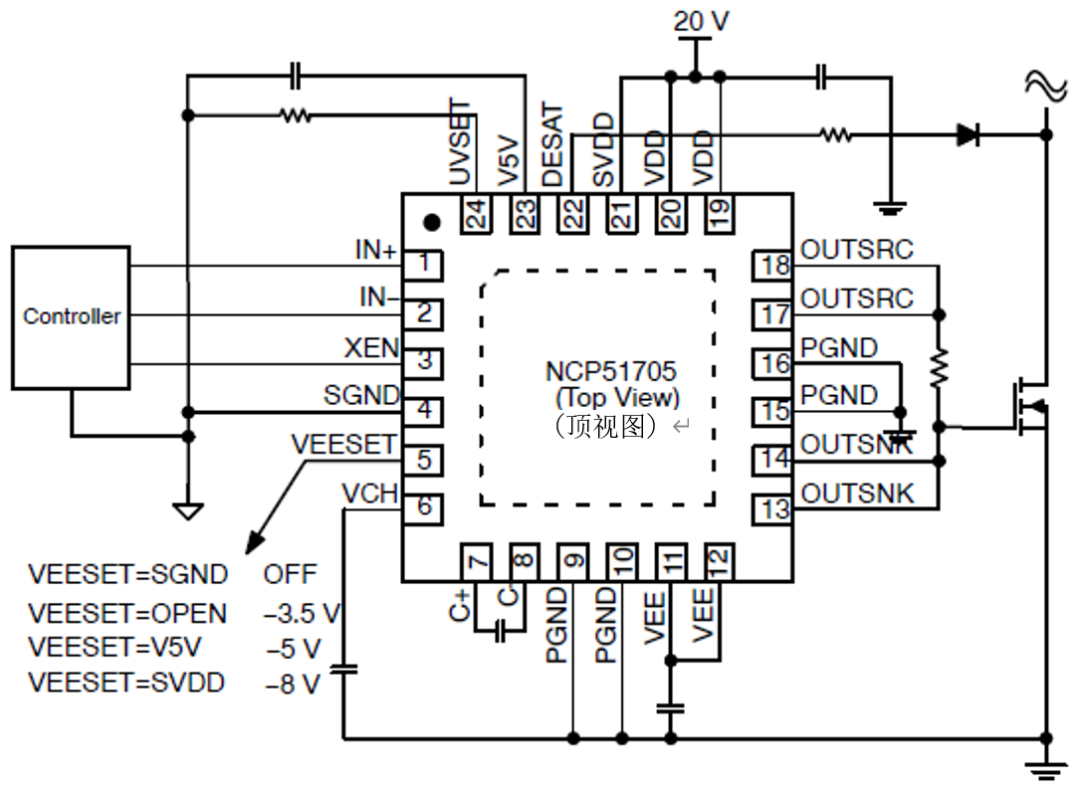

NCP51705的幾個基本應用示例如下所示。

低邊開關圖26顯示了用于低邊開關應用的NCP51705的頂層原理圖。未顯示隔離,因此控制器和驅動器之間為直連接口,不是所有應用都是非隔離架構。此原理圖旨在說明,要提供全功能、可靠和穩健的SiC柵極驅動電路,只需甚少的外部組件。還應提及,盡管只需要單一VDD電壓軌,但其共模瞬態抗擾度額定值應至少為50V/ns,以防止分立式SiC柵極驅動部分中的分立式柵極驅動說明所述的雜散電流脈沖。如果 VDD電壓軌由專用輔助電源提供,則應特別注意設計具有超低原-副邊 雜散電容的變壓器。

圖26.低邊開關示例

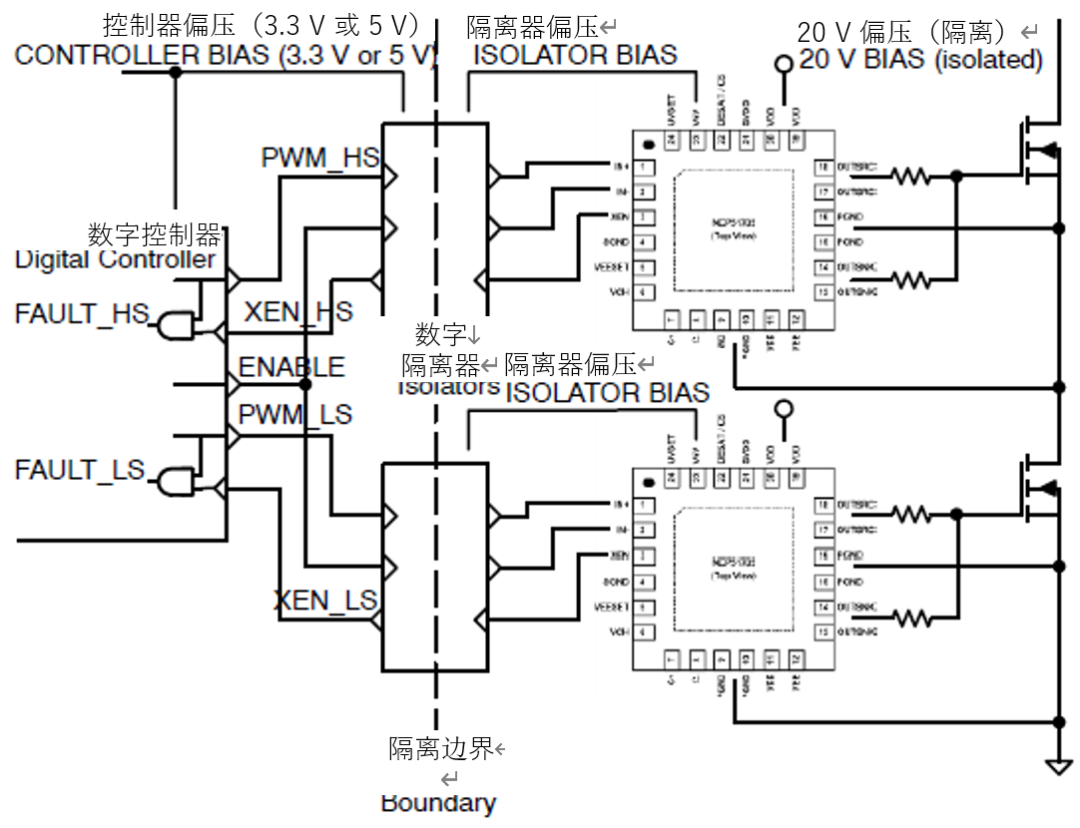

半橋概念

在半橋電源拓撲中可以找到SiC MOSFET更普遍的用途,如圖27所示。高功率應用傾向于在高邊和低邊都使用隔離驅動器。這意味著需要兩個數字隔離器。根據跨越隔離邊界的IO接口的數量,此類應用的次級側控制可能存在很大爭議。在這個簡化示例中,In+和In-(使能)是來自數字控制器的僅有的兩個信號,XEN從NCP51705讀取。XEN可以作為開發柵極驅動時序、交叉導通預防、死區時間調整和故障檢測的時序信息基準。此外,溫度感測、熱管理(風扇控制)和更高級別的故障響應也可以由數字控制器完成。NCP51705的V5V可用于為每個數字隔離器的次級側供電,如圖27所示。

圖27.半橋概念

準諧振(QR)反激式

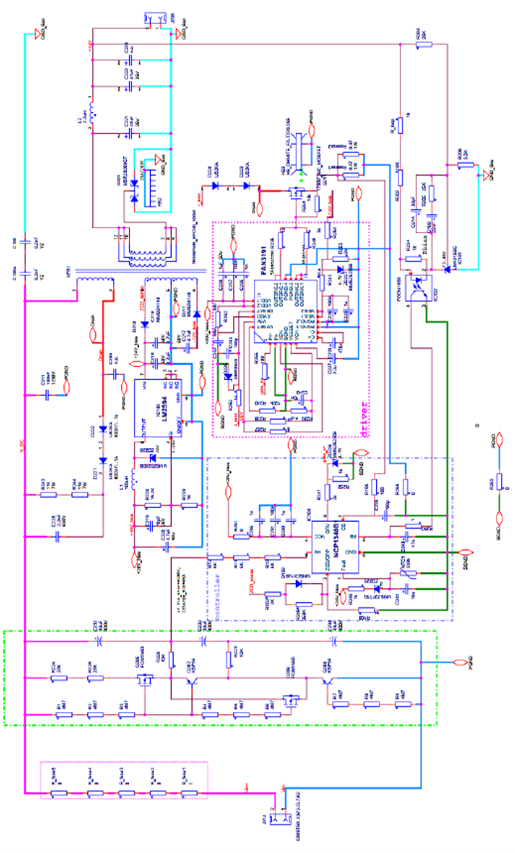

使用NCP1340B1控制器和NCP51705 SiC驅動器設計了一個100W的QR反激式轉換器,可在300V

圖28.1000V至24V、100W、400kHz、QR反激式

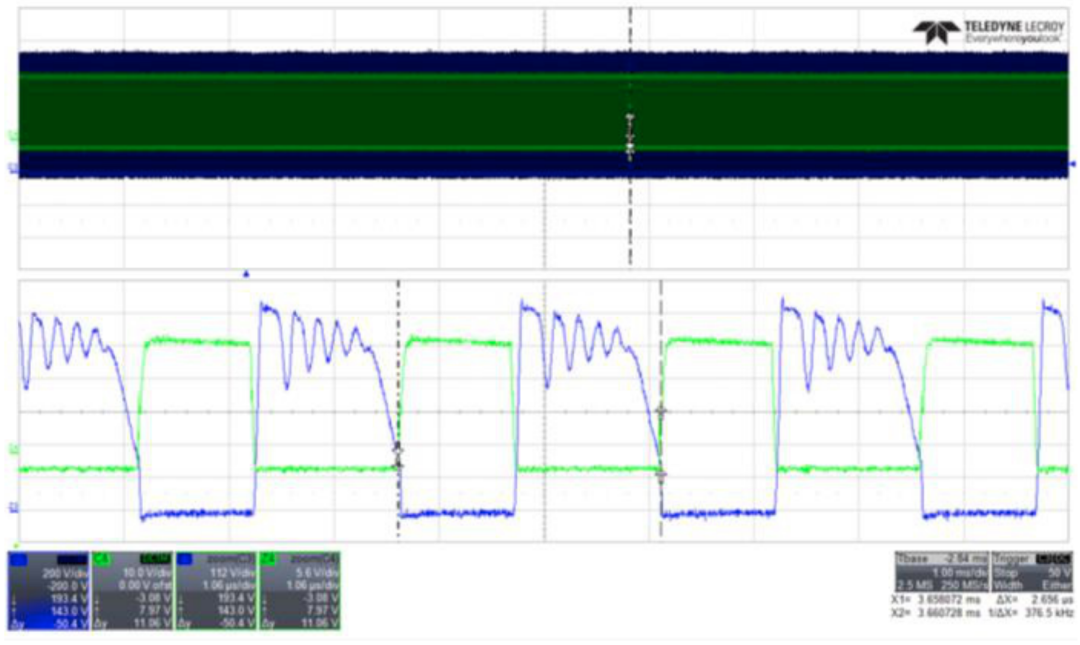

對于VIN=300V,漏極-源極電壓波形是輸入電壓和反射輸出電壓之和。圖29所示的波形突出顯示了在全占空比操作(VIN=300V)下運行的轉換器,其中SiC MOSFET的漏極-源極電壓為720V。VDS上升過渡約為30ns,相當于dVDS/dt=24V/ns。NCP1340B1 QR控制在VDS下降沿實現軟諧振過渡和谷底開關(在VDS諧振到最小值時“接近 ZVS”導通),可以在藍色波形上清晰看到這一操作過程。由于QR反激式是僅限低邊開關的應用,并且dVDS/dt下降沿為諧振,因此SiC MOSFET可能在0V

圖29.CH3=VDS,CH4=VGS;VIN=300V,VOUT=24V,

IOUT=4A,FS=377kHz

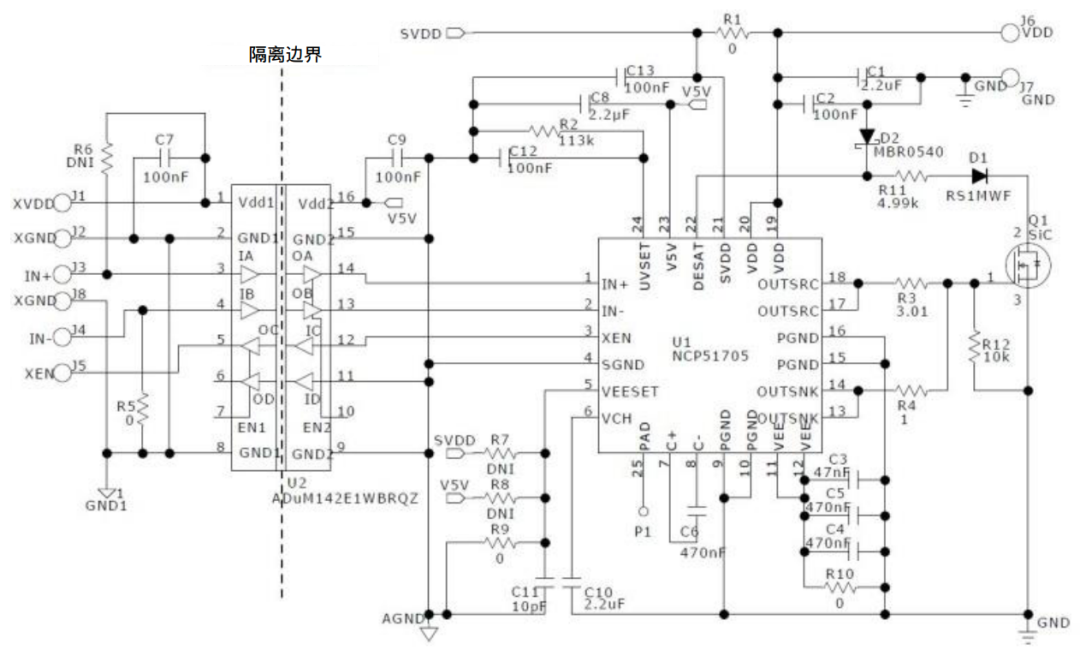

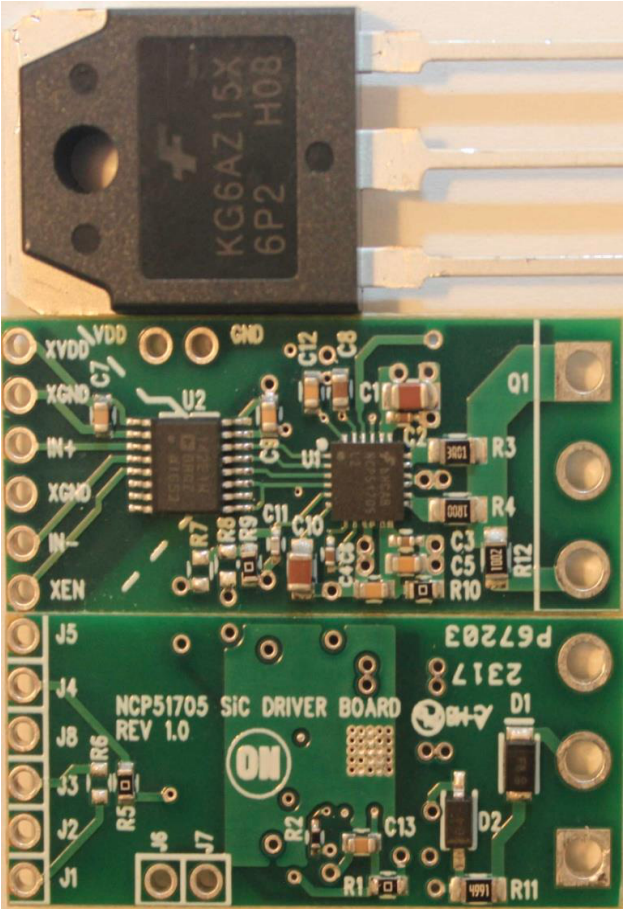

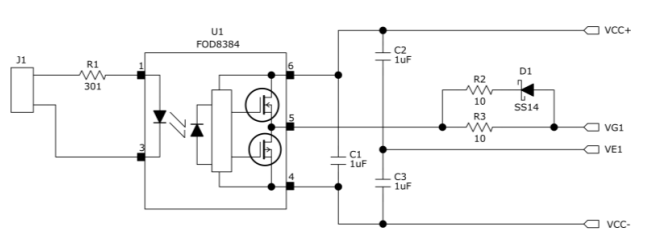

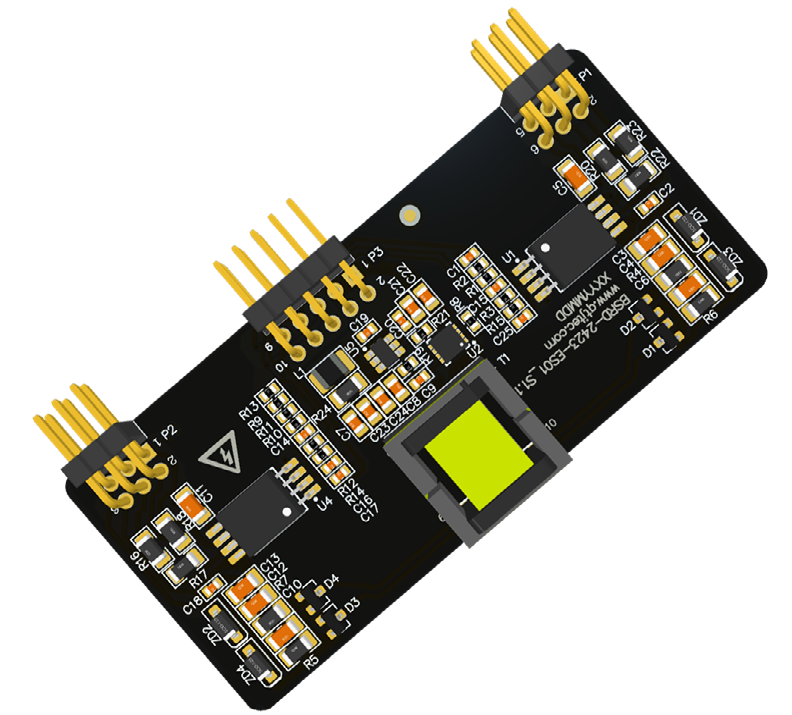

通用NCP51705客戶EVB通用評估板(EVB)旨在評估NCP51705在新設計或現有設計中的性能。EVB不包括功率級,不專用于任何特定拓撲,由此可見它是通用的。它可用于任何低邊或高邊電源開關應用。對于橋接配置,可以用兩個或者多個EVB組成圖騰柱結構來驅動每個SiC MOSFET。EVB可被視為隔離器+驅動器+TO-247分立模塊。EVB原理圖如圖30所示。

重點是提供一種超緊湊的設計,其中TO-247 SiC MOSFET的引線可以直接連接到印刷電路板(PCB)。圖31同時顯示了相鄰TO-247封裝旁邊的EVB的頂視圖和底視圖進行尺寸縮放。

圖30.NCP51705 Mini EVB原理圖

圖31.NCP51705 Mini EVB-頂視圖(35mmx15mm)

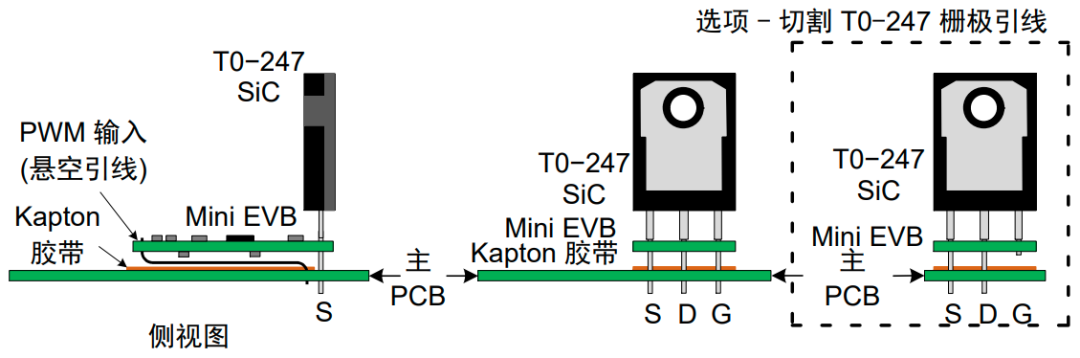

當安裝到現有電源設計中,并且TO-247前面有可用的PCB區域時,EVB可以水平安裝到主電源板上,如圖32所示。如果可能,這應該是首選的安裝方法。

圖32.水平EVB安裝

如果主電源板上的大型組件妨礙水平安裝,則第二種選擇是垂直安裝EVB,使其與T0-247封裝平行或略微傾斜。由于驅動器與TO-247漏極接頭發出的高dV/dt非常接近,因此不太傾向于采用這種方式安裝。在任何一種情況下,TO-247封裝的后接頭都保持暴露狀態,如有必要,可將其連接到散熱片上。有關安裝和操作詳細信息,請參見EVB用戶指南。

圖33.垂直EVB安裝

EVB最初配置為接受正輸入邏輯的PWM信號(連接到GND1的 IN-)。但如果需要,IN-可輕松用作主動啟用或重新配置為反相輸入邏輯。驅動器輸出預配置為0V

參數性能

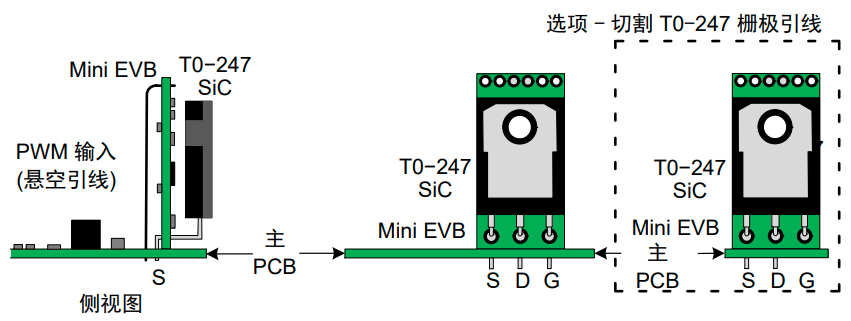

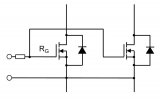

使用眾所周知的雙脈沖測試平臺對MOSFET和IGBT進行參數化表征。雙脈沖測試方法基本會向被測器件(DUT)低邊SiC MOSFET的柵極-源極施加兩個脈沖。DUT被插入到與圖34所示的鉗位電感開關電路相連的插座中。

圖34.雙脈沖測試電路和波形

調整第一個脈沖的導通時間,以獲得所需的峰值漏極-源極電流。電感器很大,關斷時間足夠短,因此IL1在關斷續流期間幾乎保持恒定。因此,第二個更短的脈沖以相同的漏極-源極電流幅度施加。該測試方法可精確控制ID和VDS,這是建立動態開關、參數性能以及對器件進行對比測試所必需的。

雙脈沖測試方法也可用于表征柵極驅動器性能。在SiC、DUT固定的情況下,可以有各種柵極驅動電路組成U1成為新的“DUT”。在圖30和圖31所示的NCP51705 EVB和圖35所示的簡單光耦合器柵極驅動電路之間,對dV/dt和dI/dt開關性能進行了比較。

圖35.FOD8384 SiC光耦合器柵極驅動電路

FOD8384光耦合器驅動器能夠承受高達30V的VDD偏壓,因此非常適合-5V

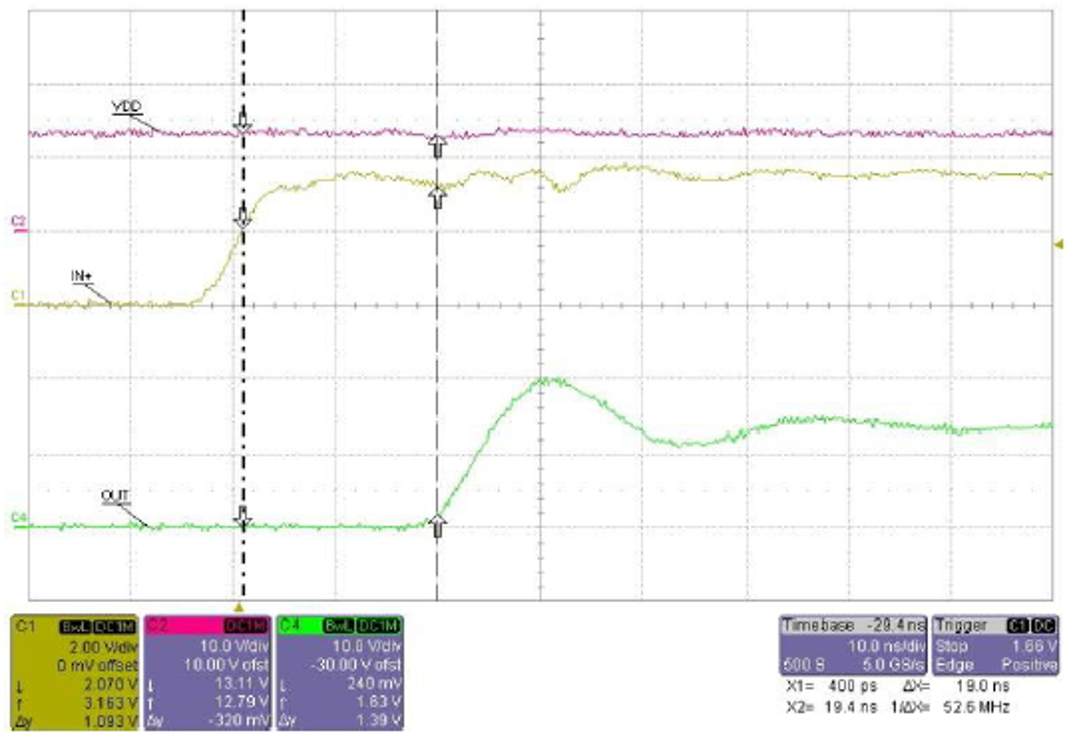

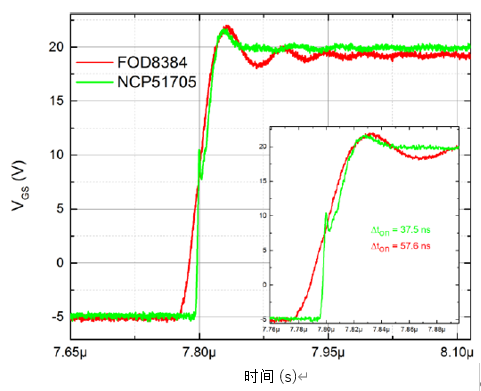

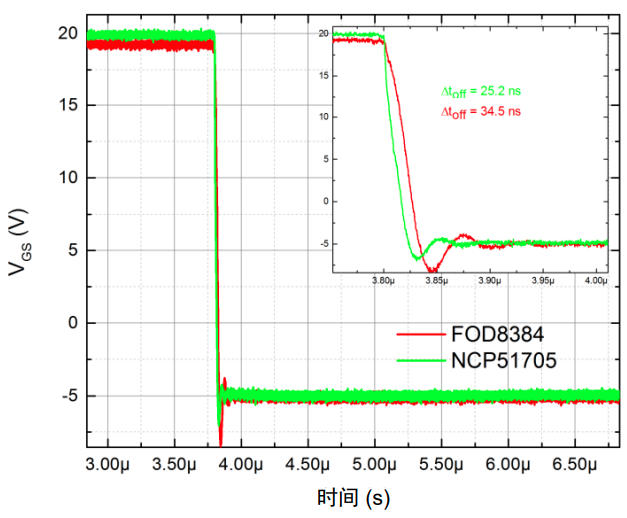

圖36和圖37分別顯示了兩種電路的上升和下降VGS波形,以供比較。兩種電路都使用了1Ω的灌和拉電阻。這些柵極驅動邊緣被顯示為驅動1.2kV的SiC MOSFET,VDS上電壓為600V,流過ID的電流為30A。NCP51705、VGS上升沿在?5V

圖36.VGS上升沿比較

圖37.VGS下降沿比較

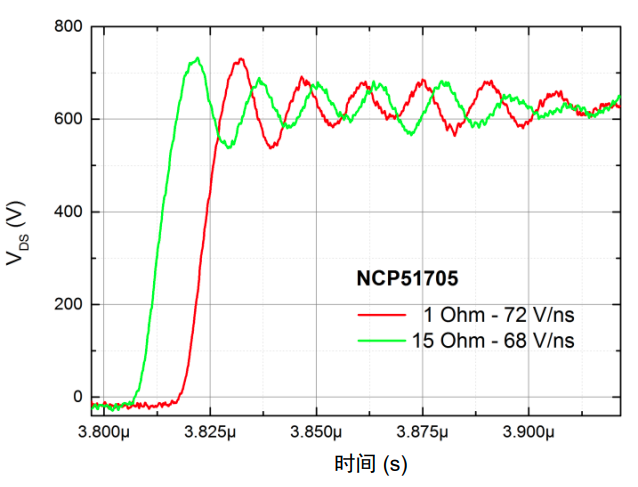

設計良好的柵極驅動器IC包括低源極和漏極阻抗,使得SiC MOSFET漏極可以由柵極精確控制。其次,最大限度地降低驅動器輸出阻抗對于允許SiC MOSFET達到最高自然dV/dt至關重要。SiC MOSFET的自然dV/dt限值與RLO+RGATE+RGI成反比。當RLO高于必要值時,SiC MOSFET的自然dV/dt限值降低。這使得器件更容易受到dV/dt引起的導通的影響,并限制了通過選擇RGATE可以實現的dVDS/dt控制量。圖38所示的NCP51705 VDS波形揭示了改變RGATE即可實現的高度dVDS/dt控制。對于RGATE=1Ω,dVDS/dt=72V/ns。將RGATE從1Ω增加到15Ω會使dVDS/dt從72V/ns降低到68V/ns。這表明,如果需要,可以使用高得多的RGATE來逐步降低dVDS/dt。

圖38.NCP51705 VDS上升沿,可變柵極電阻

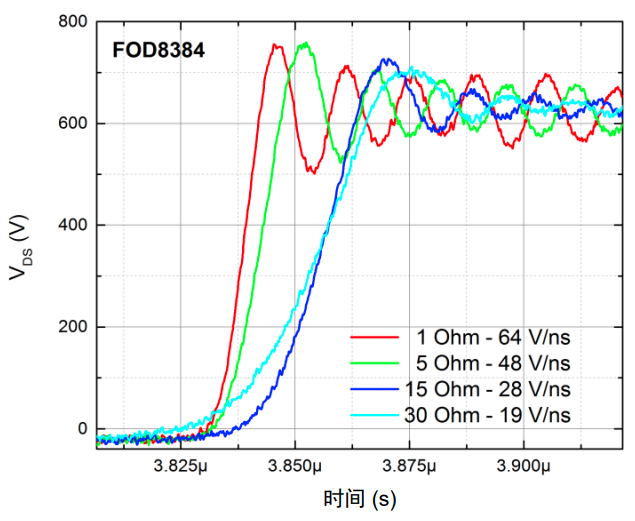

使用FOD8384光耦合器柵極驅動器完成了相同的實驗。從圖39所示的波形中發現,RGATE從1Ω變成15Ω導致dVDS/dt速率變化超過2:1。由于FOD8384驅動器輸出阻抗更高,dVDS/dt控制更受RGATE較小變化的影響。此外請注意,NCP51705的dVDS/dt上升相對而言更為線性。

圖39.FOD8384 VDS上升沿,可變柵極電阻

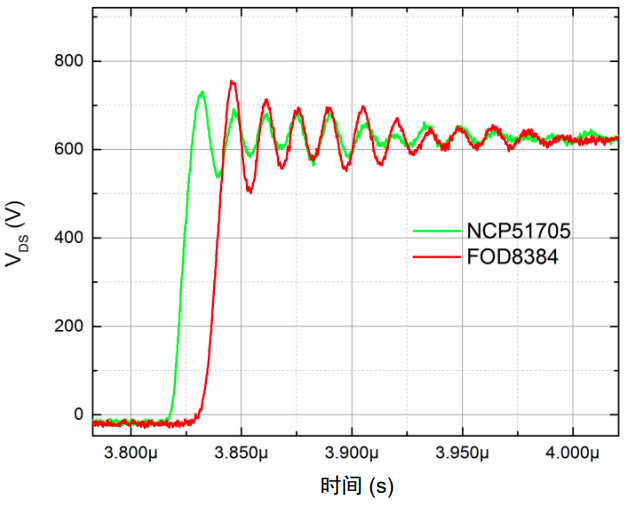

圖40所示的波形比較了在RGATE=1Ω的情況下,從?5V

圖40.VDS上升沿比較,1Ω柵極電阻

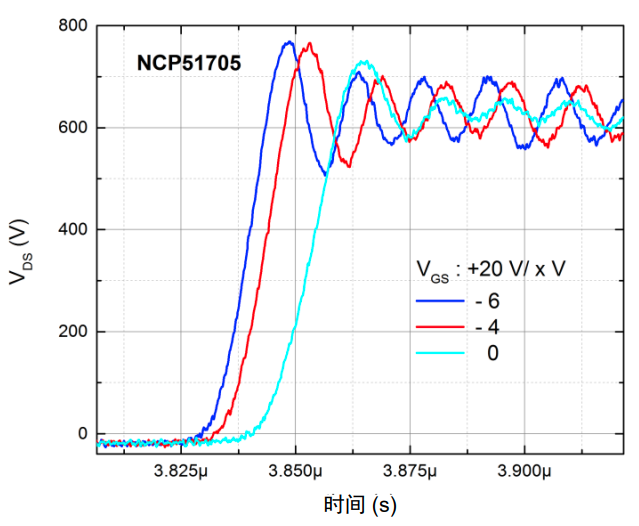

NCP51705實現dVDS/dt控制的另一種方式是通過改變VEE的負振幅電平。這可以通過根據表3配置VEESET引腳或使用施加到VEE的外部負 DC 電源來實現。圖 41 中的波形顯示了當VEE在?6V

圖41.NCP51705 VDS上升沿,可變VEE

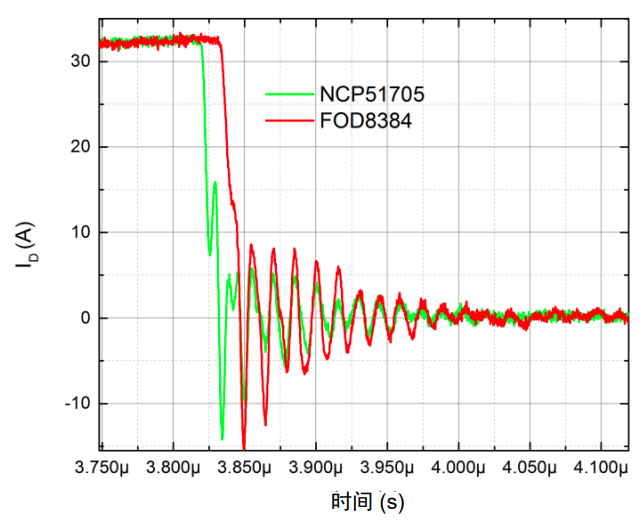

圖42所示的漏極電流測量是使用Pearson電流探頭進行的。NCP51705電流在dID/dt=3.2A/ns時下降,但與FOD8384驅動電路相比,表現出的振鈴較少。NCP51705更快的dID/dt與圖37所示的VGS下降沿波形密切相關。

圖42.ID下降沿比較

雙脈沖測試方法是傳統上用于表征分立功率半導體器件的動態開關性能的測試程序。由于在導通和關斷期間可以精確控制施加的VDS和初始ID,該測量技術已被證明是表征箝位電感開關應用電路中柵極驅動器IC性能的可靠方法。

結論

本文重點介紹了在設計高性能柵極驅動電路時必須考慮的SiC MOSFET的一些特性。對于柵極驅動來說,與SiC MOSFET相關的低gm或不那么大的跨導 特性尤其棘手。通用低邊柵極驅動器經常被使用,但缺乏高效可靠地驅動SiC MOSFET的必要功能。SiC MOSFET 在市場中的廣泛采用在某種程度上與其易用性有關。NCP51705為設計人員提供了一種簡單、高性能、高速的解決方案,用于高效可靠地驅動SiC MOSFET。

點個星標,茫茫人海也能一眼看到我

原文標題:SiC MOSFET的封裝、系統性能和應用

文章出處:【微信公眾號:安森美】歡迎添加關注!文章轉載請注明出處。

-

安森美

+關注

關注

32文章

1768瀏覽量

92797

原文標題:SiC MOSFET的封裝、系統性能和應用

文章出處:【微信號:onsemi-china,微信公眾號:安森美】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

2CD0210T12x0 SiC MOSFET驅動板:解鎖SiC碳化硅功率模塊的極限性能

SiC MOSFET 開關模塊RC緩沖吸收電路的參數優化設計

麥科信光隔離探頭在碳化硅(SiC)MOSFET動態測試中的應用

Nexperia推出采用X.PAK封裝的1200V SiC MOSFET

溝槽型SiC MOSFET的結構和應用

SiC MOSFET的參數特性

40mR/650V SiC 碳化硅MOSFET,替代30mR 超結MOSFET或者20-30mR的GaN!

國產SiC MOSFET,正在崛起

SiC MOSFET的性能優勢

什么是MOSFET柵極氧化層?如何測試SiC碳化硅MOSFET的柵氧可靠性?

SiC MOSFET模塊封裝技術及驅動設計

SiC MOSFET的封裝、系統性能和應用

SiC MOSFET的封裝、系統性能和應用

評論