當使用上拉電阻和下拉電阻時,你需要理解它們的具體應用和原理以確保正確配置引腳,維持電平狀態,并避免電路問題。以下是更詳細的解釋:

上拉電阻:

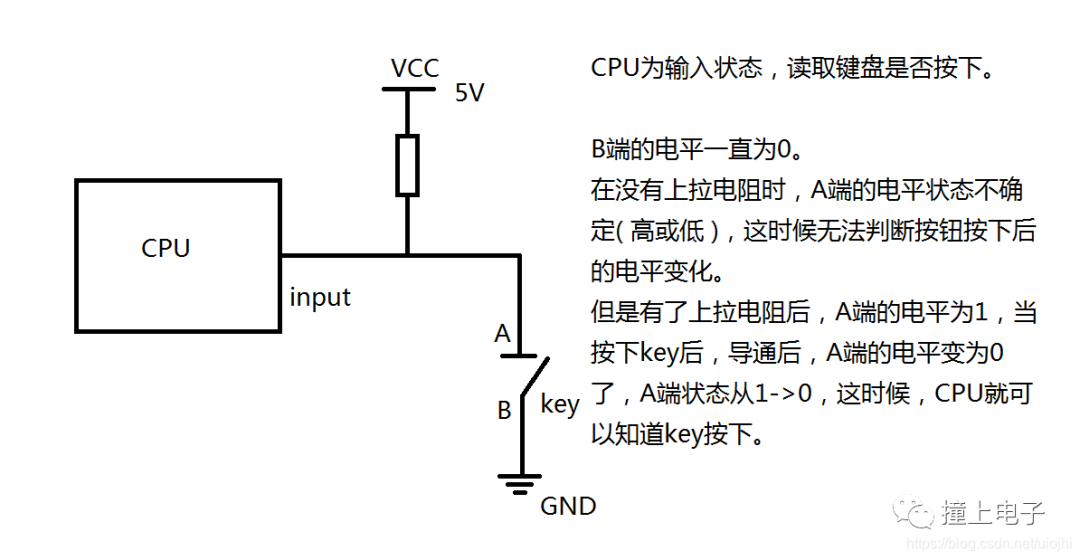

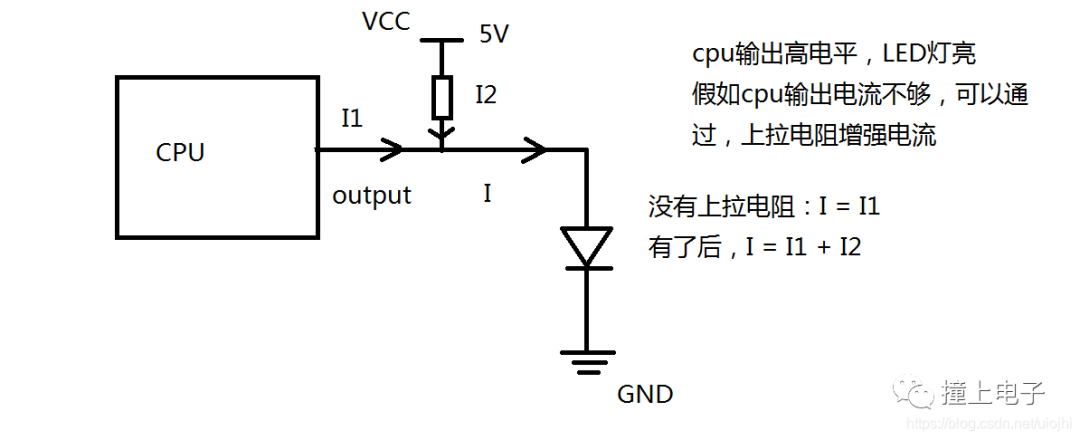

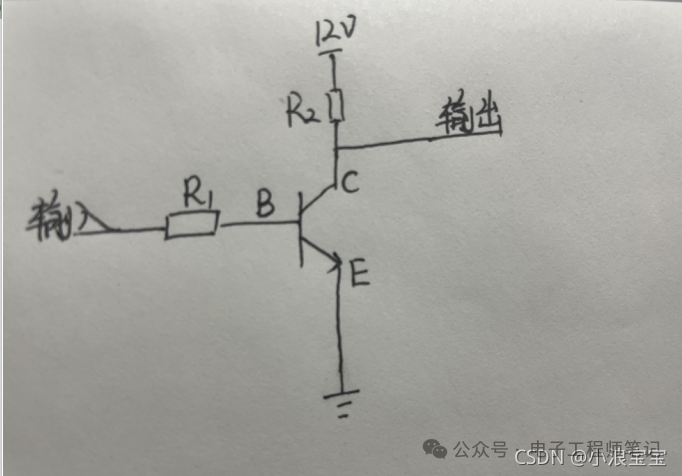

作用:上拉電阻用于保持引腳的電平在邏輯高("1")狀態。它的主要作用是確保在沒有外部輸入信號時,引腳的電平保持高電平狀態。原理:當引腳上拉電阻與電源電壓(通常是Vcc或3.3V)連接時,引腳通過上拉電阻與電源電壓相連。這使得引腳電平在沒有外部信號輸入時保持高電平。當外部事件將引腳連接到地(邏輯低)時,引腳的電平會變為低電平(邏輯"0")。應用:上拉電阻通常用于數字輸入引腳,如按鈕、開關或傳感器。例如,當按鈕未按下時,引腳保持在高電平狀態。當按鈕按下時,引腳的電平變為低電平,以表示按鈕已被按下。下拉電阻:

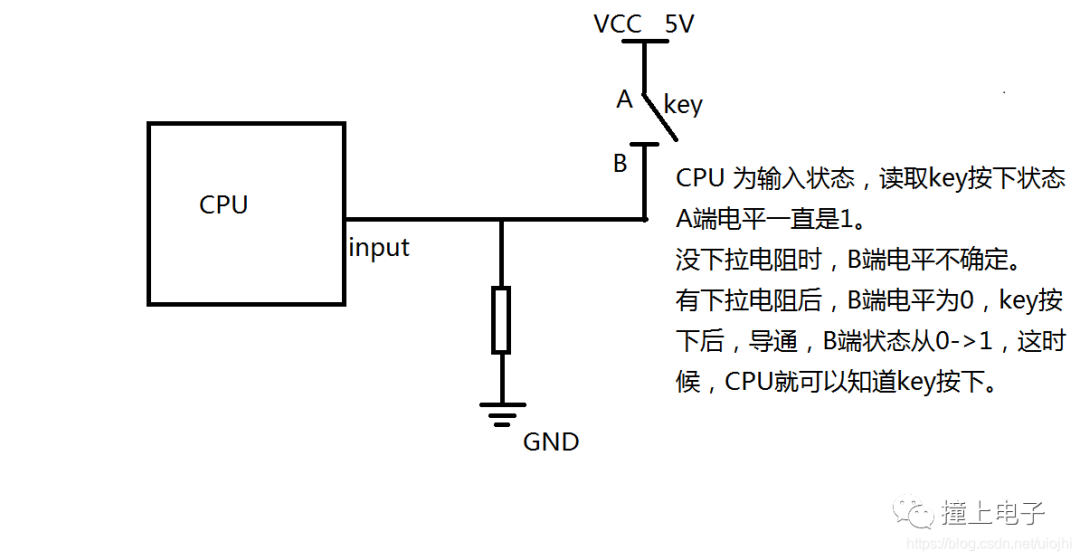

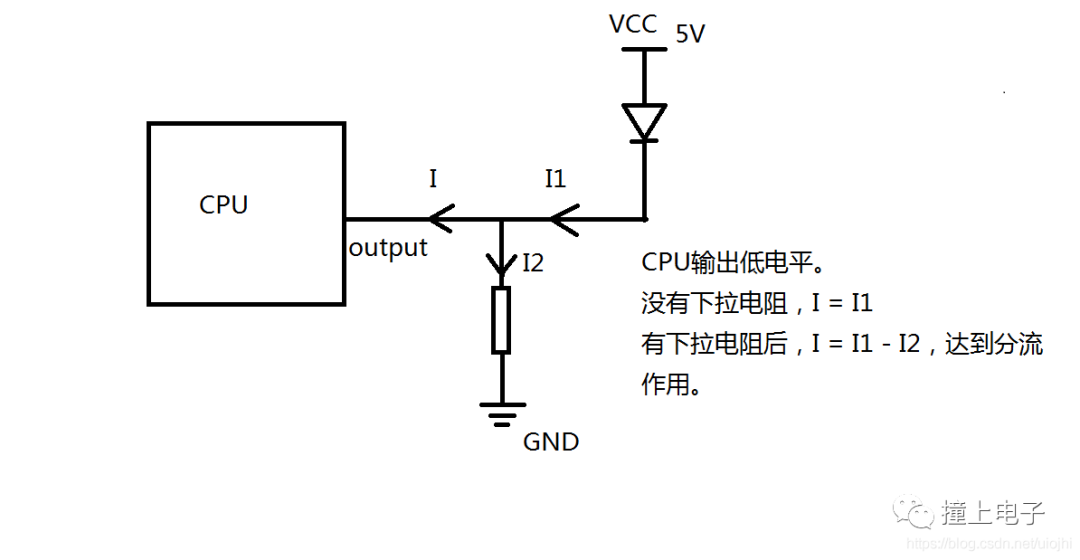

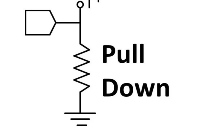

作用:下拉電阻用于保持引腳的電平在邏輯低("0")狀態。它的主要作用是確保在沒有外部輸入信號時,引腳的電平保持低電平狀態。原理:當引腳下拉電阻與地電壓(通常是GND或0V)連接時,引腳通過下拉電阻與地電壓相連。這使得引腳電平在沒有外部信號輸入時保持低電平。當外部事件將引腳連接到電源電壓(邏輯高)時,引腳的電平會變為高電平(邏輯"1")。應用:下拉電阻通常用于數字輸入引腳,如按鈕、開關或傳感器。例如,當按鈕未按下時,引腳保持在低電平狀態。當按鈕按下時,引腳的電平變為高電平,以表示按鈕已被按下。示例圖示1,上拉電阻輸入管腳

2,上拉電阻輸出管腳

3,下拉電阻輸入管腳

4,下拉電阻輸出管腳

-

電阻

+關注

關注

87文章

5606瀏覽量

174296 -

電路

+關注

關注

173文章

6022瀏覽量

174383 -

電平

+關注

關注

5文章

367瀏覽量

40398

發布評論請先 登錄

浮思特 | 電子電路下拉電阻詳解:原理、計算與應用指南

三極管下拉電阻設計:穩定與效率的平衡藝術

請問ADS1278配置管腳的上拉下拉電阻阻值選擇多少?

DAC101S101初次上電瞬間下拉電阻的開關是默認閉合的嗎?

當LMK00725的輸入為LVPECL電平時,由于芯片輸入管腳內部存在51KOhm上下拉,在芯片外部是否還需要增加上下拉偏置電阻呢?

【RS-485總線】詳解RS-485上下拉電阻的選擇

上下拉電阻的原理和4種應用

上下拉電阻的原理和4種應用

評論