思考

- L1 System memory 和 L1 Cache 是什么關(guān)系?

- L1 指令 cache 禁用時,指令 cache 就真的不會緩存了嗎?此時還會出現(xiàn)緩存不一致的情況嗎?

- L1 data cache 禁用時,L1 data cache 就真的不會緩存了嗎?此時還會出現(xiàn)緩存不一致的情況嗎?

- 在下電的時候,cache 有什么自動的行為?

- 有沒有 invalidate the entire data cache 的操作?那操作系統(tǒng)中的 invalidate_all_cache 是如何實現(xiàn)的?

- 什么是 Branch Target Buffer (BTB)?

- 什么是 Write streaming mode?軟件怎樣可以影響到 Write streaming mode 的行為?

- 有關(guān) cache 的 refill,如果 L1 MISS,那么 L1 會發(fā)生 refill 嗎

- Armv9 中的原子指令,和 cache 有啥關(guān)系?

- Exclusive 機制和 cache 有啥關(guān)系?

- 數(shù)據(jù)預取的作用是什么?數(shù)據(jù)預取有哪些指令?

- 執(zhí)行 memset() 函數(shù)清空一大塊內(nèi)存的時候,這些地址數(shù)據(jù)都會進 cache 嗎?

本節(jié)課我們將講述 Armv9 Cortex-A720 的 L1 System memory.

7 L1 instruction memory system

Cortex-A720 的 L1 指令內(nèi)存系統(tǒng)用于提取指令并預測分支。它包括 L1 指令緩存、L1 指令 Translation Lookaside Buffer(TLB)以及分支預測單元。L1 指令內(nèi)存系統(tǒng)向解碼器提供指令流。為了提高整體性能并降低功耗,L1 指令內(nèi)存系統(tǒng)使用動態(tài)分支預測和指令緩存。

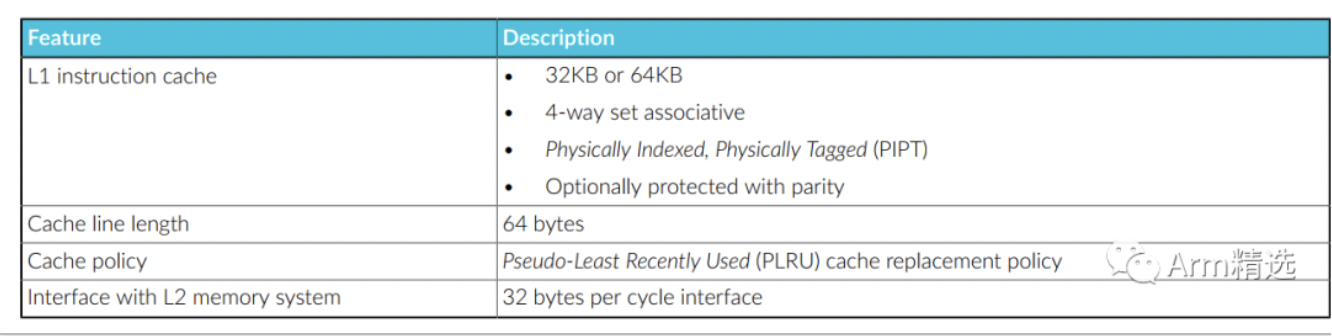

下圖顯示了 L1 指令內(nèi)存系統(tǒng)的特性。

L1 指令 TLB 也位于 L1 instruction memory system 中,它是內(nèi)存管理單元(MMU)的一部分。

7.1 L1 instruction cache behavior

在 reset 時,除非 core 電源模式初始化為 “Debug Recovery”,否則 L1 指令緩存將自動失效。在 Debug Recovery 模式下,L1 指令緩存不起作用。

L1 instruction cache 的禁用

禁用 L1 instruction cache 對 L1 指令緩存的操作沒有影響。即使在禁用狀態(tài)下,指令仍可以緩存在 L1 指令緩存中并從中提取。軟件必須考慮 Non-cacheable accesses 以確保正確的行為。

如果禁用了 L1 instruction cache,那么由指令提取引起的所有內(nèi)存訪問都將使用 Non-cacheable accesses。這意味著指令提取可能與同一核心或其他核心中的緩存不一致。軟件必須考慮這一點,執(zhí)行適當?shù)木彺婢S護操作。

L1 instruction 維護

緩存維護操作可以在任何時候發(fā)生,不管 L1 的狀態(tài)是禁用還是啟用。

7.2 L1 指令緩存的推測性內(nèi)存訪問

指令提取是推測性的,流水線中可能存在多個未完成的分支。

代碼流中的分支指令或異常可以導致流水線刷新,丟棄當前已提取的指令。

在指令提取時,具有 device memory 被視為 non-cacheable normal memory。為了防止指令提取,設備內(nèi)存頁面必須標記為翻譯表描述符屬性位 "Xecute Never"(XN)。設備和代碼地址空間必須在物理內(nèi)存映射中分離。這種分離防止了在禁用地址轉(zhuǎn)換時對讀取敏感設備的推測性提取。

如果啟用了 L1 指令緩存并且指令提取在 L1 指令緩存中未命中,那么它們?nèi)匀豢梢栽?L1 數(shù)據(jù)緩存中查找。

然而,無論數(shù)據(jù)緩存是否啟用,查找都不會導致 L1 數(shù)據(jù)緩存重新填充 (refill)。該行僅 refill allocated 在 L2 緩存中,前提是 L1 指令緩存已啟用。

7.3 程序流預測

Cortex-A720 核包含程序流預測硬件,也稱為分支預測。分支預測提高了整體性能并增強了功耗效率。

當內(nèi)存管理單元(MMU)啟用當前異常級別時,程序流預測被啟用。如果禁用程序流預測,那么所有已執(zhí)行的分支都會產(chǎn)生與清除流水線相關(guān)的動作。如果啟用程序流預測,則它會預測是否要執(zhí)行條件或無條件分支,如下所示:

- 對于條件分支,它預測是否要執(zhí)行分支以及分支轉(zhuǎn)到的地址,即分支目標地址。

- 對于無條件分支,它僅預測分支目標地址。

程序流預測硬件包含以下功能:

- 存儲以前已執(zhí)行分支的分支目標地址的分支目標緩沖器 Branch Target Buffer (BTB)

- 使用以前的分支歷史的分支預測(BP)預測器

- 返回堆棧,包括嵌套子例程返回地址

- 靜態(tài)分支預測器

- 間接分支預測器

預測和非預測指令

- 序流預測硬件預測所有分支指令,包括:

- 條件分支

- 無條件分支

- 返回指令

- 間接分支

以下指令不會被預測:

- 異常返回指令(包括 ERET,ERETAA,ERETAB)

- svc 指令

- hvc 指令

- smc 指令

返回棧

返回棧存儲了過程調(diào)用指令的返回地址。此地址應與這些指令由 Link 寄存器(X30)寫入的值相等。

以下任何指令都會導致壓棧:

- BL

- BLR

- BLRAA

- BLRAAZ

- BLRAB

- BLRABZ

以下任何指令都會導致出棧:

- RET

- RETAA

- RETAB

8 L1 data memory system

Cortex-A720 的 L1 數(shù)據(jù)內(nèi)存系統(tǒng)執(zhí)行加載和存儲指令。它處理內(nèi)存一致性請求以及特定指令,如原子操作、緩存維護操作和內(nèi)存標記指令。L1 數(shù)據(jù)內(nèi)存系統(tǒng)包括 L1 數(shù)據(jù)緩存和 L1 數(shù)據(jù) Translation Lookaside Buffer(TLB)。

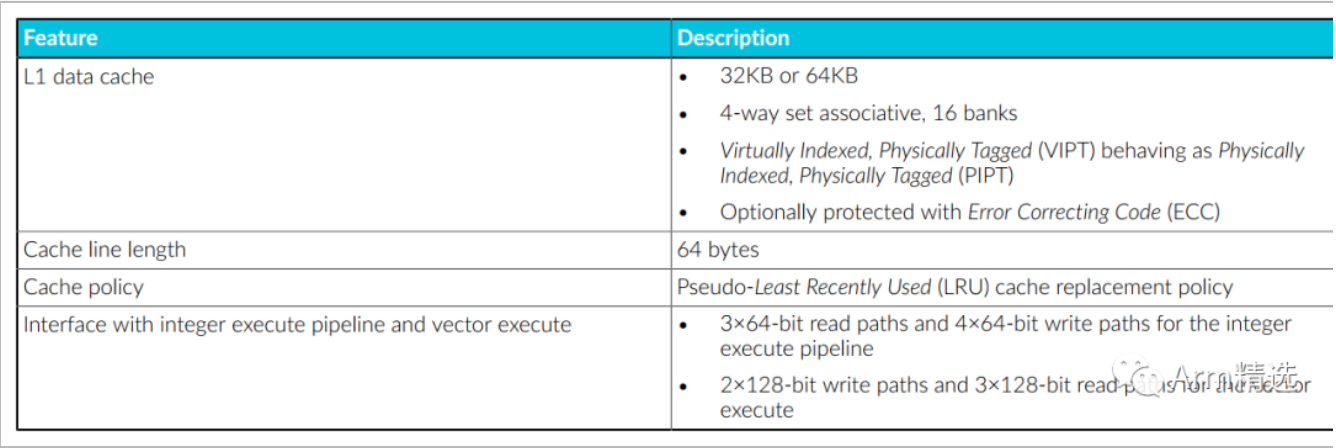

下表顯示了 L1 數(shù)據(jù)內(nèi)存系統(tǒng)的特性。

L1 數(shù)據(jù) TLB 也位于 L1 數(shù)據(jù)內(nèi)存系統(tǒng)中,它是內(nèi)存管理單元(MMU)的一部分。

8.1 L1 數(shù)據(jù)緩存行為

除非將核心電源模式初始化為 Debug 恢復模式,否則 L1 數(shù)據(jù)緩存將在重置時自動失效。在 Debug 恢復模式下,不能保證緩存是否正常運行,因此不應啟用。

沒有使整個 data cache 失效的操作 (invalidate the entire data cache)。如果軟件需要這個功能,那么必須通過循環(huán)執(zhí)行的單獨失效操作(通過 set/way 指令)來構(gòu)建它。DC CISW 指令執(zhí)行目標 set/way 的清除和失效操作。

禁用 data cache 行為

如果禁用數(shù)據(jù)緩存行為,則:

- 由于加載指令而導致的 L2 或 L3 緩存不會分配新的行。

- 對可緩存內(nèi)存的所有加載和存儲指令都視為 Non-cacheable。

- 數(shù)據(jù)緩存維護操作繼續(xù)正常執(zhí)行。

L1 數(shù)據(jù)緩存和 L2 緩存不能獨立禁用。當一個核心禁用 L1 數(shù)據(jù)緩存時,由該核心發(fā)出的可緩存內(nèi)存訪問將不再在 L1 或 L2 緩存中緩存。在多個 core 之間 cache 的維護操作,使用 Modified Exclusive Shared Invalid (MESI) 協(xié)議

緩存索引的確定方式意味著物理地址(PA)和組編號之間沒有直接關(guān)系。不能使用假設 PA 和組編號之間存在關(guān)系的有針對性的操作。要刷新整個緩存,必須根據(jù)緩存的 CCSIDR_EL1 描述的組和方式數(shù)量執(zhí)行組和方式維護操作。

8.2 Write streaming mode

Cortex-A720 核心支持 Write streaming mode,有時也稱為讀分配模式,對于 L1 和 L2 緩存都支持。

在讀不命中或?qū)懖幻袝r,會向 L1 或 L2 緩存分配緩存行。然而,寫入大塊數(shù)據(jù)可能會使緩存中充滿不必要的數(shù)據(jù)。這不僅會浪費電力,也會降低性能,因為整個線路會被后續(xù)寫入覆蓋(例如使用 memset() 或 memcpy())。在某些情況下,不需要在寫入時分配緩存行。例如,當執(zhí)行 C 標準庫的 memset() 函數(shù)來將大塊內(nèi)存清零為已知值時。

為了防止不必要的緩存行分配,內(nèi)存系統(tǒng)會檢測 core 何時寫入了一系列完整的緩存行。如果在可配置數(shù)量的連續(xù)線路填充上檢測到這種情況,那么它會切換到寫入流模式。

在寫入流模式下,加載操作行為與正常情況相同,仍然可能引起線路填充。

寫入仍然在緩存中查找,但如果未命中,則會寫入 L2 或 L3 緩存,而不會啟動線路填充 L1。

在內(nèi)存系統(tǒng)切換到寫入流模式之前,CHI 主控器或 AXI 主控器接口可能會觀察到超過指定數(shù)量的線路填充。

寫入流模式保持啟用,直到以下情況之一發(fā)生:

? 檢測到一個不是完整緩存行的可緩存寫入突發(fā)。

? 存在后續(xù)加載操作,其目標與未完成的寫入流相同。

當 Cortex-A720 核心切換到寫入流模式后,內(nèi)存系統(tǒng)會繼續(xù)監(jiān)視總線流量。當它觀察到一系列完整的緩存行寫入時,會向 L2 或 L3 緩存發(fā)出信號,以進入寫入流模式。

寫入流閾值定義了在存儲操作停止引起緩存分配之前,連續(xù)寫入的緩存行數(shù)量。您可以通過寫入寄存器 IMP_CPUECTLR_EL1 來配置每個緩存(L1、L2 和 L3)的寫入流閾值。

8.3 L1 數(shù)據(jù)內(nèi)存系統(tǒng)中的原子指令實現(xiàn)

Cortex-A720 核心支持 Arm v8.1-A 架構(gòu)中添加的原子指令。對可緩存內(nèi)存的原子指令可以作為近原子操作或遠原子操作執(zhí)行,默認情況下,Cortex-A720 核心將這些指令作為近原子操作執(zhí)行。

換句說法,可以根據(jù)系統(tǒng)行為對 IMP_CPUECTLR_EL1 進行編程,以便某些原子指令嘗試作為原子操作執(zhí)行。

當作為遠原子操作執(zhí)行時,原子操作傳遞給 interconnect 執(zhí)行操作。如果操作在集群內(nèi)的任何位置 hit,或者如果互連器不支持原子操作,則 L3 內(nèi)存系統(tǒng)執(zhí)行原子操作。如果該行不存在,則將其分配到 L3 緩存中。

Cortex-A720 核心支持對 device 或 non-cacheable 的原子操作,但這也依賴于互連器是否支持原子操作。如果在互連器不支持原子操作的情況下執(zhí)行此類原子操作指令,則會導致 abort。

8.4 內(nèi)部獨占監(jiān)視器

Cortex-A720 核心包括一個內(nèi)部獨占監(jiān)視器,具有 2 狀態(tài)(open 狀態(tài)和 exclusive 狀態(tài))的狀態(tài)機,用于管理 Load-Exclusive 和 Store-Exclusive 訪問以及 Clear-Exclusive(CLREX)指令。

您可以使用這些指令構(gòu)建信號量,確保不同進程在核心上運行時進行同步,以及確保使用相同的一致內(nèi)存位置的不同核心之間進行同步。Load-Exclusive 指令標記了一小塊內(nèi)存以進行獨占訪問。CTR_EL0 定義了標記塊的大小為 16 個字,即一個緩存行。

Load-Exclusive 或 Store-Exclusive 指令是以 LDX、LDAX、STX 或 STLX 開頭的指令。

8.5 數(shù)據(jù)預取

數(shù)據(jù)預取可以通過在需要數(shù)據(jù)之前獲取數(shù)據(jù)來提高執(zhí)行性能。

預加載指令

對于不能有效處理數(shù)據(jù)預取器的情況,Cortex-A720 核心支持 AArch64 預取內(nèi)存指令 PRFM。

這些指令向內(nèi)存系統(tǒng)發(fā)出信號,指定地址處的內(nèi)存訪問可能會很快發(fā)生。當內(nèi)存訪問發(fā)生時,內(nèi)存系統(tǒng)采取措施以減少內(nèi)存訪問的延遲。

PRFM 指令在緩存中執(zhí)行查找。如果未命中并且內(nèi)存訪問是對可緩存地址的,則開始線路填充。但是,PRFM 指令在開始線路填充時執(zhí)行結(jié)束,并且不會等到線路填充完成。

硬件數(shù)據(jù)預取器

加載 / 存儲單元包括硬件預取器引擎,負責生成針對 L1、L2 和 L3 緩存的預取。具體來說,L1 內(nèi)存子系統(tǒng)中的預取引擎針對 L1 和 L2 緩存。L2 內(nèi)存子系統(tǒng)中的預取引擎針對 L2 和 L3 緩存。加載端預取器使用虛擬地址(VA)和程序計數(shù)器(PC)。存儲端預取器僅使用虛擬地址(VA)。CPUECTLR 寄存器允許對預取器行為的某些方面進行控制。

數(shù)據(jù)緩存清零

在 Cortex-A720 核心中,Data Cache Zero by Virtual Address(DC ZVA)指令將對齊到 64 字節(jié)的內(nèi)存塊(64 字節(jié)對齊)設置為零。

-

緩沖器

+關(guān)注

關(guān)注

6文章

2037瀏覽量

46553 -

ARM芯片

+關(guān)注

關(guān)注

1文章

127瀏覽量

21924 -

MMU

+關(guān)注

關(guān)注

0文章

92瀏覽量

18628 -

Cortex-A7

+關(guān)注

關(guān)注

0文章

34瀏覽量

16758 -

cache技術(shù)

+關(guān)注

關(guān)注

0文章

41瀏覽量

1193

發(fā)布評論請先 登錄

Arm下一代指令架構(gòu)“Armv9”已經(jīng)問世

Armv9核心A710、A715和A510微架構(gòu)解讀

Armv9引入的MTE已成內(nèi)存安全的新防線

Armv9 system register class空間編碼簡析

Arm?Cortex-A720 Core技術(shù)參考手冊

Arm?Cortex-A720核心加密擴展技術(shù)參考手冊

重磅!Arm正式推出Armv9架構(gòu)

淺談ARM發(fā)布Armv9的三大改進

Arm推出三款基于Armv9架構(gòu)的全新CPU內(nèi)核

Arm微架構(gòu)之Armv9時代

Armv8架構(gòu)和Armv9架構(gòu)的區(qū)別分析

Armv9.2家族添新成員,全新Cortex-X4、A720和A520CPU內(nèi)核:性能再創(chuàng)新!

Armv9 Cortex-A720的L1 System memory簡析

Armv9 Cortex-A720的L1 System memory簡析

評論