請教關于LVDS阻抗匹配的問題 LVDS輸出阻抗偏大會出現什么情況?

LVDS(Low Voltage Differential Signaling)是差分信號傳輸技術,能夠提供較高的數據傳輸速率和較低的電磁干擾。LVDS信號在傳輸時,需要確保信號通過的阻抗匹配,以確保信號的完整性和穩定性。阻抗不匹配會導致信號反射、丟失和功耗增加等問題,影響信號傳輸的完整性和可靠性。

LVDS輸出阻抗偏大過高,會出現以下幾種情況:

1.信號反射

當LVDS信號通過傳輸線時,如果阻抗不匹配,很容易出現信號反射的情況。當信號反射回LVDS輸出端口時,會產生回波和噪聲,影響信號傳輸的完整性和可靠性。對于高速傳輸的LVDS信號,信號反射會更加明顯,因此需要更加嚴格的阻抗匹配。

2.功耗增加

當LVDS輸出端口阻抗偏大時,輸出驅動器需要產生更高的電壓來驅動傳輸線,以保證信號完整性。這會導致輸出驅動器消耗更多的功率,從而使得整個系統的功耗增加。這對于一些功耗敏感的應用來說是不可接受的。

3.信號丟失

當LVDS輸出端口阻抗偏大時,傳輸線上的信號會受到更強的信號衰減。如果衰減達到一定程度,接收端可能無法正確接收信號,導致信號丟失。這種情況下,需要降低LVDS輸出端口的阻抗以提高信號完整性和可靠性。

綜上所述,LVDS輸出阻抗偏大會導致信號反射、功耗增加和信號丟失等問題,影響傳輸線的完整性和可靠性。為避免這些問題的出現,需要進行嚴格的阻抗匹配,并在設計過程中注意輸出端口阻抗的控制。

-

lvds

+關注

關注

2文章

1110瀏覽量

67058 -

電磁干擾

+關注

關注

36文章

2378瀏覽量

106295 -

輸出阻抗

+關注

關注

1文章

104瀏覽量

12482

發布評論請先 登錄

如何確保模擬示波器的輸入阻抗匹配?

阻抗匹配中所說的50R,90R之類的阻抗是什么意思?

請問SN74CBT3251的輸出阻抗是多少?ADC10321的輸入阻抗是多少?

阻抗對音頻設備的影響 靜態阻抗和動態阻抗的區別

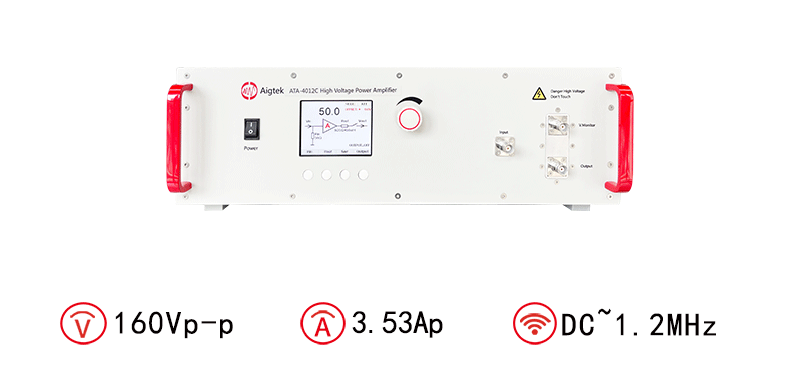

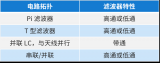

如何對一個濾波器進行50歐姆的阻抗匹配?

AD9854模塊輸出阻抗匹配

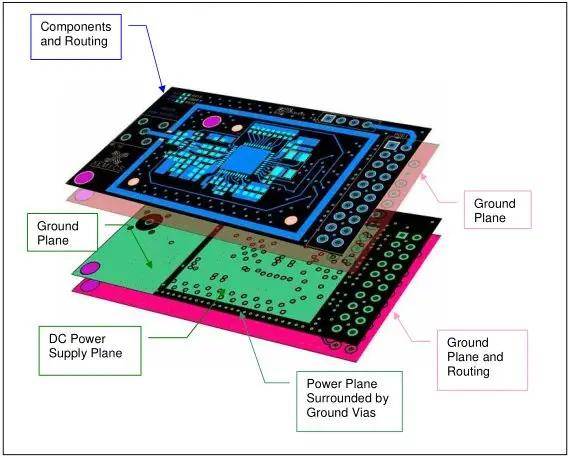

PCB阻抗匹配過孔的多個因素你知道哪些?

電路的阻抗如何匹配

阻抗匹配有煩惱?來嘮一嘮~

請教關于LVDS阻抗匹配的問題 LVDS輸出阻抗偏大會出現什么情況?

請教關于LVDS阻抗匹配的問題 LVDS輸出阻抗偏大會出現什么情況?

評論