Calibre ERC中有一項檢查會檢查Cell的輸入pin是否直接接到了電源地,為了防止產生這種問題,我們可以控制工具在設計中給那些輸入端接0/1的Pin上添加Tie low/high的Cell,而非直接接到電源地。

在布局完畢之后做如下操作即可:

setTieHiLoMode -reset

setTieHiLoMode -cell { TIEHI TIELO } -maxFanOut 16 -honorDontTouch false -createHierPort false

addTieHiLo -cell {TIEHI TIELO} -prefix LTIE

在添加了Tie high/low Cell之后,如何檢查設計中是否添加了Tie High/Low cell呢?可以用下面的命令:

dbGet [dbGet top.insts.name *LTIE* -p].name

如何得到庫中的Tie High/Low Cell名稱呢?

方法1:

一般Foundary都會提供Cell list以及每種Cell功能介紹的doc文檔,可以在里面查看,也可以在Cell LEF中找到:

MACRO TIELO

CLASS CORE ;

FOREIGN TIELO 0 0 ;

ORIGIN 0 0 ;

SIZE 1.32 BY 5.04 ;

SYMMETRY X Y ;

SITE tsm3site ;

…

END TIELO

MACRO TIEHI

CLASS CORE ;

FOREIGN TIEHI 0 0 ;

ORIGIN 0 0 ;

SIZE 1.32 BY 5.04 ;

SYMMETRY X Y ;

SITE tsm3site ;

…

END TIEHI

審核編輯:劉清

-

ERC

+關注

關注

0文章

7瀏覽量

10015 -

PIN管

+關注

關注

0文章

36瀏覽量

6554 -

電源地

+關注

關注

0文章

36瀏覽量

9937

原文標題:Innovus教程 - 如何添加、報告、驗證tie high/low cell

文章出處:【微信號:集成電路設計及EDA教程,微信公眾號:集成電路設計及EDA教程】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

A 1.9 GHz Low Noise Amplifier optimised for high IP3 using BFP540

請高手指點TEK示波器測試波形電壓時:High,Low,Max,Min的....

IAP程序只能跳轉到high地址或者low地址中的一個

High Speed/Low Loss, CAF Resis

A New High Gain Low Voltage 1.

TL4581,pdf(DUAL LOW-NOISE HIGH

TPS71710,pdf(Low Noise, High-B

TPS71715,pdf(Low Noise, High-B

Simple Low-Voltage High-Brightness (HB)-LED Solution for Li+ Battery-Operated Systems

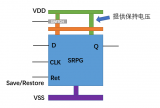

Low Power概念介紹<SRPG Cell>

Low Latency High Bandwidth Memory 數據表(Digest Edition)

Low Latency High Bandwidth Memory 數據表(Digest Edition)

MAX30009: Low-Power, High-Performance Bioimpedance Analog Front-End Data Sheet MAX30009: Low-Power, High-Performance Bioimpedance Analog Fro

如何添加、報告、驗證tie high/low cell?

如何添加、報告、驗證tie high/low cell?

評論