關于硅材料雜質濃度測試,經研究,參考肖特基二極管雜質濃度測試方案,兩者幾乎一致,因此,針對硅材料雜質濃度測試亦采用CV法測量,方案如下:

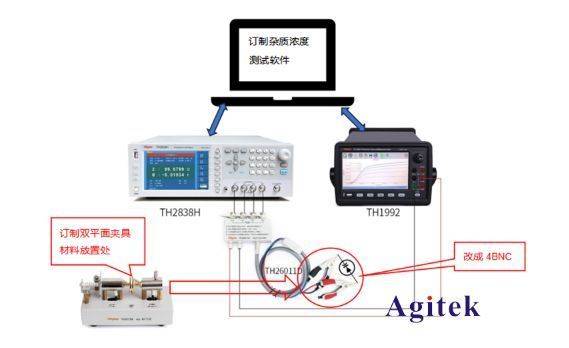

一、 方案配置

1、 TH2838系列LCR數字電橋(必選)

可選頻率20Hz-1MHz/2MHz,用于測試CV特性

2、 TH199X系列精密源/測量單元(SMU)(必選)

可選單/雙通道,電壓±63V/210V,6 1/2輸出/測量分辨率,最小輸出電壓分辨率100nV、電流10fA

3、 TH26011D直流隔離開爾文測試夾具(必選)

用于隔離直流電壓與LCR測試,如果測試片狀材料,需要改裝成4個BNC,以保證精度,直接用夾子測試材料電容誤差較大。

4、 TH26008A或TH26007型SMD測試夾具(可選)

若用于測試片狀材料,需用此夾具接觸材料,可選針狀測試端或訂制圓形測試端。

5、 訂制上位機軟件(可選)

此軟件主要用于采集CV數據,采集不同電壓下電容值,并根據下列參考資料部分公式直接計算出對應雜質濃度。

若不定制此上位機軟件,可自行采集數據并計算濃度。

方案結構示意圖

一、 參考資料:肖特基二極管雜質濃度相關知識

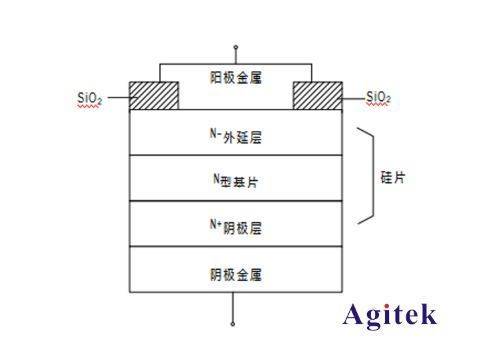

1、 肖特基二極管的構造

肖特基二極管是貴金屬(金、銀、鋁、鉑等)作為正極,以N型半導體為負極,利用兩者接觸面上形成的勢壘具有整流特性而制成的金屬-半導體器件。

構造:以重摻雜的N+為襯底,厚度為幾十微米,外延生長零點幾微米厚的N 型本征半導體作為工作層,在其上面再形成零點幾微米的二氧化硅絕緣層,光刻并腐蝕直徑為零點幾或幾十微米的小洞,再用金屬點接觸壓接一根金屬絲或在面接觸中淀積一層金屬和N型半導體形成金屬半導體結,在該點上鍍金形成正極,給另一面N+層鍍金形成負極,即可完成管芯,如圖4.1所示。

圖4.1 肖特基二極管結構圖

1、 肖特基勢壘的形成原理

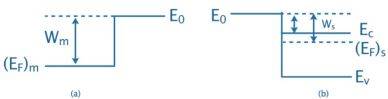

(1) 功函數與電子親和能金屬的功函數Wm

金屬的功函數表示一個起始能量等于費米能級的電子,由金屬內部逸出到表面外的真空中所需的最小能量,功函數的大小標志電子在金屬中被束縛的強弱。

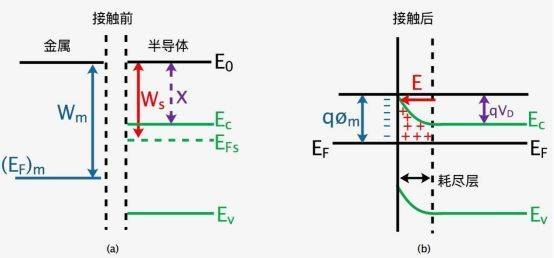

如圖4.2(a)所示。

為真空中電子的能量,又稱為真空能級。

圖4.2 (a)金屬功函數; (b)半導體功函數半導體的功函數Ws

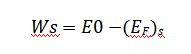

半導體功函數半導體的功函數Ws

E0與費米能級之差稱為半導體的功函數,如圖4.2(b)所示。

和金屬不同,半導體的費米能級

隨摻雜類型和摻雜濃度而變化,所以Ws也與雜質類型和雜質濃度有關。

定義真空能級E0和導帶底能量Ec的能量差為電子親合能,用χ表示,即

電子親合能表示使半導體導帶底的電子逸出體外所需的最小能量。

(2) 肖特基勢壘結的形成

功函數不同的兩種晶體形成接觸時,由于費米能級EF不在同一水平上,將有電子自 EF 較高一側的表面流向對方表面,在兩側晶體的表面形成電荷層,從而在兩者之間形成電勢差,直到費米能級達到同一水平時,將不再有電子流流動。這時在兩者之間形成的電勢差稱為接觸電勢差。接觸電勢差正好補償兩者費米能級之差。

假定有一塊金屬和一塊n型半導體,并假定金屬的功函數大于半導體的功函數,即:Wm>Ws。由于它們有相同的真空能級,所以在接觸前,半導體的費米能級EFs高于金屬的費米能級EFm,且EFs-EFm=Wm-Ws,如圖4.3(a)所示。

圖4.3 (a)金半接觸前能級; (b)金半接觸后能級變化。

當金屬和N型半導體接觸時,由于半導體的費米能級高于金屬中的費米能級,

電子流從半導體一側向金屬一側擴散,同時也存在金屬中的少數能量大的電子跳到半導體中的熱電子發射;顯然,擴散運動占據明顯優勢,于是界面上的金屬形成電子堆積,在半導體中出現帶正電的耗盡層,如圖 4.3(b)所示。界面上形成由半導體指向金屬的內建電場,它是阻止電子向金屬一側擴散的,而對熱電子發射則沒有影響。隨著擴散過程的繼續,內建電場增強,擴散運動削弱。在某一耗盡層厚度下,擴散和熱電子發射處于平衡狀態。宏觀上耗盡層穩定,兩邊的電子數也穩定。界面上就形成一個對半導體一側電子的穩定高度勢壘:

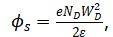

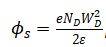

它和耗盡層厚度有如下關系:

其中

為N的摻雜濃度,在勢壘區,??????為耗盡層寬度。電子濃度比體內小的多,是一個高阻區域,稱為阻擋層,界面處的勢壘通常稱為肖特基勢壘。耗盡層和電子堆積區域稱為金屬-半導體結。

2、 肖特基二極管的整流特性

如果給金屬-半導體結加上偏壓,則根據偏壓方向不同,其導電特性也不同。

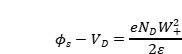

零偏壓:保持前述勢壘狀態,如圖4.4(a)所示。

正偏:金屬一側接正極,半導體一側接負極,如圖4.4(b)所示。

外加電場與內建電場方向相反,內建電場被削弱,耗盡層變薄,肖特基勢壘高度降低,使擴散運動增強,半導體一側的電子大量的源源不斷的流向金屬一側造成與偏壓方向一致的電流,金屬-半導體結呈正向導電特性,且外加電壓越大,導電性越好,其關系為:

反偏:金屬一側接負極,半導體一側接正極,如圖4.4(c)所示。

外加電場與內建電場方向一致,耗盡層變厚,擴散趨勢削弱,熱電子發射占優勢,但這部分電子數量較少,不會使發射電流增大。在反偏電壓的規定范圍內,只有很小的反向電流。在反偏情況下,肖特基勢壘呈大電阻特性。反偏電壓過大時,則導致反向擊穿。

圖4.4 肖特基二極管在不同偏壓下的情況

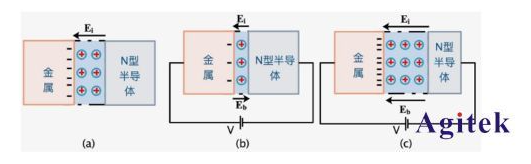

肖特基二極管與 PN 結二極管具有類似的整流特性,硅肖特基二極管的反向飽和電流比典型的PN結二極管的反向飽和電流大103~108倍,如圖4.5所示,具體的數值取決于肖特基勢壘高度。較小的肖特基勢壘高度導致反向飽和電流較大,較大的反向飽和電流意味著產生相同的正向電流,肖特基二極管的正向導通電壓較小,這個特性使得肖特基二極管更適合應用于低壓以及大電流領域。

圖4.5 肖特基二極管伏安特性曲線

1、 勢壘電容

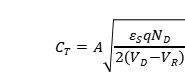

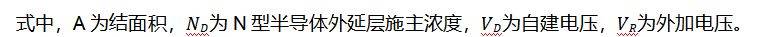

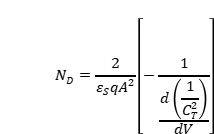

耗盡層的厚度隨外加電壓的變化直接反映著耗盡層具有一定的電容。耗盡層的兩個界面可以看作平行板電容器的兩個面板,假如半導體內雜質濃度是均勻的且不存在氧化層,則在耗盡層的區域內,其電容為:

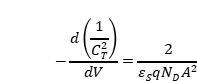

如果半導體均勻摻雜,則 為一條直線,通過直線的斜率可求得半導體的摻雜濃度為:

審核編輯:湯梓紅

-

二極管

+關注

關注

148文章

10038瀏覽量

170226 -

測試

+關注

關注

8文章

5623瀏覽量

128266 -

肖特基二極管

+關注

關注

5文章

978瀏覽量

35735 -

硅材料

+關注

關注

0文章

47瀏覽量

8224

發布評論請先 登錄

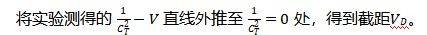

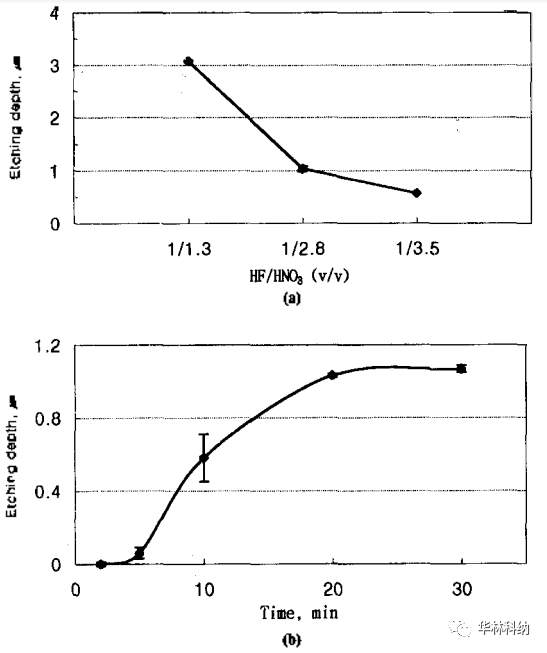

如何減少硅晶片表面上的金屬雜質

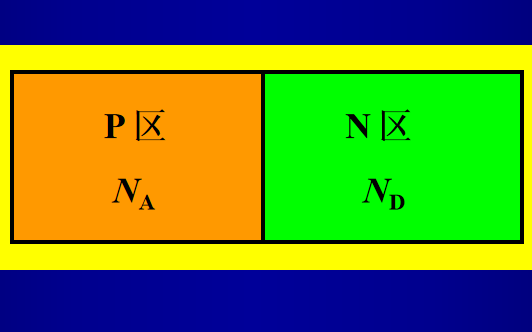

不同濃度和溫度的硫酸對材料的腐蝕差別較大

氧氣 濃度 方案開發

模擬電子復習總結(一):半導體二極管

數字源表應用方案的半導體霍爾效應測試

吉時利源表在寬禁帶材料測試的應用方案

為什么硅仍然主導著集成電路產業?

微電子器件教程之PN結的詳細資料說明

用蝕刻法測定硅晶片表面的金屬雜質

利用蝕刻法消除硅晶片表面金屬雜質?

硅材料雜質濃度測試方案

硅材料雜質濃度測試方案

評論